电能的高功率运用可以使家用电器本钱下降并保护环境。绝大多数的家用电器,如电冰箱、洗衣机、烘干机、洗碗机以及空调,都是由电机驱动的。这些设备一般包含了电源、电机、电机操控电路和机械体系。咱们可以选用多种办法来改进体系功率。包含:

1. 坚持电压稳定;

2. 尽量削减相位不平衡;

3. 坚持功率因数稳定;

4. 坚持杰出的电源质量;

5. 选用可调式速度驱动或双速电机;

6. 操控好温度;

7. 匹配电机运转速度。

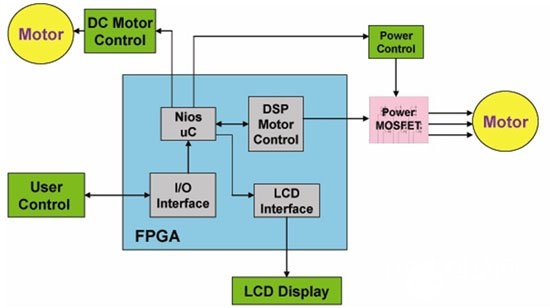

运用数字电路或FPGA操控模仿电机电路将使体系本钱和功耗大大下降。选用FPGA除了可以节能之外,还可以将嵌入式数字信号处理(DSP)、微操控器、I/O接口等功用整合到一同,然后完成完好的家电规划。

脉冲宽度调制

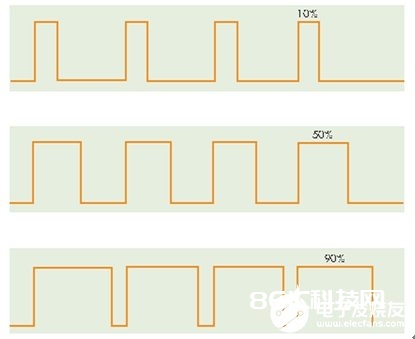

用数字办法操控模仿电机电路的一种典型办法是选用脉冲宽度调制(PWM)。此刻方波的时刻周期是稳定的,而接通时刻(TON)即信号坚持高电平的时刻可以被改动或调制。因而,信号的占空比或均匀直流电平是改动的。借助于数字体系的支撑,PWM已经成为操控模仿电路的一种极好办法。图1便是数字脉冲的接通时刻改动的比如。

运用实例包含电压调整,即通过改动占空比将输出电压操控到所要求的电平。另一个比如是功率发送,这时的均匀发送功率是调制占空比的函数。PWM的完成取决于详细的运用办法,关于简略的电压调整,可以运用CPLD(例如Altera MAX II)完成,而关于需求运用内部DSP模块的杂乱操控算法,可以运用低本钱的FPGA(例如Altera Cyclone III)完成。

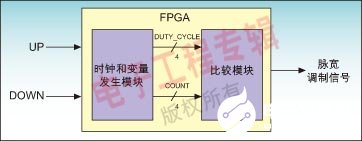

图2是PWM的根本方框图,而图3则是一个驱动模仿电机接口电路的调制输出。UP和DOWN输入信号被用来调整输出信号的占空比,它们可以由微操控器产生。第一个模块运用一切MAX II器材中都有的UFM振荡器来产生两个频率不同的时钟。来自该模块的4位输出信号DUTY_CYCLE的添加或下降取决于UP或DOWN信号的证明。第二个4位输出信号COUNT以第一个模块中产生的较高时钟频率接连添加。该信号与第二个模块中相同频率的DUTY_CYCLE信号进行比较。比较的结果是分配到终究输出信号PWM的单个位。信号DUTY_CYCLE是一个4位的变量,因而输出信号的占空比具有16个不同的取值。在本规划完成中,输入UP的优先级要高于DOWN。因而,假如两个信号一起为高电平,输出信号将被视作占空比的添加。

图1:PWM波形示例。

图2:PWM根本框图

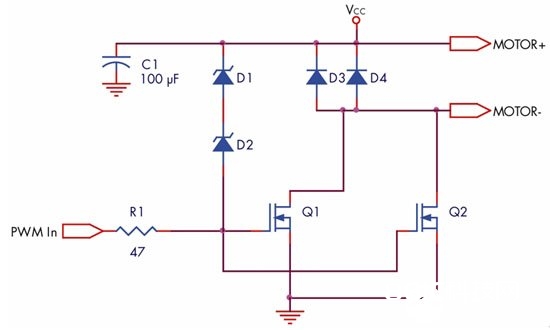

图3:电机模仿驱动电路。

DSP电机操控

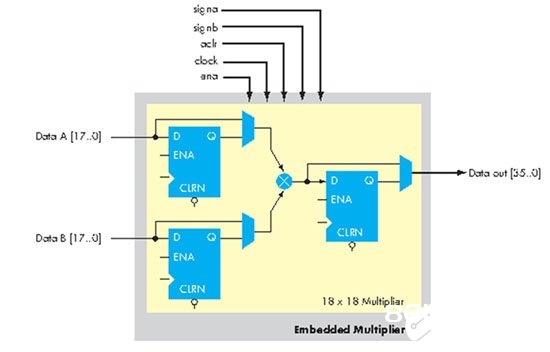

Cyclone III FPGAs中的嵌入式DSP功用块(如图4所示)为规划更杂乱和功率更高的电机操控体系供给了要害要素。依据FPGA的DSP芯片使得大型家电制造商可以下降研制时刻和本钱,并且在未来晋级时不需求从头布板。FPGA所供给的可重装备解决方案可用来完成DSP运用以及满意高DSP吞吐率的需求。因为FPGA可以完成硬件重装备,因而能完成完好的硬件定制并完成杂乱的电机操控DSP功用。因而,由FPGA完成的DSP体系可以具有定制的架构、定制的总线结构、定制的存储器、定制的硬件加速器模块和各种很多的乘法-累加(MAC)块。

图4:FPGA中的嵌入式DSP块。

为了使沟通电机的运转功率更高,内部永久磁铁的方位与施加的沟通电压频率同步至关重要。可以运用传感器来检测磁转子的方位,并以此调理电压的频率。该办法类似于伺服操控锁相环(PLL)体系,只不过这儿选用DSP来完成这一使命。

图5:典型的运用方框图。

新一代的家电将需求更杂乱的电路来监控电机和整个体系的运转状况。运用FPGA中DSP功用的先进操控算法规划将可以完成比特别运用规范产品(ASSP)或特别运用集成电路(ASIC)更灵敏的体系。因为FPGA可以编程,因而可以依据市场需求的改动修正或参加新功用。假如参加一个以太网IP核,FPGA还可以通过IP网络与外界进行通讯,然后答应体系安排好体系产生毛病之前的保护和服务作业,并完成用户家庭网络的无线通信。

微操控器

新一代家电设备将通过微操控器完成用户接口和其他的功用操控。具有嵌入式微操控器的FPGA供给了一个集成的解决方案,无需别的再配外部专用处理器。嵌入式处理器规划师面对的首要应战是怎么挑选处理器,使之最合适详细的运用但又不过分地糟蹋或献身功用。像Altera的Nios? II软件处理器就答应规划师创立抱负的硬件(CPU,外设以及定制硬件加速器)、软件(存储器接口)和本钱的归纳环境,以满意每一个新的家电规划阶段的共同需求。

此外,Altera公司的 Nios II C-to-Hardware Acceleration (C2H) Compiler可以协助那些对FPGA比较生疏的工程师运用ANSI C替代原理图或RTL输入进行嵌入式处理器体系规划。

LCD面板接口

FPGA中内置的LVDS I/O接口答应直接耦合并驱动简略文本或视频质量的显示器面板,因而在体系中可以很简单规划出用于显示器的视频处理器和守时操控器。一片Cyclone III FPGA可以被规划和装备成为一个驱动典型液晶显示器(LCD)接口的图画增强引擎。而预先通过优化的IP MegaCore??能,例如去交错、量化、滤波以及颜色空间转换器,都可以处理来自任何源设备的视频输入,并输出到象具有网络功用的电冰箱上的视频显示器这样的LCD面板上。

本文小结

低本钱的FPGA或CPLD可以协助家电规划师运用灵敏的、集成有DSP算法的单片集成解决方案完成节能的电机操控。此外,这些具有内置软处理器的可编程器件还有助于简化设备的用户接口规划。运用这些器材还可以使新一代的家电设备可以与用户的家庭网络进行无线通信。

责任编辑;gt