MIL—STD—1553B(以下简称1553B)总线规范是美国于20世纪70年代提出的飞机内部电子体系联网规范,因为具有可靠性高、实时性好、运用灵敏等长处,广泛使用在军用有人和无人机中。我国于1987年建立了与1553B相应的国家军用规范《数字式时分制指令/呼应型多路传输数据总线》(GJB 289-1987),并于1997年对原规范进行扩大和修订(GJB 289A-1997),一向沿用至今。

FlexRay总线是一款新式时刻总线,具有高速率,时刻确定性,信道容错冗余功用,彻底满意新式分布式结构飞翔仿真计算机内部总线数据通讯需求。依据分布式结构飞翔仿真计算机对1553B通讯接口的需求,本文规划了依据FlexRay总线的飞翔仿真计算机1553B接口单元。

1 分布式飞翔仿真计算机简介

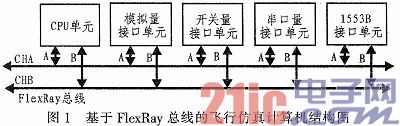

典型的依据FlexRay总线的分布式飞翔仿真计算机由中央处理单元、串口量单元、模仿量单元、开关量单元及1553B接口单元组成。其间CPU单元是分布式飞翔仿真计算机的中心主控单元,其功用首要经过CAN总线接纳其他四个功用模块的上行数据,经操控律解算及逻辑办理后,将数据下行传输给各功用板。其结构图如图1所示,本文规划研讨一种依据FlexRay新式总线的1553B接口单元。

2 1553B节点硬件电路规划

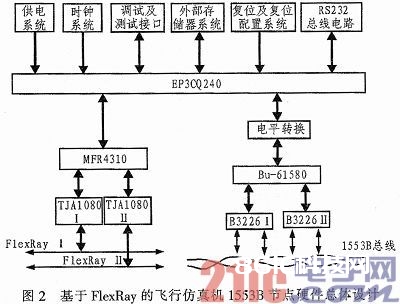

依据FlexRay总线的飞翔仿真计算机1553B接口单元以FPGA作为主操控芯片,FPGA选用Altera公司Cvclone III系列的EP3C25Q240芯片。挑选该芯片的原因是因为FPGA硬件衔接灵敏,编写程序简略,且该芯片IO口资源丰富。

图2为依据FlexRay的飞翔仿真机1553B节点硬件总体规划。如图2所示,本规划选用BU-61580S3作为1553B主控芯片。BU-61580集成了双通道1553B信号的收/发器,内部有4K字的RAM用于1553B音讯存储,简化了用户程序规划。选用B3226作为1553B总线变压器,B3226首要功用是将1553B总线电平规范转化为TTL电平。而因为BU-61580的IO接口为5 V电平接口,而EP3CQ240的IO电平为3.3 V,故在FPGA与BU-61580之间需求经过一个电平转化模块进行电平匹配。

FlexRay节点有3种架构方法,别离为微处理器(MCU)+通讯操控器(CC)+总线驱动器(BD),微处理器+总线驱动器,微处理器3种。其间前两种架构现已完结,本规划选用微处

理器+通讯操控器+总线收发器的架构形式,其间通讯操控器选用MFR4310,它是飞思卡尔半导体公司推出的一款面向轿车的FlexRay设备,它的物理层通道有两个独立的发送/接纳通道,每个通道的传输速率可达10Mbit/s。通讯操控器两路通道的总线操控器选用TJA1080,TJA1080是恩智浦半导体公司推出的FlexRay收发器,它供给了1Mbit/s到10Mbit /s的传输率,可以装备成自动星型或许节点收发器。

为了确保体系正确无误运转及调试便利考虑,本规划还增加了供电体系、时钟体系、调试及测验接口、外部存储器体系、复位及复位装备体系、RS232总线电路6个模块作为辅佐功用。

2.1 1553B接口规划

2.1. 1 BU-61580与FPGA接口规划

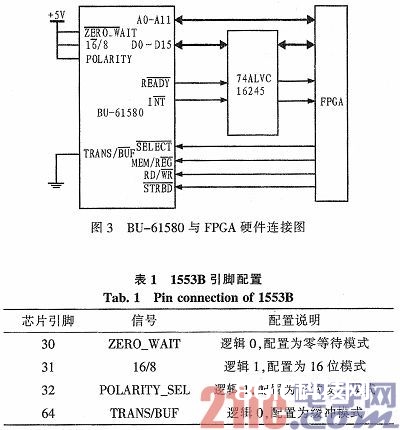

BU-61580芯片为DDC公司运用最为广泛的操控芯片,具有多种操作形式,如通明形式、缓冲形式,本规划选用缓冲形式。如图3所示,经过将BU-61580的16/8引脚衔接至VCC,TRANSPARENT/BUFFERED、ZEROWAIT引脚衔接至GND,将BU-61580的作业形式设置为16位零等候缓冲形式,具体管脚装备见表1。

因为BU-61580的输入高电平阈值为2 V,输出高电平为5 V,而FPGA的作业电平为3.3 V,故FPGA的输出电平可用于驱动BU-61580,但BU-61580输出信号至FPGA过程中需求外加电平转化芯片。本规划选用的是SN74ALVC164245作为电平转化芯片,该芯片具有十六位电平转化长度。

BU-61580的时钟选用外部有源晶振,CLOCK引脚接16M有源晶振,依据GJB 289A-97要求,晶振的长时刻安稳性为0.1%,短期安稳性为0.01%。

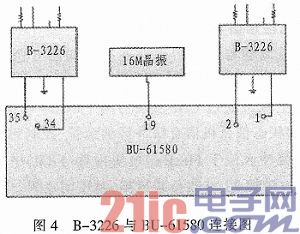

2.1. 2 BU-61580与收发器接口规划

本规划选用的阻隔变压器芯片为B-3226,该芯片每个通道通讯可以到达1 Mbit/s,可以供给很好的通讯带宽,具有强壮的容错传输功用。耦合变压器与BU-61580硬件衔接如图4所示,BU-61580内部具有两路1553B收发器别离与阻隔变压器B-3226相连,B-3226将1553B电平逻辑转化为TTL逻辑电平,从而将处理后的信号送入BU-61580内部的收发器中,完结一次1553B接纳通讯。

2.2 FlexRay接口规划

本规划中,挑选MFR4310作为FlexRay总线主控芯片,该芯片具有两条通讯通道,每条通道速率可装备为:2.5,5,8,10Mbit/s;TJA1080作为独立的FlexRay收发器,具有低电磁辐射特性。外界传感器数据经过1553B总线传输至本板卡后,经FPGA预处理后经过FlexRay总线发送至CPU单元中,然后完结一次CPU读取外部传感器信息。

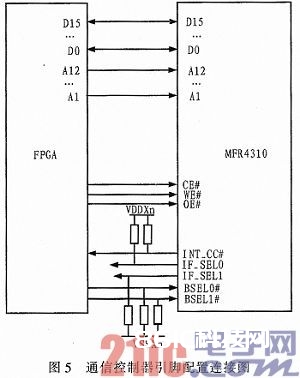

2.2.1 通讯操控器与处理器接口规划

MFR4310与处理器具有3种衔接形式,别离为:异步存储器接口(AMI)、MPC接口、HCS12接口。硬件规划经过装备IF_SEL0和IF_SEL1两个引脚来挑选哪种接口形式。依照飞思卡尔官方引荐衔接电路,MPC接口首要为MFR4310与PowerPC处理所规划的接口,而HCS12接口首要为MFR4310与HCS12系列处理器所规划的接口,因为本规划选用的处理器为FPGA,故选用异步存储器接口。具体硬件衔接图如图5所示,AMI接口将通讯操控器装备为异步存储器从设备,从而可以与多种处理器进行数据交互,在AMI接口形式下,处理器经过操控CE#、0E#、WE#等信号完结与MFR4310数据交换。

图5为通讯操控器引脚装备衔接图,如图5所示,因为本规划选用AMI形式,需求设置IF_SEL[0:1]为{2’h10},该值可经过将IF_SEL0引脚下拉、IF_SEL1引脚上拉来完结。

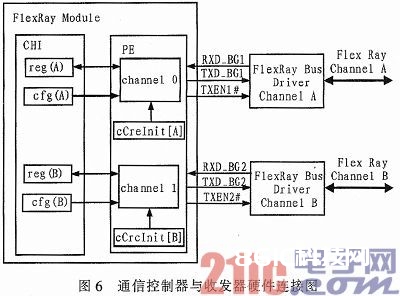

2.2.2 通讯操控器与收发器接口规划

通讯操控器与收发器硬件衔接图如图6所示,FlexRay模块内部首要由由操控主机接口(CHI)与协议引擎(PE)等部分组成,主机可经过CHI模块拜访FlexRay功用模块的装备、操控和状况信息机音讯缓冲区的装备、操控和状况信息。这些音讯缓冲区坐落FlexRay模块内存(FRM)中,用于存储发送和接纳的帧头、有用负载数据、时序音讯等。而PE模块有TxA和TxB两个发送单元及RxA、RxB两个接纳单元,别离用于两个FlexRay通道发送和接纳帧信息。

通讯操控器经过信号引脚TxD、RXD、TXEN与总线收发器进行衔接,正常高速通讯形式下,当MFR4310通讯操控器的TJXEN [1:2]#引脚为高电平时,TJA1080的发送使能引脚TXEN有用,这时TJA1080的TXD输入引脚把从通讯操控器TXD_BG[1:2]引脚输入的数字位流,转化成相应的模仿总线信号再输出到FlexRay总线上;一起,TJA1080将FlexRay总线上的模仿总线信号转化成相应的数字位流,从TJA1080的RXD引脚输送到通讯操控器MFR310的RXD_BG2引脚上,完结总线与MFR4310通讯操控器的数据通讯。

3 软件驱动程序规划

3.1 1553B总线软件驱动规划

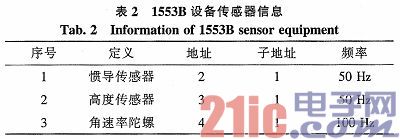

本设备1553B协议芯片作业于BC形式下,而其他传感器模块作业于RT形式,即:本设备作业于主形式,传感器设备作业于从形式。当本设备需求传感器信息时,发送数据恳求帧,传感器形式将相应数据发送至本设备。本设备要求承受的传感器信息频率如表2所示。

从上表可看出,各个传感器的频率并非彻底一致。而BU-61580可以经过运用巨细周期来支撑多种频率的数据传输,在自动发送形式下,可以经过设置小周期为100 Hz、大周期为50 Hz,从而完结数据帧按要求的速率进行传输。

BU-61580的程序初始化流程如下所示:

1)将该模块设置为增强型BC形式,设置中止屏蔽寄存器,初始化装备寄存器、时刻标签寄存器;

2)初始化内存空间,为3个传感器分配内存初始地址及内存空间;

3)装备复位寄存器,发动BC。

3.2 FlexRay总线软件驱动规划

本设备接纳外部传感器信息,经过内部总线FlexRay发送至CPU板卡中,从而完结一次总线收发。FlexRay总线收发首要由总线操控器完结的,FlexRay总线操控器具体的通讯流程如下。

总线操控器MFR4310的信息缓冲器(Message Buffer,简称MB)是用来存储帧数据、装备、操控、状况数据的结构。当总线通讯时,MB是暂时存储数据的物理介质,当数据发送时,使用程序将数据存储于MB中,当周期轮转至发送时槽时,硬件节点将数据从MB中取出发送至另一接纳节点的相应MB中,完结一次数据通讯。

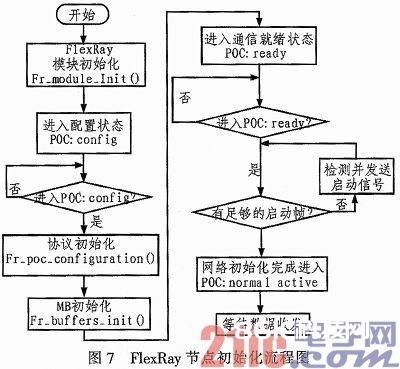

MB在运用前,有必要经过初始化。FlexRay网络节点的初始化包含初始化节点本身和初始化网络。初始化本身由3步组成:

1)初始化FlexRay模块。完结FlexRay模块基地址存储映射,重启FlexRay通讯操控器,进入装备状况(POC:config),由函数Fr_module_init()完结;

2)FlexRay协议初始化。该步界说相关数据结构,完结网络装备和节点通讯任务分配,由函数Fr_poc_configuration()完结;

3)音讯缓冲器初始化。初始化FlexRay通讯操控器音讯缓冲器与通讯数据报文的对应联系,由函数Fr_buffers_init()完结。节点初始化本身完结后就进入通讯安排妥当状况(PO C:ready)。之后,进入初始化网络阶段,这阶段经过发送发动帧完结网络发动。依据表2的装备,节点ECU1和ECU2别离在时槽1和时槽4发送发动信息帧,一起侦听网络中的发动帧个数,直到网络中有满意的发动帧发动网络,数据在正常自动状况下(POC:nomal active)完结节点间通讯。具体流程图如图7所示。

4 总线网络通讯测验与成果剖析

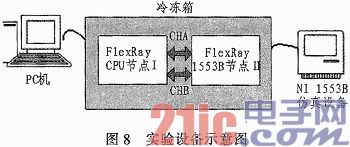

最终对所规划的依据FlexRay总线的1553B节点进行测验,其测验渠道如图8所示。经过NI测验设备对传感器数据进行模仿,从而发生一组传感器数据,完结1553B总线通讯。

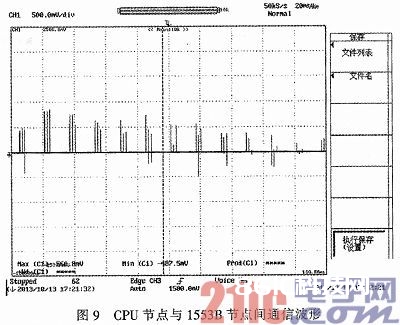

体系上电后,CPU板卡及1553B板卡进行寄存器装备,完结本身初始化,然后CPU板卡作为冷发动节点发送10个冷发动帧至FlexRay总线上,进行总线组网,1553B板卡接纳到冷发动帧后,当即参加FlexRay总线集群中,至此,总线预备完结。待总线预备完结,节点间开端通讯,图9为CPU节点与1553B节点间通讯波形。

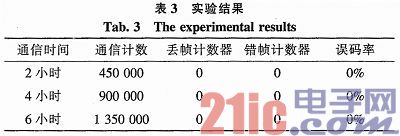

如图9所示,FlexRay通讯周期为16 ms,静态时隙长度为50μs,将CPU板卡与1553B板卡进行通讯试验6小时,试验成果如表3所示。

经过试验成果可以得出,节点规划合理,本设备可精确接纳外界1553B传感器信息,并进行数据处理功用,可为新式分布式无人机飞翔仿真计算机供给1553B通讯接口。

5 结束语

1553B作为航空内部电子体系联网规范,可规划为飞翔仿真计算机的外部总线,而FlexRay为新式总线,具有速率快,多冗余等特色,可规划为飞翔仿真计算机外部总线。这两种总线各展所长,为飞翔仿真计算机供给了快速、安稳的数据传输链路。本文规划了依据FPGA的1553B总线节点,经过与NI设备进行数据通讯,成果正确,可以满意飞翔仿真计

算机数据链路要求,为今后先进飞翔仿真计算机新式总线FlexRay与1553B总线的使用打下了根底。