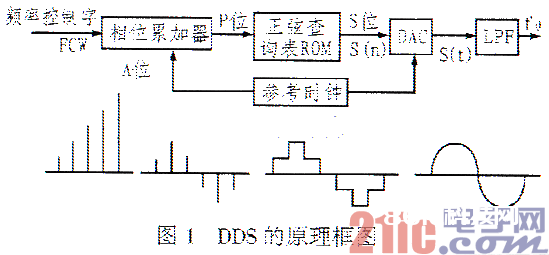

摘要:在剖析了DDS根本原理以及AD9858根本特色的基础上,介绍了AD9858的送数办法及单片机接口程序。给出了运用AD9858内部寄存器来完结跳频时刻小于50ns的4频点快速跳频的详细办法。 要害词:DDS;AD9858;快速跳频 在电子体系中,常常需求运用频率组成技能来完结跳频源规划。频率组成指对一个高安稳的参阅频率进行各种技能处理,以生成一系列安稳的频率输出。现在运用最广的是锁相环(PLL)频率组成技能,它是经过改动PLL中的分频比N来完结跳频的,但PLL无法防止环路确定时刻缩短与频率分辨率进步及杂散减小之间的对立,因而很难一起满意高速跳频和细步长、低杂散的要求。直接数字频率组成(DDS)是一种新的频率组成技能。它具有频率分辨率高、频率切换快、频率切换时相位接连等长处,因而被广泛运用于雷达跳频、通讯、电子对抗等体系中。 1 DDS根本原理 DDS的原理框图如图1所示。相位累加器在A位频率操控字FCW的操控下,以参阅时钟频率fc为采样率来发生待组成信号相位的数字线性序列,然后将其高P位作为地址码,经过查询正弦表ROM发生S位对应信号波形的数字序列S(n),再由数模转化器将其转化为阶梯模仿电压波形,最终由低通滤波器LPF滑润为正弦波输出。

频率操控字FCW和时钟频率fc一起决议了DDS的输出信号频率fo 。其联系是: 输出频率:f0=FCW fc/2A 频率的分辨率为:fo=fc/2A 2 AD9858的特色及送数办法 AD9858的主要特色: ● 具有1千兆次/秒的采样速率; ● 具有高达2GHz的输入时钟(经过2分频); ● 集成有10位D/A转化器; ● 内含32位可编程频率寄存器; ● 带有8位并行及SPI串行操控接口; ● 具有主动频率扫描功用; ● 内带4个频率寄存器; ● 选用3.3V低电源供电; ● 电荷泵独立供电电压可达5V; ● 集成有2GHz混频器。 因为DDS发生的频率是由频率操控字FCW操控的,改动相应频率的操控字即可取得所需频率。因而DDS的送数办法是完结DDS跳频源的要害之一。其内部结构框图如图2所示。 AD9858有并行和串行两种送数办法。数据从用户传输到DDS器材中心需求两个过程。在写操作时,不管是用并行送数办法仍是串行送数办法,用户都要首先将数据写入I/O缓冲器。只要当数据从I/O缓冲器锁入存储寄存器,DDS的中心才接收到数据。在AD9858中,触发FUD脚或许改动预编程的Profile都可以使I/O缓冲器中的数据进入DDS的中心存储寄存器。 (1)并行送数形式时,体系应激活八个双向数据口(D0~D7)、六个地址输进口(ADDR5~ADDR0)、一个读口(RD)和一个写口(WR),寄存器的挑选由寄存器图供给的地址决议。读写功用由RD和WR脉冲触发操控,但这两个功用不能一起起作用。读写的数据可经过D0~D7脚传输。 图2 (2)串行送数形式包含两个阶段。第一阶段由一个8位的指令周期构成。最高位是标志位,用于确定是读操作仍是写操作,低六位是串行送数方针寄存器的地址。第二阶段便是送数据给寄存器。 许多时分DDS都要求快速跳频,而频率的快速改动则要求寄存器的频率操控字快速更新,因而,一般都要求DDS选用并行送数。相对于ADI公司以往的DDS芯片而言AD9858的优势在于它具有四个频率寄存器及四个相位补偿寄存器这使得它可以便利快速的发生跳频信号以及四相码编码调制信号并且它转化时刻极短。这是因为跳频的频率操控字现已送入DDS中心寄存器中的四组操控寄存器,频点之间的挑选是依托外部挑选信号PS1和PS0来完结的。 3 依据AD9858的快速跳频规划 3.1 跳频电路 送数及四频点的切换经过单片机来完结。89C51单片机可在5V电压下作业,但试验证明,3.3V供电时,89C51单片机的作业也是彻底正常的,选用单片机和DDS芯片AD9858规划的跳频原理图如图3。 3.2 软件程序规划 依据AD9858的时序特色,可将单片机的P1.0和P1.1别离与RD和WR相连。这样,编程时就可以对频率操控字和相位补偿字的地址列表作如下详细设置: FTW0_1 EQU 00101011B FTW0_2 EQU 00101111B FTW0_3 EQU 00110011B FTW0_4 EQU 00110111B POW0_1 EQU 00111011B POW0_2 EQU 00111111B 最低两位别离是RD和WR,初始化时将其均置为高位。三到六位才是送数的地址。一个频点的送数程序如下: MOV P3, 40H MOV P1, #FTW0_1 CLR WR_ SETB WR_ SETB FUD CLR FUD MOV P3, 40H MOV P1, #FTW0_2 CLR WR_ SETB WR_ SETB FUD CLR FUD MOV P3,40H MOV P1, #FTW0_3 CLR WR_ SETB WR_ SETB FUD CLR FUD MOV P3, #40H MOV P1, #FTW0_4 CLR WR_ SETB WR_ SETB FUD CLR FUD ; MOV P3, #00H MOV P1, #POW0_1 CLR WR_ SETB WR_ SETB FUD CLR FUD ; MOV P3, #00H MOV P1, #POW0_2 CLR WR_ SETB WR_ SETB FUD CLR FUD 规划时,应先将8位频率操控字送入单片机的P3口,再将这8位的地址送入P1口。因为送8位地址的一起也将WR置为高位。因而,将WR置低就可将8位操控字和6位地址送入DDS缓冲器。因为频率的更新只需FUD一个上升沿,所以将FUD置为高位就可将8位数据送入指定的频率寄存器(初始化已将FUD置为低位),最终再将FUD置为低位,认为后边的频率更新设置上升沿做准备。 经过一个简略的程序可将一个频点的操控字送入DDS的存储寄存器。再经过相同的地址列表和送数办法就可将所需求的其它三个频点送入DDS的存储寄存器。这样,经过外部挑选信号PS1和PS0就可以快速在这四个频点间进行切换。 因为AD9858内部的频率寄存器有限,因而,在跳频的频点较多时,每次跳频都需求改动频率操控字。DDS的实践跳频时刻包含送数和内部切换时刻。假如运用内部寄存器经过PS1和PS0来操控切换频率,则跳频时刻只要内部切换时刻,所以,这种跳频是适当快的。 图3 4 试验及测验成果 试验标明(该试验选用400MHz低相噪时钟):AD9858的内部切换时刻仅为纳秒级。该试验运用周期逻辑电平操控 PS1和PS0,并经过对PS1和PS0信号的挑选来完结频率的切换。最终运用高频示波器来测验跳频时刻。 笔者进行的第一个试验是将一个寄存器的频点FCW设为00000000H(0MHz),另一个寄存器的频点FCW设为20000000H(125MHz)。测验成果为:从0MHz跳频到125MHz所用的时刻为17.6ns。 第二个试验是将一个寄存器的频点FCW设为19999999H(100MHz),另一寄存器的频点FCW设为20000000H(125MHz)。测验成果为:从100MHz跳频到125MHz所用的时刻为33.6ns。 5 定论 从两次测验的成果来看运用AD9858内部寄存器来完结快速跳频是彻底可行的。因为测验过程中存在数据传输推迟,PS0和PS1操控电平的上升沿,所以测验存在必定的差错,实践跳频时刻应比测验成果更短一些。 因为AD9858内部只要四个频率寄存器,所以跳频的点有限。在跳频点不需求许多、跳频时刻要求很短时,此办法优越性非常显着。