0 导言

跟着遥感技术的开展,遥感图画的分辨率也越来越高。飞行器上搭载的遥感成像设备也从曩昔的低分辨率向现在的高分辨率在改变。遥感成像设备分辨率进步的一起,也对飞行器的数据下传链路提出了更高的带宽要求。而相应的地上数据承受设备,也需求具有对高速实时数据的存储和处理才能。同样在测验设备方面,为了对大容量存储设备进行高速数据的传输测验,相应的地上检测设备也应该具有高速数据的输出功用。因而,急需开宣布具有高速实时数据接纳和高速数据输出功用的高速数据收集存储体系。

从现在此类体系的技术指标来看,往往只能到达100Mbps到150Mbps的数据接纳和数据输出功用。而依据现在的运用需求来看,高速数据流的数据传输速率往往在200Mbps以上乃至到达300Mbps。关于这种高速数据流,现在的体系就难以接连无错的进行存储和处理,往往会因为数据传输速率超越体系能处理的极限,导致呈现丢掉数据或许体系功用不正常,状况不稳定等问题。

本文中介绍的高速数据收集存储体系的规划方针便是对传输速率最高为300Mbps的数据流进行无错接纳存储,并能完结最高为300Mbps的高速数据流输出,以便于对大容量存储设备进行检测。

1 体系全体介绍

高速数据收集存储体系是在32位的核算机体系上完结的,数据传输也是运用32位,33MHz的PCI总线来完结。数据存储是运用两块SATA接口的硬盘组成的RAID0磁盘阵列来完结的。整个体系的中心是数据传输接口卡,它完结外部数据到核算机内存的传输。然后运转的驱动程序再将内存中的数据存储到硬盘上。因而,整个体系的规划也就分为数据传输接口卡的规划和驱动及运用程序规划两大部分。

2 数据传输接口卡规划

数据传输接口卡从功用上分为PCI总线接口,存储缓冲区,间断模块,传输操控模块,缓冲区操控以及DMA操控六个模块,如图2-1中所示。当作业于数据输入时,传输操控模块依据缓冲区状况发动传输,传输进程中缓冲区操控模块将数据读出送到PCI总线上,DMA操控模块操控着PCI总线上数据传输的进行。传输完毕今后,间断模块宣布间断信号提示驱动程序对传输到内存中的数据进行处理。下面首要介绍PCI总线接口模块,DMA操控模块,存储缓冲区模块以及传输操控模块几个中心模块的规划。 500)this.style.width=500;” border=”0″ />

500)this.style.width=500;” border=”0″ />

2.1 PCI总线接口模块的规划

PCI总线接口模块完结的作业首要是PCI总线指令的解码,地址以及数据的锁存。完结PCI接口常用的办法是选用现成的PCI总线接口协议芯片(PLX905X系列等),如文献[2]中数据收集板的规划便是选用的这种办法。可是因为这些协议芯片往往不是针对空间运用而专门开发的,从可靠性方面考虑,不能选用这种规划方案。在本方案中,整个接口的规划是在运用Xilinx公司供给的LogiCORE PCI v3.0的IP核(IP Core)的基础上完结的。LogiCORE PCI v3.0是Xilinx公司供给的用于PCI总线接口规划的IP 核,在它的基础上能够依据实践运用的需求很便利的定制和完结PCI总线接口。因为IP 核本身完结了装备空间以及总线指令的解码和地址的锁存,所以规划者只需求专心于PCI传输状况机和本地操控信号的规划。选用这种完结方法尽管比直接运用PCI接口专用芯片更为杂乱,可是整个规划能够集成于一片高可靠性的FPGA之中,然后有用的进步了整个规划的可靠性。

2.2 DMA操控模块的规划

为了满意高速率数据传输的需求,并且在数据传输的一起不占用CPU,所以有必要选用DMA的方法来传输数据。因为PCI总线上的DMA传输是经过PCI设备本身的DMA操控功用来完结的,而不是依托总线上独自的DMA操控设备来完结,所以在规划时有必要完结DMA操控模块。DMA操控模块在数据传输周期宣布操控指令以及更新地址。其间传输地址操控能够依靠一组传输地址寄存器来完结,而传输的操控能够经过PCI传输状况机给出的信号来发生操控信号。

2.3 存储缓冲区模块的规划

为了确保数据的接连不间断传输,每次传输只传输半个缓冲区的数据,而外部数据总是在两个半区之间切换贮存,因而不会形成数据的丢掉和不接连。

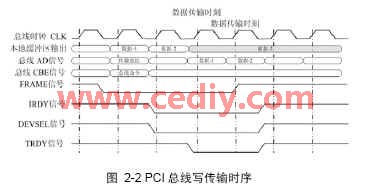

一个典型的PCI总线上的写数据传输时序如图2-2中所示。首要用于传输的数据有必要要提早从本地的缓冲区中读出,然后呈现在总线AD信号线上,当IRDY信号和TRDY信号一起有用时(为低电平时),被方针设备获取。当传输完毕时,最终一个从本地缓冲区中预读出的数据(如图中暗影的数据3),并不会被传输到方针设备。而本地的缓冲区操控模块会以为数据现已传输,这时假如不采纳办法就会导致数据丢掉。

500)this.style.width=500;” border=”0″ />

500)this.style.width=500;” border=”0″ />

在传输完毕的时分,PCI总线传输状况时机切换到备份数据的状况,在这个状况下,缓冲区的操控模块会检测是否存在现已读出而未传输的数据,假如存在这样的状况,操控模块则采纳办法避免数据丢掉。关于双口RAM这种存储结构而言,数据读出今后,只需没有在同一地址写入数据,那么数据是不会丢掉的,因而要完结前面的功用只需求简略的修正一下读指针现在指向的地址就能够完结。

2.4 传输操控模块的规划

传输操控模块的中心是一个传输操控状况机。它经过检测存储缓冲区的状况,来操控传输的进行。当输入缓冲区中数据存储满或输出缓冲区空今后,主动恳求一次数据传输,由此确保数据流的接连。

3 驱动与运用程序的开发

驱动程序的开发是选用标准的WDM(Windows Driver Model)设备驱动程序模型,运用DriverStudio的驱动程序开发工具包来进行开发的。关于WDM的驱动程序模型,限于篇幅的原因就不作具体的介绍。

一个典型的数据传输进程是这样进行的。首要驱动程序完结设备的初始化,如在内存中拓荒缓冲区,硬件设备的初始化等等。完结初始化今后硬件就处于等候传输的状况。当用户经过运用程序宣布传输数据的指令今后,驱动程序处理这一恳求,并对硬件宣布指令开端数据传输。因为数据传输的时刻或许比较长,所以运用程序选用多线程的规划,传输线程会等候驱动程序在传输完毕时宣布的信号,而一起运用程序还能完结与用户的交互作业。当传输完毕后,驱动程序向硬件写入间断指令,间断传输,并向运用程序宣布传输完毕信号。驱动程序对运用程序的通讯是经过创立Win32事情来完结通讯的。

4 规划的仿真和验证

为了验证规划的正确性,首要需求对规划进行逻辑功用仿真。为了验证规划是否能正常的作业在PCI总线上,那么就需求仿真PCI总线上的各种总线业务,验证规划是否能呼应各种总线指令。仿真是在Xilinx公司供给的PCI总线接口仿真实例的基础上完结的。依照PCI总线标准规划了一个简略的总线裁定器,用来仿真主设备请求总线占用的进程。此外还规划了一个PCI总线上的从设备,用来仿真主设备与从设备之间的数据传输进程。此外还仿真了总线上对设备的主动装备进程。经过调查仿真波形图,发现规划彻底满意PCI总线的数据传输标准,并且数据传输的成果正确。

在仿真验证正确的基础上,将规划完结于Xilinx公司型号为virtexII2v1000-fg456-5的FPGA中。将数据接口卡装置于测验核算机上,运用数据接口卡的自回路数据传输功用以及单向输入输出功用,对体系进行了验证和功用测验,成果如表格1中所示。

从成果能够看出,当输入输出速率保持在160Mbps以下时,能够确保本身回路数据传输无错进行,可是当速率进步到200Mbps今后,传输就会呈现数据丢掉,导致接纳的数据与发送数据不一致。因而,为了确保数据的无错传输,本身回路数据传输测验速率应该不高于160Mbps。

500)this.style.width=500;” border=”0″ />

500)this.style.width=500;” border=”0″ />

单向输入输出测验时,当输入速率或许输出速率小于300Mbps,体系的功用是彻底正确的,而当作业于400Mbps的时分,则会呈现数据丢掉的状况。与本身回路传输测验的数据比较能够看出,当在本身回路数据传输测验速率为200Mbps的时分,因为此刻体系接纳和输出一起进行,一起分时运用总线,此刻相当于独自接纳或许独自输出测验时400Mbps的传输速率。两次测验成果的一致性也阐明晰测验的可靠性。

5 结语

经过对体系的测验验证,证明晰本规划能够彻底满意高速实时数据流对数据收集存储体系的要求。为了便利今后进一步的作业,在测验时也对缓冲区巨细和传输速率之间的联系进行了简略的测验。将缓冲区巨细从8KB改变到16KB今后,传输速率仅仅略微有些进步,对功用的改进非常不显着。成果阐明简略的扩展硬件缓冲区并不会带来数据传输速率的显着改观,一起还会占用FPGA内部名贵的RAM资源。究其原因在于,数据传输速率首要遭到32位/33MHzPCI总线带宽本身的约束,以及硬盘读写的峰值速率的约束,而并不是缓冲区巨细的影响。能够预见假如选用64位/66MHz的PCI总线并选用更多的磁盘来构成RAID磁盘阵列以进步磁盘读写速率,那么全体的功用会有很大的提高。