1、导言

跟着工业企业生产规模的扩大和自动化程度的进步,现场总线网络体系在大中型工业企业的自动生产操控中得到了广泛运用。大部分现场总线均运用有线传输技能作为其底层通讯办法,而在一些特别工业现场环境中,现场设备需求具有必定的移动性,有线介质的运用约束了设备的移动。为了处理设备的移动问题能够挑选运用红外线、802.1lx、蓝牙等线缆代替技能来代替有线介质作为底层通讯介质。运用无线技能衔接的现场无线网络尽管进步了网络的灵活性,但却构成留传有线现场总线和无线现场网络构成网络“孤岛”。为了完结两种网络的信息同享,需求在两者的鸿沟运用接入设备完结两者的互操作。本文根据SOPC技能规划了能够有用衔接EPA有线网段与蓝牙无线网段的接入点。

2、完结原理

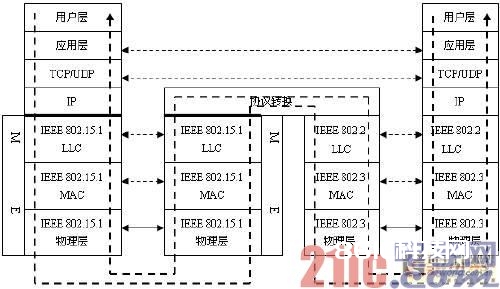

因为蓝牙技能开始首要是为消费类电子运用而规划的,在规划协议栈时考虑了对其他运用层协议的支撑,如RFCOMM是根据ETSI 07.10标准的串行仿真协议,还有电话操控协议等,其协议栈为通用协议栈[1]。考虑到操控网络中传送的信息多为短帧信息,且信息交流频频的特色,一起为了使操控网络的通讯协议简略有用,作业效率高,缩短体系呼应时刻,进步通讯的实时性和时刻确定性。因而,咱们在归纳剖析操控体系的特色和蓝牙协议栈的基础上,以及在EPA中蓝牙接入协议参阅模型的基础上,提出并完结了一种运用模型。该运用模型的体系结构如下图1所示。

图1中的粗实线代表蓝牙主机操控器接口(HCI),HCI供给了一种拜访蓝牙硬件才能的通用接口,HCI固件经过拜访基带指令、链路管理器指令、硬件状况寄存器、操控寄存器以及事情寄存器完结对蓝牙硬件的HCI指令。

通讯进程如下:经过调用HCI指令树立数据链路层衔接,当衔接树立成功后,把获取的IP分组包封装成HCI数据帧,经过蓝牙物理层传输至EPA网络蓝牙接入点BEPA,BEPA收到后,解包,取出IP分组包,再选用802.3协议封装成局域网数据帧,终究经过网卡发送出去。

图1 EPA中蓝牙通讯协议的运用模型

3、EPA蓝牙接入点的规划

针对以上的EPA蓝牙接入的运用模型,本文选用SOPC技能、现场总线技能规划了一种适用于EPA工业以太网的蓝牙无线接入计划。该计划的中心部分即选用NIOS II软核作为处理器。运用NIOS II软核处理器代替通用处理器(如ARM、单片机)[2],不只简化了电路结构,并且增强了编程的灵活性,节省了硬件资源,并且FPGA的现场可编程的特性有利于体系的软件和硬件晋级。本规划首要包含EPA协议栈处理部分和蓝牙协议处理部分,前者由NIOS II处理器完结,后者由BCM04模块完结,两者之间经过UART串口相连。以下分别从硬件规划计划和软件规划计划进行详细描绘。

3.1 硬件体系规划

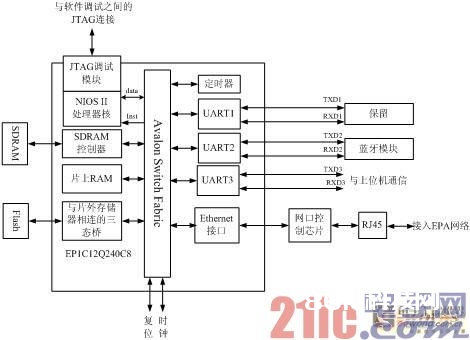

图2是EPA蓝牙接入点的硬件体系结构框图。整个规划的中心电路用一片高端体系级FPGA完结,可将嵌入式处理器、存储器、逻辑单元以及高性能I/O集成在一个芯片中,选用自顶向下的规划办法,对整个体系进行计划规划和功用区分,用硬件描绘言语HDL完结体系行为规划,终究经过归纳器和适配器生成终究的方针器材。在规划中FPGA选用了Altera公司的Cyclone系列的EP1C12Q240C8芯片,内嵌32位RISC软核处理器NIOS II。

在进行硬件规划时分两步完结,首先是根据需求规划EP1C12Q240C8芯片的外围电路,包含网络接口单元、存储器单元、串口通讯单元、复位电路、JTAG、时钟电路、电源电路等。其次,运用Altera公司供给的Quartus II开发软件对FPGA内嵌的NIOS II软核及其相关接口进行规划。

图2 EPA蓝牙接入点的硬件结构框图

3.1.1 网络接口单元

以太网接口芯片选用了SMSC公司专门用于嵌入式产品的LAN91C111快速以太网操控器。该芯片内部一起集成了以太网介质拜访操控器(MAC)及物理层收发器(PHY),支撑10/100M全双工传输形式、能够便利地与各种体系得CPU衔接。本规划中运用了异步总线接口形式,并与FLASH共用地址线和数据线,经过FPGA上的适配模块衔接到Avalon片内总线。

3.1.2 存储器单元

因为存储操作体系内核、EPA协议栈、程序数据等的需求,本体系运用了一片型号为AM29LV320D的FLASH芯片。该芯片由AMD公司推出,容量为4MB,支撑CFI接口,其与Avalon总线的衔接需求FPGA内部的总线适配模块进行时序匹配。SDRAM用于存储运转期的程序代码和数据,HY57V641620芯片为现代公司推出的容量达8MB的SDRAM,因为该芯片端口的宽度可达32位,因而体系中运用单芯片即可。SDRAM读写时序比较复杂,需求在FPGA中集成专用的SDRAM操控器IP核与其对接。

3.1.3 蓝牙模块

蓝牙模块的完结选用了CSR公司的单芯片BCM04。BCM04内嵌BlueCore04芯片,并供给SPI、UART/USB、PIO、PCM接口。单芯片蓝牙无线和基带%&&&&&%BlueCore04内有16位RISC微操控器,可作为一个简略的嵌入式操控器及蓝牙链路操控器,可运转蓝牙软件协议栈及高层运用程序。该模块的需求与NIOS II内部的UART串口IP核衔接以完结与处理器的无线通讯功用

3.1.4 FPGA内部IP核

为完结与上述3个外部单元的衔接,还有必要在EP1C12Q240C8芯片内部定制相关的接口电路。其间包含一个定时器,为EPA协议栈供给本地时钟,该时钟有必要与EPA网络中的主时钟同步;两个UART串行接口操控器,其间一个与蓝牙模块衔接,完结蓝牙数据的收发,另一个需求外接电平转化芯片后与上位机衔接完结上位机的监控功用;一个以太网接口操控器,完结对LAN91C111的接口操控;此外还包含 SDRAM和FLASH接口等部件。一切的部件都由Altera公司以IP核的办法供给,可便利复用。体系部件及其功用见图3所示。NIOS II和一切部件经过Avalon总线衔接在一起,构成根据Avalon总线的SOPC体系架构。Avalon总线是Altera公司开发的片上总线,是一种简略的总线体系结构,用来将处理器和周边设备集成到SOPC中,并规则了主设备和从端口的端口衔接办法的时序联系。