跟着核算机技能的开展,人们开端把它运用到越来越多的范畴,例如金融剖析、科学核算、网络服务运用、医疗成像等等。尽管这些不同范畴有着各异的运用程序和算法,但关于高功能的核算机而言,它们一起的需求便是,对程序要有强壮的履行功率,并且可以完结较快的核算速度。

为了进步HPC的核算才能,在最近的几年中,人们开端把其他各种高功能架构开端向机群体系搬运。但是,现在的机群体系大多仍是传统的CPU,为了寻求核算才能,仅仅是不断的添加核算节点,终究服务器会堆到机房外面。

假如在HPC体系中的核算节点上参加FPGA(现场可编程门阵列)作为协处理器,经过对FPGA进行特定程序算法优化,可以大大进步对特定运用程序的履行功率,一起还可以大大下降体系的功耗,并下降体系TCO。

跟着干流服务器芯片厂商中AMD和Intel先后敞开了CPU接口总线IP核,使得FPGA同CPU总线直接接口变得愈加简单,而不需求再选用IO接口进行规划专门的协处理IO卡。现在已经有许多的厂商开端供给相关的协处理器。

HPC变迁趋势和机群架构的新问题

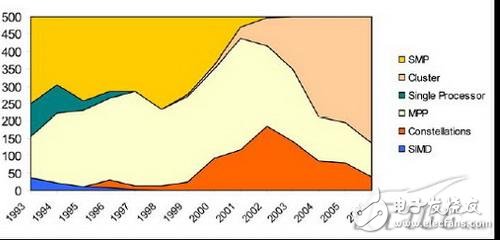

关于高功能核算(HPC),其特点是核算才能强,一般为特别规划的超级核算机。之前的超级核算机架构多是SMP、MPP、SMD等,图1所示为TOP500中HPC的架构变迁。

集群(Cluster)技能是近几年鼓起的开展高功能核算机的一项技能,选用Cluster体系结构集群体系,具有可自在弹性、高度可办理、高可用、高功能价格比等许多长处,从图1中咱们可以看到机群体系逐步在HPC运用上代替MPP开端占有干流方位。

图1 TOP500中体系架构开展状况

尽管机群体系有着上述种种优势,但因为运用了通用的处理器,跟着运用对核算才能需求的日益添加,人们不得不被迫添加核算结点数目,添加CPU数目来应对核算才能需求的进步。现在的机群体系从本来的几十个核算结点,到现在的成百上千个结点,乃至到不远的将来上万个核算结点,机群体系的缺乏也随之日趋显着。首要体现在:榜首、受机柜高度和传统1U机箱的约束,核算密度比较疏松,并且密度无法打破;第二、装置保护作业量和本钱过大;第三、关于大规模机群,功耗日趋成为瓶颈;第四、智能而有用的办理监控成为大规模机群体系新的应战。一切这些问题都会导致数据中心的全体具有本钱的添加(TCO),这关于长时间运营的数据中心而言,是最不想看到的。

而最大的问题在于,关于一切的运用而言,都选用相同的CPU进行运算处理,而像金融剖析、生物核算、科学核算,对CPU资源的需求是不同的,因此选用相同的体系,就不可以实践取得机群体系所标称的功能。

现在,人们开端寻觅一种代替方法,可以看到的是选用依据FPGA的协处理器来加快运用软件的要害算法履行。这种方法类似于曾经提出过的在C++代码中的内层循环选用汇编言语来直接编写,以优化要害程序运转。

相关于现在的X86处理器而言,FPGA一般都运转在比较低的时钟频率下,优势在于有着较高的内存带宽、杰出的并行处理才能和超卓的依据运用环境的硬件定制化才能。假好像在服务器上添加一颗处理器/内核比较,仅仅在服务器上添加一颗FPGA的协处理器,一般状况下功能可以进步2至3倍,而功耗则可以下降40%,依据运用状况进行算法优化的话,最大可以进步功能达10倍。

FPGA协处理器为HPC加快

正如上文所言,现在HPC运用涵盖了多个范畴,有着不同的核算需求。例如在商业数据剖析和基因测序中,要进行许多的数组运算、线形数据匹配、逻辑测验等等,而关于医疗成像、核算化学而言,其首要作业是同步映射、过滤等等。这些不同的运用需求不同的数学逻辑操作以及有用的内存衔接读取等。

通用的CPU、专用的图画处理CPU(现在称之为GPU)或网络处理CPU,都无法为HPC运用供给一个可选的通用处理方案。而FPGA作为一个可重构核算引擎,可以在软件操控下进行硬件单元优化作业,来满意不同HPC运用需求,然后供给核算功率。从某种程度上说,选用依据FPGA协处理器的可重构核算硬件渠道,可以有可能让HPC在各种运用软件下到达很高的功率。

FPGA经过把高功能核算算法中固有的并行运算部分硬件化来完结HPC运用加快。其实这种并行可分为多个等级,在机群核算中在多个CPU上进行使命的多线程分配咱们可以称之为“使命级并行”。第二级并行咱们称之为“指令并行”,传统的CPU支撑数量有限的指令并发处理,便是CPU指令流水线的管道数或许发射数比较有限。而FPGA则可以供给许多管道,也便是说可以一起并行履行许多的指令。“数据并行”是FPGA很简单完结的第三级并行处理才能,FPGA的结构十分简单完结并行操作。因此,经过装备,它可以一起履行许多的数据吞吐操作,在这种状况下,该设备相当于多个传统CPU在一起作业。

假如完结上述三种等级的并行处理,一个200Mhz的FPGA处理才能将远远超越一个3Ghz的通用CPU,但是功耗仅仅是后者的1/4。例如在生物核算中,FPGA在处理DNA基因排序上能往往可以比通用CPU加快50倍到100倍;而在医疗CT的2D/3D图画处理上可以加快10倍左右;而对与一些通用的算法如FFT,一般状况下FPGA的加快至少可以到达10倍以上。

一个规范FPGA协处理器的比如

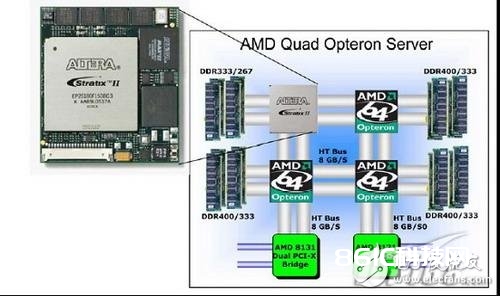

本文以XtremeData公司的协处理器产品为例,介绍其运用环境及作业流程。图二是XtremeData 公司的x86 FPGA 协处理器什物以及运用渠道状况。从图中可以看出,该协处理器产品可以直接放置在一般的4路或许两路Opteron体系上,该体系可以是机架式服务器或刀片产品。

该协处理器模块同CPU管束兼容,一起可以直接运用板上衔接在协处理器上的内存条,或许经过HT总线运用其他CPU上衔接的内存条。这种结构有很大的优势,主板可以不必作任何改动,也便是说在一般的服务器上可以即插即用,一起还可以直接运用主板资源,并获取很大的HT总线带宽和低推迟。

图2 典型协处理器运用架构

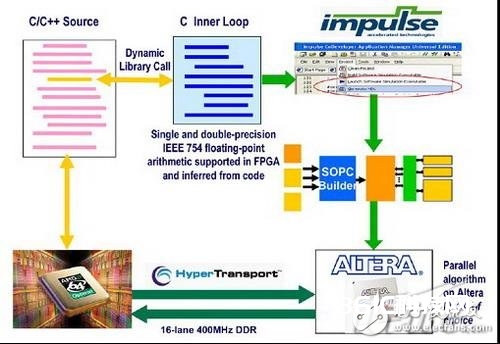

其作业原理把适用于该芯片的算法库装置在主机上,依据运用不同,主机上的GUI可以在线装备和更改FPGA内硬件进行不必算法的优化。当然,条件是关于各种HPC运用都要完结完结算法库的编写,并转换成FGPA可以辨认的硬件描绘言语库,经过加载该言语库,可更改FPGA内部硬件结构,完结运用程序的硬件加快。图3为体系作业流程。

图3 协处理器装备和完结进程

在履行进程中,关于并行性较强、浮点运算需求较高的核算可以经往后HT总线丢给协处理器进行核算,并继续获取核算结果,主CPU首要担任IO处理以及程序调度作业,然后完结协处理器的加快作业。

CPU 厂商持敞开情绪

CPU厂商现在对协处理器的呈现并没有持抵抗情绪,而是比较支撑协处理器的开发。

AMD首先提出Torenza协处理渠道,答应第三方处理器与Opteron协作,敞开相关接口。之后,Intel在IDF上也提出了自己的体系架构敞开方案。Intel高档副总裁Pat Gelsinger宣告,Intel将向Xilinx等第三方FPGA生产商敞开前端总线(FSB)授权,以便他们的芯片能经过前端总线和内存操控器 (MCH)的直连与Intel处理器协同作业。好像AMD的HyperTransport总线,Intel的前端总线授权也能让各种加快单元参加一个高带宽、低推迟的总线,然后在Intel体系中与MCH直接相连。

至此,两个通用处理器的伟人对协处理器都抱着支撑和看好的情绪,大大方便了第三方厂商进行协处理器同通用处理器的接口的开发作业。

总归,从商场来看,现在IBM 的cell、美国的Cleaspeed、DRC、Mitrionics和Celoxic等公司都有相应产品供给。在现在的运用中,Sun公司在为东京理工大学制作的超级核算机就选用了ClearSpeed的协处理器卡进行了加快,Cray公司现在在超级核算机上也有运用。

不过,该技能从现在的状况来看还不是很老练,间隔大规模商业运用还有必定的间隔。首要问题在于:不同的HPC范畴运用算法各异。而作为可重构核算的 FPGA协处理器,关于不同的算法都需求经过硬件描绘言语解说和完结,需求进行许多的算法库的作业。而现在没有公司可以供给足够多的IP核供运用,只能在少量运用上进行FPGA协处理器的加快。当然,因为Linepacke是HPC的首要测验软件,而各家公司的产品都可以加快Linpake的功能测验。

从长远看来,因为FPGA可重构的协处理器有着上文描绘的种种优势,所以在将来的HPC运用中,处理的不同算法的硬件描绘转化的问题后,将会得到许多的运用。