导言

跟着遥测体系的不断发展,体系杂乱程度也随之进步,因此在终端规划中,对信号源的频率安稳度、幅值规模和频率规模提出了越来越高的要求。这就要求遥测体系具有高码速、实时可重构、处理杂乱结构的才能,传统的数字电路难以完结这些杂乱功用。FPGA(现场可编程门阵列)是近几年发展起来的硬件可编程芯片,具有硬件密度高、结构灵敏、可编程、加密性强等杰出功用,在高速信号处理范畴占有至关重要的方位,也为多路模仿量信号源的完结,供给了有用的途径。本文针对遥测运用,以大容量FPGA器材为中心,完结了电源独立的不同频率、不同波形的多路模仿量信号源。

1 体系硬件规划

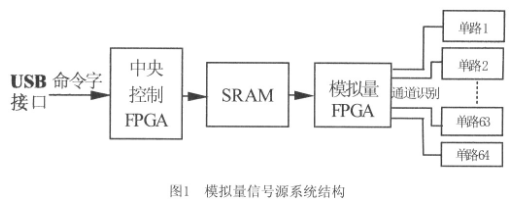

现在,大容量的FPGA首要有Altera、Xilinx、Lattice、Actel、Cypress等公司的产品。比较而言,Altera CycloneII系列FPGA芯片速度快、容量大、内嵌RAM多、而且有DSP硬件乘法器,是低成本、低功耗运用的最佳挑选。因此在本文中选用Altera公司的Cyclone II系列FPGA-EP2C8芯片,EP2C8芯片是1.25 V内核供电,具有8.256个逻辑单元(LE),36个M4K RAM块,RAM总量为165,888,18个嵌入式乘法器以及208个管脚,其间包含182个最大可用I/O引脚。Altera公司有相应的开发软件渠道Quartus II,此软件功用强大,运用简略,支撑的器材品种很多,可支撑在线仿真,在线下载等,并具有丰厚的IP核及逻辑功用模块资源,便于运用VHDL+模块/原理图输入界面等等。模仿量信号源首要包含中心操控FPGA单元、模仿量FPGA、静态存储SRAM、单路模仿量单元,如图l所示,

整个体系运用USB 2.0接口与计算机进行通讯,信号由计算机软件生成波形数据,通过USB口下载到主控FPGA,通过16位SRAM锁存,将各路信号传至模仿量FPGA,经由解码分路选通,输出电源独立的不同频率、不同波形的多路模仿量信号。其间包含4路单极性幅值O~30V,60路双极性幅值±15V;四种波形分别为锯齿波、正弦波和方波(占空比1:1),信号频率为0~50Hz,以及固定电平,幅值能够初始设定,并可完结实时可调。

2 单路模仿量组成模块规划

2.1 体系构成

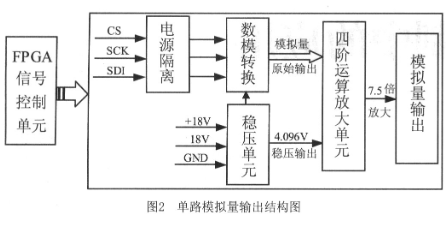

单路模仿量由电源阻隔单元、前端稳压单元、数模转化(DAC)单元和运算扩大单元等构成,详细构成如图2所示,体系由双18 V供电通过稳压单元输出4.096 V,给DAC和运放芯片供给作业电压,别的通过指令发动信号在SPI总线上发送FPGA的CS、SCK、SDI信号,传至单路模仿量,将相应数字量进行D/A转化,得到的模仿量数据经由运算扩大输出,即可完结64路模仿量波形。体系时钟同步输出,具有很高的可靠性。

2.2 组成模块规划

2.2.1 电源阻隔单元

64路模仿量信号要求对每路信号进行独立电源阻隔,本文选用的ADUM1300是根据ADI公司磁耦阻隔技能的通用型三通道数字阻隔器,通过克己高压阻隔信号调度电路,能够输出体系使命要求的彼此阻隔的、独立基准模仿量信号,完结SPI接口和数字转化器的阻隔。它选用了高速CMOS工艺和芯片级的变压器技能,在功用、功耗、体积等各方面都有光电阻隔器件无法比拟的优势。ADUM130数字阻隔器在一个器材中供给三个独立的阻隔通道,两头作业电压为2.7V~5.5V,支撑低电压作业,并能完结电平转化。别的,ADUM130具有很低的脉宽失真(《3ns),功耗仅为0.8mA,作业电压为3V/5V,传输速率为1M/25M/90Mb/s,ADuM130还具有直流校对功用,有一个改写电路确保即便不存在输入跳变的状况下,输出状况也能与输入状况相匹配,这关于上电状况和具有低数据速率的输入波形或安稳的直流输入状况是很重要的。

2.2.2 前端稳压单元

REF198精细电压基准,初始精度0.05%,温漂5ppm/℃,输出电流30mA,最大电源电流45 μ A,电源电压规模6.4V~15V,输出电压4.096V,每路输出电压与理论设置值的差错在30mV以内;每路驱动才能不低于5mA;该芯片一起为数模转化(DAC)模块和运放模块供给作业电压。

2.2.3 DAC单元

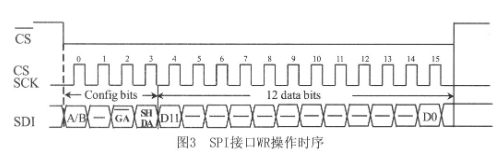

MCP4821是12位DAC芯片,本文中是单电源供电,32.768 MHz时钟支撑的SPI接口,温漂50ppm/℃,电源电压规模2.7V~5.5V,内部参阅电压为2.048V,FPGA向MCP4821写入16位数据,如图3所示,高四位是芯片装备位(Config bits),其它12位是数据位(data bits),在CS信号上升沿有用时,通过16个时钟脉冲完结转化。

2.2.4 运算扩大单元

AD824运算扩大器是美国AD公司出产的单电源、低功耗、精细场效应输入的运算扩大器。选用双电源作业时,它的输出电压能够到达电源的正负电源电压。AD824的芯片内含有四个功用匹配的运算扩大器。在本规划的双电源作业时,额外作业电压由±1.5v到±18v。它们的输出电压摆幅仅比电源电压小10mV。输入信号有或许呈现大于+VS时,运算扩大器的同相输入端串联一个电阻,典型值为1k Ω,就能避免输入信号的相位反相,但将发生附加的输入电压噪声。

3 电磁搅扰规划

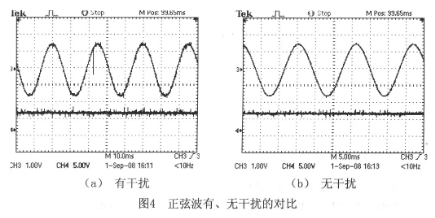

在整个电路体系中,电磁搅扰首要呈现在输入与输出接口处,其内部结构一般不会呈现电磁搅扰。本体系对输入输出信号进行接口维护,避免电磁搅扰的发生;并选用线性电源及电源滤波模块,要害模块均进行电磁屏蔽,以最大程度下降模块问的互扰。如图3所示,左边为有电磁搅扰的正弦波,能够很明显地看出,在正弦波波峰方位忽然呈现一个下拉电平,通过屡次剖析,此现象为输入电源遭到严峻搅扰而引起,右侧为通过II滤波模块后的波形。

4 结束语

本文运用FPGA完结了模仿/数字信号收集体系规划,异步串行数据传输等,而且通过多路切换开关循环收集,完结了对高速信号的收集和准确的电路规划,体系功用安稳,数据收集精度较高,抗搅扰才能较强,具有很高的运用价值和杰出的运用远景。通过屡次长期上电测验,能发生频率、幅值可调的波形信号,每路波形输出电压基准阻隔,调理精度高达1%,远高于一般的信号源,彻底满意体系规划的要求,已成功运用于某遥测信号源。

责任修改:gt