作者:吴学礼,李培,孟凡华,孟华

前语

由空气动力学原理,当超音速运动的物体,因为运动速度大于部分声速时会发生激波,弹道声波是超声速弹丸飞行时冲击空气分子所构成的激波(Shockwaves)。选用激波原理进行报靶是一项具有挑战性的技能,它运用激波信号进行超音速飞行体勘探,是一种新的方针勘探办法。本文研讨目标为移动靶车,该遥控主动装置自带电源和动力装置,能在25Km/h内无级调速,可是,因为其作业环境比较恶劣,本身振荡、风吹、发电机和电动机的巨大搅扰,严重影响了主动报靶体系的报靶精度。为了习惯现代化*练习的需求,本文选用FPGA和自习惯滤波技能,运用硬件电路来完结LMS自习惯滤波器,完结对强背景噪声环境下激波信号的滤波,在满意实时数据处理前提下,以进步报靶体系的报靶精度。

1问题的提出及计划选取

本规划起先规划电路选用的模仿高通滤器,后来又规划成带通滤波器,但是通过实践发现,其滤波效果都比较差,难以满意体系精度的要求;选用通用DSP数字信号处理器材用软件规划数字滤波器,其数据吞吐率、处理速度和实时性远不如依据FPGA硬件完结的数字滤波器,因为,依据FPGA的数字滤器代表了未来数字信号处理的发展方向,用户可以很便利的结合实践需求规划出自己的可编程数字信号处理芯片,现在现已较为广泛地运用在高端数字信号处理范畴。

自习惯滤波器的常用完结方法有FIR和IIR两种,而FIR滤波器是实践运用较为广泛的一种,FIR滤波器只要可调的零点,因而它没有IIR因兼有可调的零点和极点而带来的不安稳问题,此外,LMS核算量小,易于硬件完结,故本文选用的滤波器是依据FIR根底之上构建的LMS自习惯滤波器。

2体系规划结构

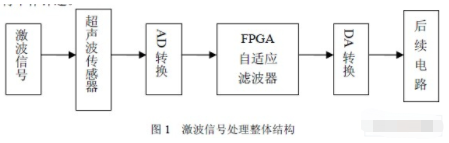

本文所触及的激波信号处理部分的全体结构框图如图1所示,由信号收集传感器、模数转化器件、FPGA器材、数模转化器件构成。高速瞬态的激波信号被超声波传感器捕获今后,通过恰当调度送到AD转化器材,本规划选用MAX197AD转化器材,由FPGA规划的状况机对其操控,进行AD转化,然后再进入依据FPGA规划的自习惯滤波器中滤波,终究再进行DA转化传输到后续处理电路,因为本规划的首要使命是规划依据LMS算法的自习惯滤波器,其它部分将不作胪陈。

3LMS自习惯滤波器规划

LMS算法是以希望响应和滤波器输出信号之间的均方值为原则,依据输入信号在迭代进程中估量梯度矢量,并更新权值系数以到达最有用的一种自习惯迭代算法,它在优化办法中选用了依据随机梯度的最速下降法。依据LMS算法的完结进程,在FPGA完结时,可以分为首要的几个模块:FIR滤波器模块、差错核算模块、权值存储模块、权值更新模块以及操控模块。其模块框图如图2所示。规划中选用VHDL言语规划,依据MAX197的转化要求,其输出为12位宽度的数字信号,因而,此处选用12位并行数据输入,12并行数据输出,权值系数的数据宽度为16位,reset为体系复位,高电平有用,clk为体系时钟,firen为FIR滤波器使能,suben为差错核算模块使能,cuncuen为权值存储模块使能,coffen为权值更新模块使能,都为高电平有用。

4自习惯滤波器的FPGA完结

4.1N阶FIR滤波器模块的规划

FIR滤波器是数字滤波器的一种,它的输出可以用差分方程表明如下:

其间:N是FIR滤波器的抽头数,x(i)表明第i时间的输入样本,h(i)是FIR滤波器的第i级抽头系数。FIR滤波器的单位脉冲响应h(n)是一个有限长序列,其体系函数可表明为:

在规划中,为了节约FPGA的内部资源,进步运用功率,此处选用串行乘加的办法完结。FIR滤波器模块完结16阶的FIR滤波,输入量首要包含AD转化后的激波信号数据的输入和权值系数的输入,xin是AD转化后的输出信号,为12位字宽,其间1位符号位,10位精度位,将此信号存储在深度为N的RAM中作为16阶FIR滤波器的输入;FIR的权系数win存储在别的一个RAM中,字宽16位,其间最高位为符号位。通过操控模块输出地址信号操控读各个存储模块的读写动作,此处的乘法器为28位有符号数的乘法器,加法器完结累加使命,当16阶乘法以及累加运算做完后,由操控模块输出youten信号,对锁存的数据进行有用截取,然后输出。其完结的框图如图3所示。在该规划中,选用VHDL言语编程完结,生成对应的顶层原理符号,然后按规划计划把它们连接成顶层原理图。

4.2操控模块本模块首要是操控从激波数据输入模块和权系数输入模块读取数据输入信号和权系数到乘法器的输入端,一起还操控累加器完结累加使命,然后发生一个使能信号,对输出数据进行截取操作,然后输出到下一级模块中。本模块为整个体系的中心部分,它首要完结:初始化各个模块;依据体系时钟发生各个模块的操控信号,操控每个单元完结特定的作业;选用全体流水线和部分流水线的方法,和谐各个模块作业,然后进步整个滤波体系的全体功用。

4.3核算模块

本模块包含:差错核算模块和权值核算模块。差错模块实践便是一个减法器,首要核算FIR滤波器输出和希望值之间的差错,然后,在操控模块的效果下,当差错满意规划要求时,便使能其输出,得到终究的输出成果。在权值核算模块中,归纳考虑收敛性和规划完结,设定u=1/4092,即u=10H,这样只需对差错核算模块的差错输出进行移位运算即可完结,省掉了乘法器的运用,节约了FPGA资源,进步了核算速度,别的,在核算2ue(k)x(k)时,可以在e(k)与x(k)相乘后直接右移12位,即可得出权值变量。

5自习惯滤波器的仿真与校验

在QuartusII6.0归纳环境下,首要对输入规划文件(.vhd、.bdf)进行编译(包含建库、逻辑归纳、器材适配、仿真数据截取等),体系主动编译完结后主动生成.pof文件,然后通过JTAG下载电缆把.pof文件下载到FPGA器材中即可。本规划选用CycloneII系列的EP2C8Q208C8芯片,体系时钟为20MHz,输入信号、参阅输入和滤波器输出都是12位,考虑到FPGA还要完结其它功用,因而在进行体系的芯片选型时,留有较大的冗余量。试验时,调试电路板从核算机中读取输入数据到FPGA中,然后通过FPGA处理后,将处理的数据送回核算机中。

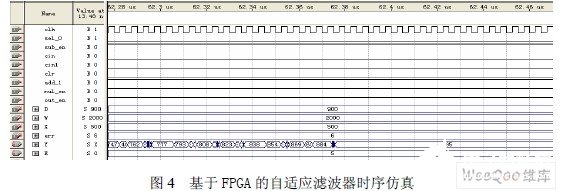

仿真时,设希望信号为900,输入信号为500,实践输出为895,差错为5,在63.2us处收敛到安稳状况。其时序仿真波形如图4所示。

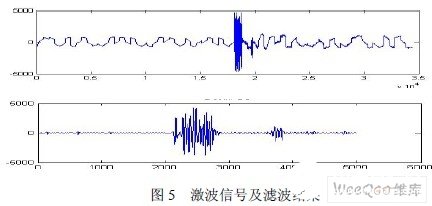

用LabVIEW编写的上层软件收集激波数据,以txt文件格局保存。运用MATLAB的load指令,制作出图5上半部分的激波信号,据图显着看出,弹丸穿过靶平面时的激波稠浊有很多高低频搅扰。为了验证上述自习惯滤波器的滤波才能,在进行试验时,将此数据送入到FPGA中进行处理,再送回到核算机中,运用绘图软件制作其滤波成果,其滤波成果见图5。

从上图可以看出,在强噪声搅扰下,很难分辨出实在有用的有用信号,选用LMS自习惯滤波器进行滤波后,可以实在有用地滤除搅扰噪声。

6结束语

本文运用FPGA器材完结了依据LMS自习惯FIR滤波器,由上述试验成果可以看出,依据FPGA完结的自习惯滤波器,可以实时有用地滤除掺杂在激波信号中的噪声,可以精确捕捉到实在的激波信号,为后续部分处理奠定了坚实的根底,然后为进步主动报靶体系的报靶精度奠定了坚实根底。

本文作者立异点:将先进的FPGA技能和自习惯滤波技能运用于主动报靶中,完结了依据FPGA的自习惯滤波器,对整个激波信号处理体系进行了严重改善,进步了移动报靶体系的报靶精度。

责任编辑:gt