集成电路测验(IC测验)首要的意图是将合格的芯片与不合格的芯片区分隔,确保产品的质量与牢靠性。跟着集成电路的飞速开展,其规划越来越大,对电路的质量与牢靠性要求进一步进步,集成电路的测验办法也变得越来越困难。因而,研讨和开展IC测验,有着重要的含义。而测验向量作为IC测验中的重要部分,研讨其生成办法也日渐重要。

1 IC测验

1.1 IC测验原理

IC测验是指依据被测器材(DUT)特色和功用,给DUT供给测验鼓励(X),经过丈量DUT输出呼应(Y)与希望输出做比较,然后判别DUT是否符合格。图1所示为IC测验的根本原理模型。

依据器材类型,IC测验能够分为数字电路测验、模仿电路测验和混合电路测验。数字电路测验是IC测验的根底,除少数纯模仿IC如运算放大器、电压比较器、模仿开关等之外,现代电子体系中运用的大部分IC都包含有数字信号。

图1 IC测验根本原理模型

数字IC测验一般有直流测验、沟通测验和功用测验。

1.2功用测验

功用测验用于验证IC是否能完结规划所预期的作业或功用。功用测验是数字电路测验的底子,它模仿IC的实践作业状况,输入一系列有序或随机组合的测验图形,以电路规则的速率作用于被测器材,再在电路输出端检测输出信号是否与预期图形数据相符,以此判别电路功用是否正常。其重视的重点是图形发生的速率、边际守时操控、输入/输出操控及屏蔽挑选等。

功用测验分静态功用测验和动态功用测验。静态功用测验一般是按真值表的办法,发现固定型(Stuckat)毛病。动态功用测验则以挨近电路作业频率的速度进行测验,其意图是在挨近或高于器材实践作业频率的状况下,验证器材的功用和功用。

功用测验一般在ATE(Automatic Test Equipment)上进行,ATE测验能够依据器材在规划阶段的模仿仿真波形,供给具有杂乱时序的测验鼓励,并对器材的输出进行实时的采样、比较和判别。

1.3沟通参数测验

沟通(AC)参数测验是以时刻为单位验证与时刻相关的参数,实践上是对电路作业时的时刻联系进行丈量,丈量比如作业频率、输入信号输出信号随时刻的改变联系等。常见的丈量参数有上升和下降时刻、传输推迟、树立和坚持时刻以及存储时刻等。沟通参数最重视的是最大测验速率和重复功用,然后为准确度。

1.4直流参数测验

直流测验是依据欧姆定律的,用来确认器材参数的稳态测验办法。它是以电压或电流的方法验证电气参数。直流参数测验包含:触摸测验、漏电流测验、转化电平测验、输出电平测验、电源耗费测验等。

直流测验常用的测验办法有加压测流(FVMI)和加流测压(FIMV),测验时首要考虑测验准确度和测验功率。经过直流测验能够判明电路的质量。如经过触摸测验判别IC引脚的开路/短路状况、经过漏电测验能够从某方面反映电路的工艺质量、经过转化电平测验验证电路的驱动才能和抗噪声才能。

直流测验是IC测验的根底,是检测电路功用和牢靠性的根本判别手法。

1.5 ATE测验渠道

ATE(Automatic Test Equipment)是自动测验设备,它是一个%&&&&&%测验体系,用来进行%&&&&&%测验。一般包含计算机和软件体系、体系总线操控体系、图形存储器、图形操控器、守时发生器、精细丈量单元(PMU)、可编程电源和测验台等。

体系操控总线供给测验体系与计算机接口卡的衔接。图形操控器用来操控测验图形的次序流向,是数字测验体系的CPU.它能够供给DUT所需电源、图形、周期和时序、驱动电相等信息。

2测验向量及其生成

测验向量(Test Vector)的一个根本界说是:测验向量是每个时钟周期使用于器材管脚的用于测验或许操作的逻辑1和逻辑0数据。这一界说听起来好像很简单,但在实在使用中则杂乱得多。由于逻辑1和逻辑0是由带守时特性和电平特性的波形代表的,与波形形状、脉冲宽度、脉冲边际或斜率以及上升沿和下降沿的方位都有联系。

2.1 ATE测验向量

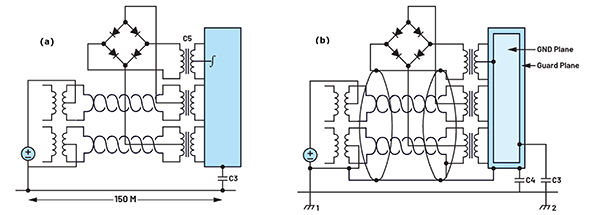

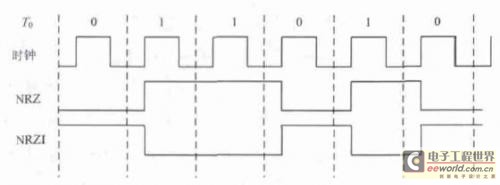

在ATE语言中,其测验向量包含了输入鼓励和预期存储呼应,经过把两者结合构成ATE的测验图形。这些图形在ATE中是经过体系时钟上升和下降沿、器材管脚对树立时刻和坚持时刻的要求和必定的格局化方法来表明的。格局化方法一般有RZ(归零)、RO(归1)、NRZ(非归零)和NRZI(非归零反)等。

图2为RZ和R1格局化波形,图3为NRZ和NRZI格局化波形。

图2 RZ和R1数据格局波形

图3 NRZ和NRZI数据格局波形

RZ数据格局,在体系时钟的开始时刻T0,RZ测验波形坚持为“0”,如果在该时钟周期图形存储器输出图形数据为“1”,则在该周期的时钟周期期间,RZ测验波形由“0”变换到“1”,时钟结束时,RZ测验波形回到“0”。若该时钟周期图形存储器输出图形数据为“0”,则RZ测验波形一向坚持为“0”,在时钟信号周期内不再发生改变。归“1”格局(R1)与RZ相反。

非归“0”(NRZ)数据格局,在体系时钟开始时刻T0,NRZ测验波形坚持T0前的波形,依据本时钟周期图形文件存储的图形数据在时钟的信号沿改变。即若图形文件存储数据为“1”,那么在相应时钟边际,波形则改变为“1”。NRZI波形是NRZ波形的反相。

在ATE中,经过测验程序对时钟周期、时钟前沿、时钟后沿和采样时刻的界说,结合图形文件中存储的数据,构成实践测验时所需的测验向量。

ATE测验向量与EDA规划仿真向量不同,并且不同的ATE,其向量格局也不尽相同。以JC-3165型ATE为例,其向量格局如图4所示。