本文提出一种根据FPGA 的数字核脉冲剖析器硬件规划计划,该计划选用现场可编程逻辑部件(FPGA),完结数字多道脉冲起伏剖析仪的硬件规划。用QuartusⅡ软件在FPGA 平台上完结了数字核脉冲的起伏提取并生成能谱。在此基础上经过电路规划建立了数字化能谱丈量试验设备,实测了137Cs的能谱,丈量结果与相同条件下的模仿能谱仪的实测谱彻底符合。由此证明根据FPGA 的数字多道脉冲起伏剖析器硬件规划计划的正确可行,具有实用性。

多道脉冲起伏剖析仪和射线能谱仪是核监测与和技能运用中常用的仪器。20世纪90年代国外就现已推出了根据高速核脉冲波形采样和数字滤波成型技能的新式多道能谱仪,使数字化成为脉冲能谱仪开展的重要方向。国内谱仪技能多年来一向停留在模仿技能水平上,数字化能谱丈量技能仍处于办法研讨阶段。为了满意不断增加的高性能能谱仪需求,迫切需求研发一种数字化γ能谱仪。经过核脉冲剖析仪显现在显现器上的核能谱协助人们了解核物质的放射性的程度。

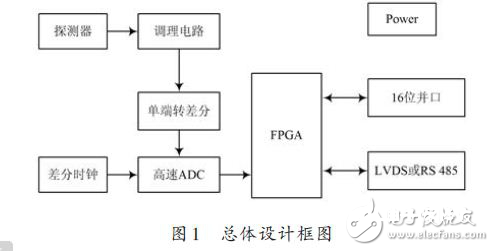

图1即为总体规划框图,探测器输出的核脉冲信号经前端电路简略调度后,经单端转差分,由采样率为65 MHz 的高速ADC 在FPGA 的操控下进行模/数转化,完结核脉冲的数字化,并经过数字核脉冲处理算法在FPGA 内构成核能谱,核能谱数据可经过16 位并行接口传输至其他谱数据处理终端, 也可经过LVDS/RS 485接口完结长途传输。特别需求留意的是,因为高速AD 前置,调度电路应该满意宽带、高速,且电路参数能够动态调整的需求,以习惯不同类型探测器输出的信号,然后更好地发挥数字化技能的优势。

前端电路

前端电路由单端转差分和高速ADC 电路组成。差分电路因为其杰出的抗共模搅扰才能而运用广泛。因为调度电路输出的脉冲信号为单极性信号,若直接送入ADC,将丢失一半的动态规模。规划中在运放中参加一个恰当的偏置电压,将单极性信号转化成双极性信号后再送入ADC,以确保动态规模。将信号由单端转化成差分的一起,进行抗混叠滤波处理,完结带宽的调整。

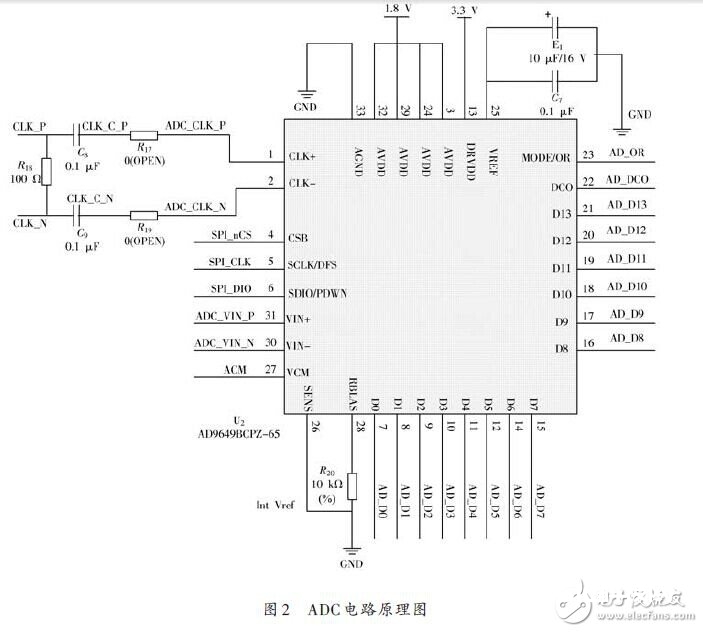

本规划运用AD9649 – 65 高速ADC 完结核脉冲的模/数转化,AD9649为14 位并行输出的高速模/数转化器,具有功耗低、尺度小、动态特性好等长处。当信号从探测器经过调度电路,过差分转单端电路后,以差分信号的方式进入ADC, 在差分时钟的操控下,转化成14 位数据,进入FPGA.该高速A/D 在外部FPGA 的操控下对信号进行采样。然后将采样后的数字信号送入FPGA 中完结数字核脉冲的起伏提取。图2 为A/D 转化的原理图,AD9649在差分时钟的同步下完结A/D 转化,D0~D13为14个有用输出数据位。

FPGA

现在国内外多道脉冲起伏剖析的数字化完结主要有2种计划:纯DSP 计划、DSP+可编程器材计划。本文将充分发挥FPGA 的并行处理优势,在单片FPGA芯片上完结核脉冲的收集与数字核脉冲处理算法,经Quar-tus-Ⅱ软件仿真与归纳,本文选用EP3C40 FPGA 芯片完结多道剖析器的数字化功用。

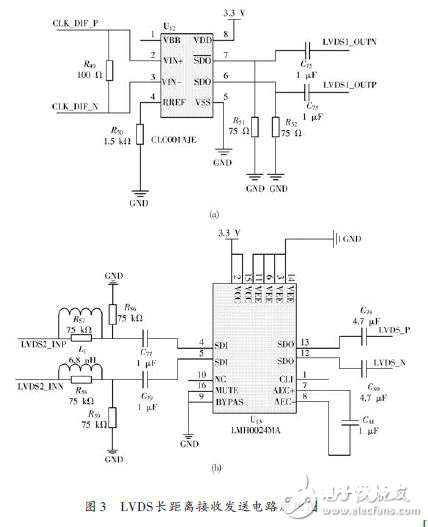

接口电路规划选用了LVDS 和RS485两种长距离数据传输接口,用于完结核能谱数据的长途传输。LVDS 即低电压差分信号,是一种能够完结点对点或一点对多点的衔接,具有低功耗,低误码率,低串扰,低噪声和低辐射等特色。LVDS 在对信号完整性、地颤动及共模特性要求较高的体系中得到了越来越广泛的运用。图3为低电压、最高数据传输速率为655 Mb/s 的LVDS 接口电路。

根据FPGA 的数字核脉冲剖析器硬件规划计划。该计划在单片FPGA 中完结了多道脉冲起伏的数字剖析功用,经过软件功用仿真和实践运转,说明晰数字多道脉冲起伏剖析器硬件规划的可行性,将FPGA 运用到数字能谱丈量体系能充分发挥其并行处理优势,并能有用下降硬件电路规划的复杂度。