0 导言

现在高速数据收集技能越来越得到人们的注重,传统的USB 2.0收集渠道理论带宽只要480 Mbps,实践传输才干只要30 Mb/s左右,而USB 3.0收集渠道理论带宽达到了5Gbps,能有用处理USB2.0收集体系的缺点。现在一些收集体系选用单片机为主控芯片,则不能充沛发挥USB3.0的带宽,功用欠安。本文研讨和规划了一套依据USB3.0总线的数据收集体系,此体系选用高速CPLD芯片MAX7000A作为主控芯片,CYUSB3014作为USB3.0主机接口芯片,能完成超高速实时数据收集与传输。

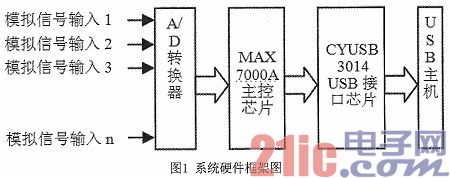

1 体系硬件规划

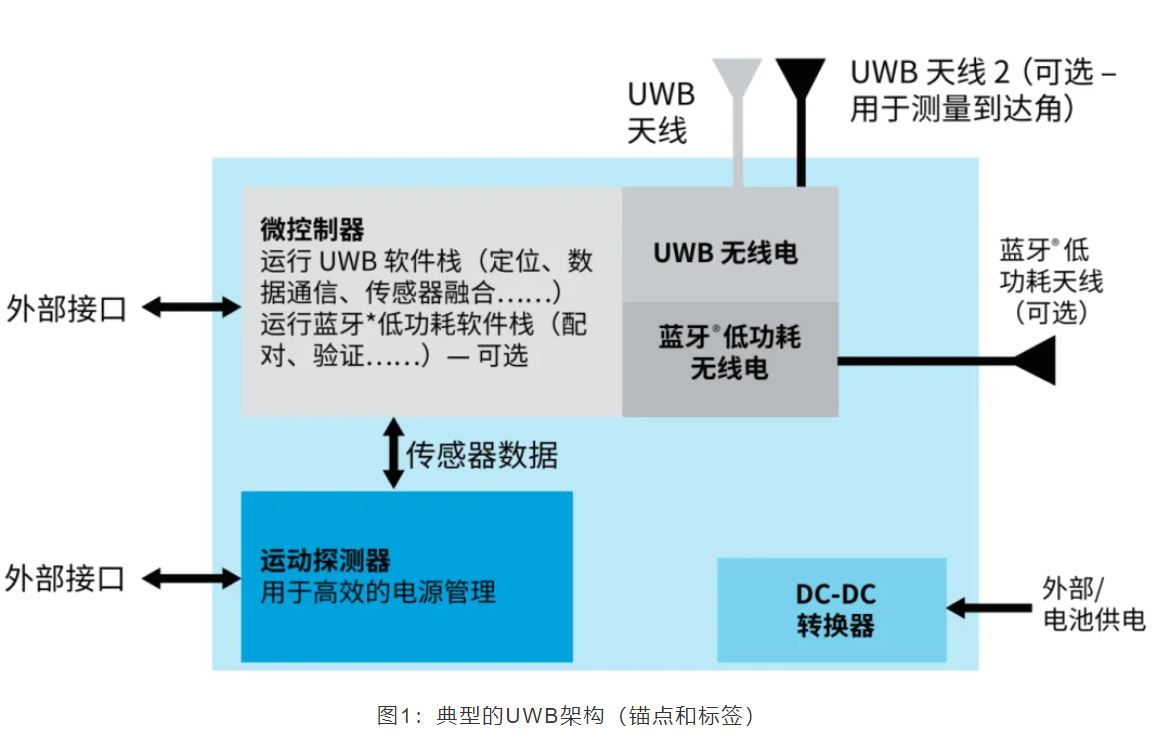

体系的整体结构如图1所示。被收集的信号经过相应的传感器转换为相应的模仿电压,A/D芯片将其转换为数字信号,再送到CPLD主控芯片MAX7000A,经处理后发送到USB 3.0主机接口芯片CYUSB3014,该芯片作业在SLAVE FIFO形式,最终数据以5Gbps的速度送入到计算机。

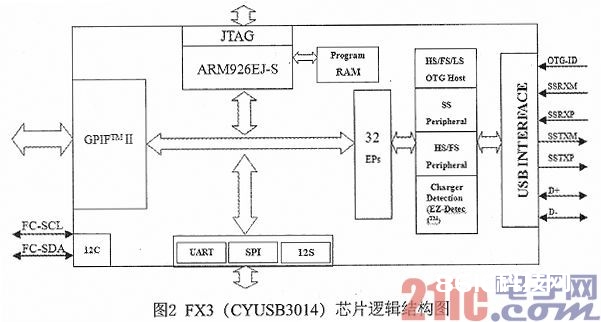

美国的赛普拉斯(CYPRESS)公司开发的EZUSB FX系列芯片以其强壮的功用,简易的开发进程而深受开发者喜欢。EZ—USB FX3(CYUSB3014)芯片是其最新的USB接口芯片,不只完全符合USB3.0标准,并且还能够与DSP、FPGA、CPLD和单片机等处理器方便地相连,然后简化了体系的规划。EZ-USB FX3芯片内部逻辑结构如图2所示。

CYUSB3014的内核为一个200MHz作业频率的32位ARM926EJ处理器,其经过固件程序和内部DMA通道办理USB和GPIF II、I2S、SPI、UART接口之间的数据传输。CYUSB3014内部有一个能完成5Gbps传输速度的GPIF II接口,该接口能够方便地与MAX 7000A衔接。GPIF II接口不只作业频率可达100MHz,并且其数据总线能够依据需求挑选8位、16位和32位中的任何一种。当然,只要选用了32位的数据总线,才干充沛发掘其带宽。

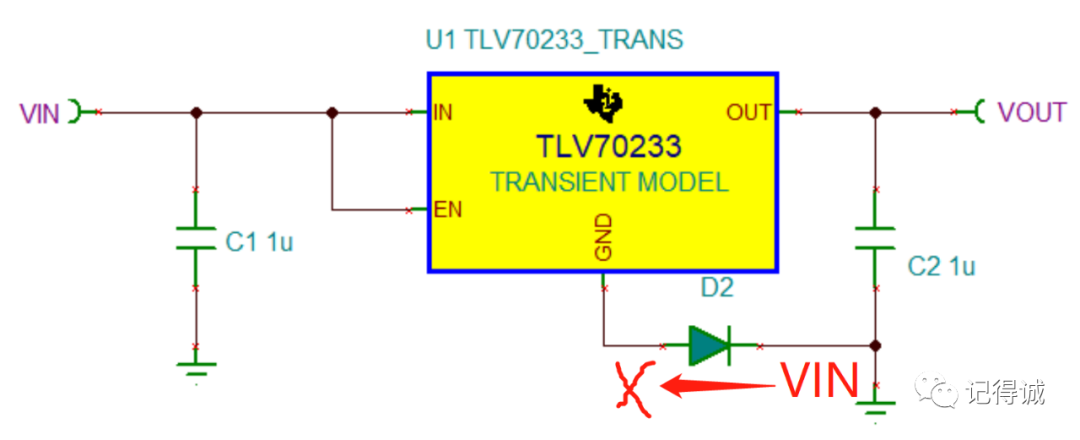

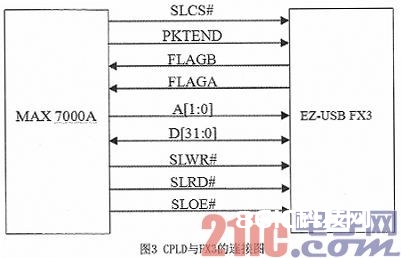

美国硅谷的Altera公司一直是立异定制逻辑处理方案的领先者,其开发了业界最先进的FPGA、CPLD和AS%&&&&&%技能,其开发的MAX系列CPLD芯片深受开发者喜欢。只要选用高速的CPLD主控芯片才干充沛发挥USB3.0的5Gbps超宽带宽,为此Altera公司最新高速的MAX7000A系列CPLD为抱负之选,咱们选用了型号为MAX7128AETC100—4的主控芯片,该芯片的具体资料见文献。该芯片首要担任与GPIF II接口相连,完成GPIF II接口作业在SLAVEFIFO形式下向计算机写入数据的逻辑时序操控。EZ—USB FX3的GPIF II接口有HOST主机和SLAV EFIFO两种作业形式,本体系选用SLAVE FIFO作业形式,其与CPLD衔接的原理图如图3所示。

体系作业原理如下:1)A[1:0]为地址挑选位,MAX7000A依据其值挑选对应的Socket;2)D[31:0]为32位的传输数据总线,MAX7000A将需求写入的数据放置在此总线上;3)SLCS为片选芯片,作业时需为低电平来选中EZ-USB FX3芯片;4)PKTEND为包完毕信号,当数据包写满时,该信号有用时,MAX7000A将其打包传送至EZ—USB FX3芯片;5)FLAGA和FLAGB为EZ—USB FX3回来给MAX 7000A的状况标志信号,MAX7000A据此决议是否对EZ—USB FX3进行数据读写;6)SLWR为写使能信号,SLRD为读使能信号,SLOE为输出使能信号。

体系硬件规划中还包含了电源电路、USB接口电路和时钟复位电路等电路的规划,因为篇幅的联系,在此不作介绍。

2 体系软件规划

体系软件的开发包含了MAX 7000A CPLD和EZ—USB FX3的固件程序开发、EZ—USB FX3的Windows驱动程序开发和上位机应用程序的开发。咱们使用CYPRESS公司供给的开发包,大大缩短了开发周期,提高了开发功率。

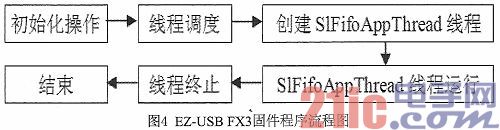

固件程序是微操控器体系的中心,是协助设备完成相应的功用。MAX 7000A CPLD固件程序首要完成对A/D芯片的操控和对EZ—USB FX3芯片的通讯,其将A/D芯片收集的数据传送给EZ—USB FX3。MAX 7000A CPLD的固件开发比较简略,只需对相应的引脚和时序进行界说。为此咱们选用了Verilog HDL言语编写,开发环境为Quartos II 8.0。EZ—USBFX3固件程序的首要功用是让其将MAX 7000A CPLD芯片传来的数据传输到上位机,完成超高速数据传输。EZ—USB FX3的操控器是依据ARM926EJS的,固件程序选用ECLIPSE集成开发环境,开发人员需在CYPRESS公司官网上下载其SDK安装包。EZ—USB FX3的固件程序流程图如下:

S1FifoAppThread线程代表着EZ—USB FX3芯片的GPIF II接口作业在SLAVE FIFO形式。咱们需在S1FifoAppThread线程中界说一个DMA传输通道,此DMA通道在外部MAX 7000A芯片的操控下,将数据送至指定的输入端点,以供上位机应用程序获取。

在驱动程序开发方面,CYPRESS公司的SDK为EZ-USB FX3供给了通用设备驱动程序CYUSB3.SYS,其不只完全符合WDF(Windows Driver Foundation)标准,还具有兼容USB2.0和USB3.0设备、支撑即插即用和支撑高带宽数据传输等长处。咱们只需依据固件程序中界说的USB设备的VID和PID对通用驱动程序相匹配的CYUSB3.INF文件进行相应的简略修正即可。

在上位机的应用程序的开发方面,CYPRESS公司相同为用户供给了一个个操作简略、功用强壮的C++编程接口:CyAPI.Lib库函数。咱们选用了Microsoft Visual Studio2008作为开发工具,经过CyAPI.Lib函数与CYUSB3.SYS设备驱动程序传递数据,进行实时收集。

3 总结

本文具体介绍了选用EZ—USB FX3为接口USB3.0芯片,MAX 7000A为主控芯片,规划与开发了一套USB 3.0数据收集传输体系。CYPRESS公司为EZ-USB FX3供给了完好的SDK开发包,缩短了开发周期。当采样数据为32位,采样时钟为40MHz时,体系理论传输带宽可达1.28Gps。实践测验中咱们选用了16位的A/D高速芯片,MAX 7000A芯片作业时钟为40MHz,试验测得体系传输速率约600Mbps,超过了USB2.0的480Mbps理论带宽,这表明USB3.0总线能将收集的信号实时传输至计算机,充沛发挥了USB3.0超高速传输带宽的优势。