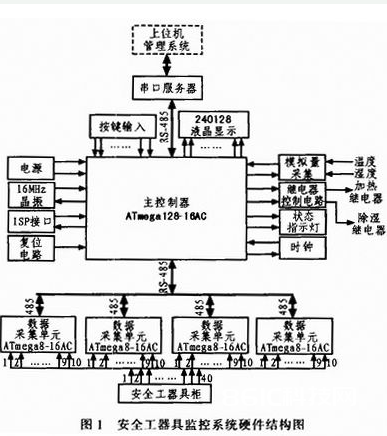

AVR单片机的监控系统设计方案-本文所设计的安全工器具监控系统主要分为下位机数据采集和上位机数据管理两个部分,两者之间通过网络进行通信。

系统首先通过数据采集板对安全工器具柜的相关量进行采集,然后将采集得到的数据进行相应处理后经串口服务器传递给上位机管理系统,上位机获得数据后进行相应处理。

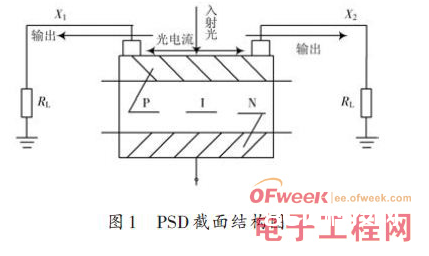

基于Atmega16单片机的PSD数据采集控制电路设计-PSD作为一种精密的光电位置传感器,具有灵敏度高、响应时间短、位置分辨率高、光谱响应范围大等特点,因此被广泛应用于现代光电检测技术中,尤其是高精度、高速度的数据采集技术中。

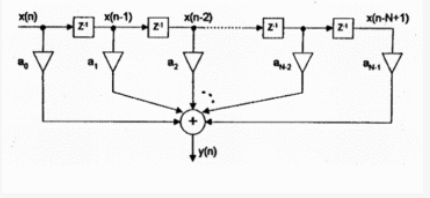

基于单片机和C语言对数字滤波系统的设计-数据采集,又称数据获取,是利用一种装置,从系统外部采集数据并输入到系统内部的一个接口。数据采集技术广泛引用在各个领域。比如摄像头,麦克风,都是数据采集工具。被采集数据是已被转换为电讯号的各种物理量,如温度、水位、风速、压力等,可以是模拟量,也可以是数字量。

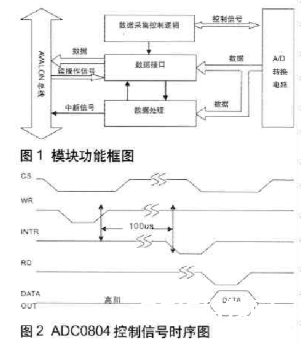

基于NIOS处理器实现A/D数据采集电路的控制接口逻辑设计-在FPGA系统中,实现对外部A/D数据采集电路的控制接口逻辑,由于其逻辑功能不是很复杂,因此可采用自定义的方式。采用这种方法进行设计有两种途径。①从软件上去实现。这种方案将NIOS处理器作为一个主控制器,通过编写程序来控制数据转换电路。由于NIOS处理器的工作频率相对于外部设备来说要高出许多,故此种方法会造成CPU资源极大的浪费;②用FPGA 的逻辑资源来实现A/D采集电路的控制逻辑。FPGA有着丰富的逻辑资源和接口资源,在其中实现并行的数据采集很少会受到硬件资源的限制,在功能上,设计的接口控制逻辑相当于一个主控制器,它是针对具体的外部电路而实现的,容易满足要求、又能节约资源,提高系统性能。因此,采用硬件逻辑去实现控制将是一种较好的方式。

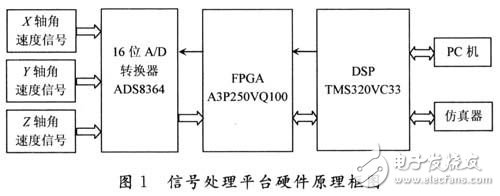

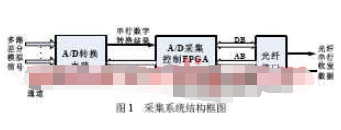

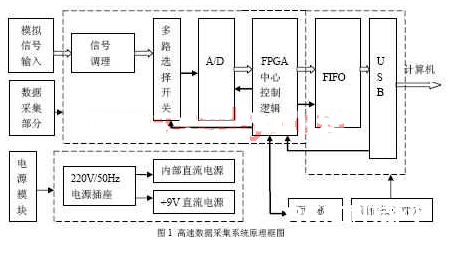

采用FPGA器件控制ADC和数据传输实现数据采集系统的设计-数据采集系统是计算机测控系统中不可或缺的组成部分,是影响测控系统的精度等性能指标的关键因素之一。常用数据采集方案是以微处理器为核心控制多个通道的信号采集、预处理、存储和传输,即用软件实现数据的采集,这在一定程度上局限了数据采集的速度、效率及时序的精确控制。

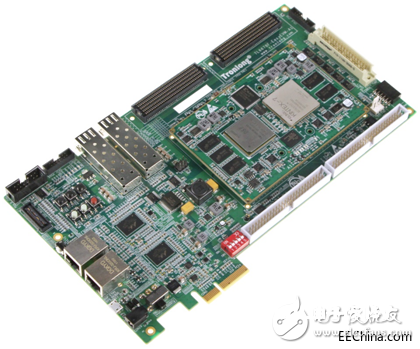

基于DSP+FPGA实现的TL6678F-EasyEVM开发板的介绍-创龙结合TI KeyStone系列多核架构TMS320C6678及Xilinx Kintex-7系列FPGA设计的TL6678F-EasyEVM开发板是一款DSP+FPGA高速大数据采集处理平台,其底板采用沉金无铅工艺的8层板设计,适用于雷达声纳、视频通信系统、电力采集、光缆普查仪、医用仪器、机器视觉等高速数据采集和处理领域。核心板在内部通过I2C、EMIF16、SRIO通信接口将DSP与FPGA结合在一起,组成DSP+FPGA架构,实现了需求独特、灵活、功能强大的DSP+FPGA高速数据采集处理系统。

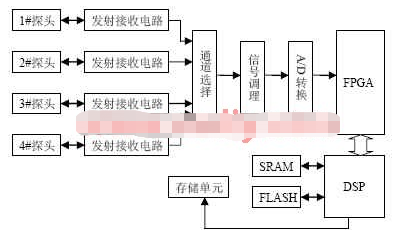

基于EPF20K300EQC240-1和TMS320VC5402实现新型超声探伤系统的设计-本文将FPGA技术和DSP单片系统设计技术结合起来,设计了一种新型四通道超声探伤数据采集处理系统,由FPGA配合DSP并行地进行数据采集、处理和存储工作,较好地解决了系统体积、功耗和处理速度等方面的矛盾。

基于Altera的FPGA器件和VHDL语言实现数据采集系统的设计-传统的数据采集系统,通常采用单片机或DSP作为主要控制模块,控制ADC、存储器和其他外围电路的工作。随着数据采集对速度性能的要求越来越高,传统采集系统的弊端就越来越明显。单片机的时钟频率较低且需用软件实现数据采集,这使得采集速度和效率降低,此外软件运行时间在整个采样时间中也占很大的比例。

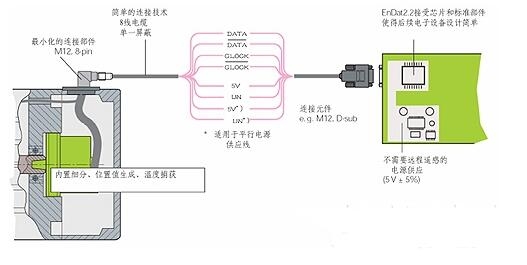

基于FPGA的EnDat接口编码器数据采集设计-EnDat接口是HEIDENHAIN专为编码器设计的数字式、全双工同步串行的数据传输协议,具有传输速度快、功能强大、连线简单、抗干扰能力强等优点,是编码器、光栅尺数据传输的通用接口。本文阐述了EnDat接口的特点、功能、时序和数据传输、OEM数据存储,同时介绍了编码器数据采集后续电路设计方案、基于FPGA模块设计的原理和原则。