与分立器材比较,现代集成运算扩大器 (op amp)和外表扩大器

(op amp)和外表扩大器 (in-amp)为规划工程师带来了许多优点。尽管供给了许多奇妙、有用而且吸引人的电路。往往都是这样,由于匆促地拼装电路而会忽视了一些十分根本的问题,然后导致电路不能完成预期功用 – 或许或许根本不作业。本文将评论一些最常见的运用问题,并给出有用的解决计划。

(in-amp)为规划工程师带来了许多优点。尽管供给了许多奇妙、有用而且吸引人的电路。往往都是这样,由于匆促地拼装电路而会忽视了一些十分根本的问题,然后导致电路不能完成预期功用 – 或许或许根本不作业。本文将评论一些最常见的运用问题,并给出有用的解决计划。

AC耦合时短少DC偏置电流回路

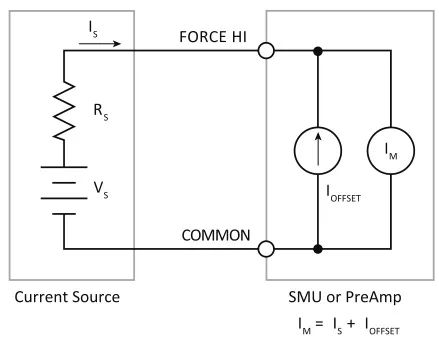

最常遇到的一个运用问题是在沟通(AC)耦合运算扩大器 或外表扩大器

或外表扩大器 电路中没有供给偏置电流的直流(DC)回路。在图1中,一只电容器与运算扩大器

电路中没有供给偏置电流的直流(DC)回路。在图1中,一只电容器与运算扩大器 的同相输入端串联以完成AC耦合,这是一种阻隔输入电压(VIN)的DC重量的简略办法。这在高增益运用中特别有用,在那些运用中哪怕运算扩大器输入端很小的直流电压都会约束动态规模,乃至导致输出饱满。可是,在高阻抗输入端加电容耦合,而不为同相输入端的电流供给DC通路,会呈现问题。

的同相输入端串联以完成AC耦合,这是一种阻隔输入电压(VIN)的DC重量的简略办法。这在高增益运用中特别有用,在那些运用中哪怕运算扩大器输入端很小的直流电压都会约束动态规模,乃至导致输出饱满。可是,在高阻抗输入端加电容耦合,而不为同相输入端的电流供给DC通路,会呈现问题。

图1.过错的运算扩大器AC耦合输入

实践上,输入偏置电流会流入耦合的电容器,并为它充电,直到超越扩大器输入电路的共模电压的额定值或使输出到达极限。依据输入偏置电流的极性,电容器会充电到电源的正电压或负电压。扩大器的闭环DC增益扩大偏置电压。

这个进程或许会需求很长时刻。例如,一只场效应管(FET)输入扩大器,当1 pA的偏置电流与一个0.1μF电容器耦合时,其充电速率I/C为10–12/10–7=10 μV/s,或每分钟600μV。假如增益为100,那么输出漂移为每分钟0.06 V。因而,一般实验室测验(运用AC耦合示波器)无法检测到这个问题,而电路在数小时之后才会呈现问题。明显,完全避免这个问题十分重要。

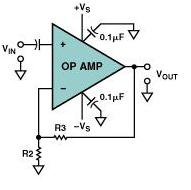

图2.正确的双电源供电运算扩大器AC耦合输入办法

图2示出了对这常见问题的一种简略的解决计划。这儿,在运算扩大器输入端和地之直接一只电阻器,为输入偏置电流供给一个对地回路。为了使输入偏置电流形成的失调电压最小,当运用双极性运算扩大器时,应该使其两个输入端的偏置电流持平,所以一般应将R1的电阻值设置成等于R2和R3的并联阻值。

可是,应该留意的是,该电阻器R1总会在电路中引进一些噪声,因而要在电路输入阻抗、输入耦合电容器的尺度和电阻器引起的Johnson噪声之间进行折衷。典型的电阻器阻值一般在100,000Ω ~1 MΩ之间。

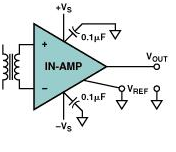

相似的问题也会呈现在外表扩大器电路中。图3示出了运用两只电容器进行AC耦合的外表扩大器电路,没有供给输入偏置电流的回来途径。这个问题在运用双电源(图3a)和单电源(图3b)供电的外表扩大器电路中很常见。

图3.不作业的AC耦合外表扩大器实例

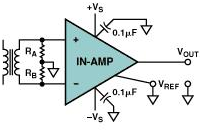

这类问题也会呈现在变压器耦合扩大器电路中,如图4所示,假如变压器次级电路中没有供给DC对地回路,该问题就会呈现。

图4.不作业的变压器耦合外表扩大器电路

图5和图6示出了这些电路的简略解决计划。这儿,在每一个输入端和地之间都接一个高阻值的电阻器(RA,BR)。这是一种适宜双电源外表扩大器电路的简略而有用的解决计划。

图5.每个输入端与地之间都接一个高阻值的电阻器以供给必需的偏置电流回路。

a.双电源. b.单电源.

这两只电阻器为输入偏置电流供给了一个放电回路。在图5所示的双电源比如中,两个输入端的参阅端都接地。在图5b所示的单电源比如中,两个输入端的参阅端或许接地(VCM接地)或许接一个偏置电压,一般为最大输入电压的一半。

相同的准则也能够运用到变压器耦合输入电路(见图6),除非变压器的次级有中心抽头,它能够接地或接VCM。

在该电路中,由于两只输入电阻器之间的失配和(或)两头输入偏置电流的失配会发生一个小的失调电压差错。为了使失调差错最小,在外表扩大器的两个输入端之间能够再接一只电阻器(即桥接在两只电阻器之间),其阻值大约为前两只电阻器的1/10(但与差分源阻抗比较依然很大)。

图6.正确的外表扩大器变压器输入耦合办法

为外表扩大器、运算扩大器和ADC供给参阅电压

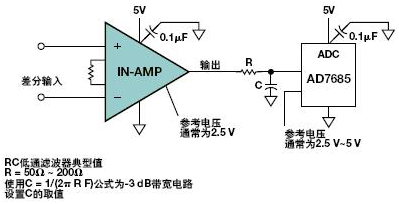

图7示出一个外表扩大器驱动一个单端输入的模数转换器(ADC)的单电源电路。该扩大器的参阅电压供给一个对应零差分输入时的偏置电压,而ADC的参阅电压则供给份额因子。在外表扩大器的输出端和ADC的输入端之间一般接一个简略的RC低通抗混叠滤波器以削减带外噪声。规划工程师一般总想选用简略的办法,例如电阻分压器,为外表扩大器和ADC供给参阅电压。因而在运用某些外表扩大器时,会发生差错。

图7.外表扩大器驱动ADC的典型单电源电路

正确地供给外表扩大器的参阅电压

一般假定外表扩大器的参阅输入端为高阻抗,由于它是一个输入端。所以使规划工程师一般总想在外表扩大器的参阅端引脚接入一个高阻抗源,例如一只电阻分压器。这在某些类型外表扩大器的运用中会发生严峻差错(见图8)。

图8.过错地运用一个简略的电阻分压器直接驱动3运放外表扩大器的参阅电压引脚

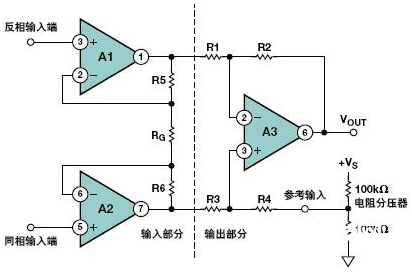

例如,盛行的外表扩大器规划装备运用上图所示的三运放结构。其信号总增益为

参阅电压输入端的增益为1(假如从低阻抗电压源输入)。可是,在上图所示的电路中,外表扩大器的参阅输入端引脚直接与一个简略的分压器相连。这会改动减法器电路的对称性和分压器的分压比。这还会下降外表扩大器的共模按捺比及其增益精度。可是,假如接入R4,那么该电阻的等效电阻会变小,减小的电阻值等于从分压器的两个并联支路看过去的阻值(50 kΩ),该电路表现为一个巨细为电源电压一半的低阻抗电压源被加在原值R4上,减法器电路的精度坚持不变。

假如外表扩大器选用关闭的单封装方式(一个IC),则不能运用这种办法。此外,还要考虑分压电阻器的温度系数应该与R4和减法器中的电阻器坚持一致。终究,参阅电压将不可调。另一方面,假如测验减小分压电阻器的阻值使添加的电阻巨细可疏忽,这样会增大电源电流的耗费和电路的功耗。在任何状况下,这种蠢笨的办法都不是好的规划计划。

图9示出了一个更好的解决计划,在分压器和外表扩大器参阅电压输入端之间加一个低功耗运算扩大器缓冲器。这会消除阻抗匹配和温度系数匹配的问题,而且很简略对参阅电压进行调理。

图9.运用低输出阻抗运算扩大器驱动外表扩大器的参阅电压输入端

当从电源电压运用分压器为扩大器供给参阅电压时应确保PSR功能

一个常常忽视的问题是电源电压VS的任何噪声、瞬变或漂移都会经过参阅输入依照分压比经过衰减后直接加在输出端。实践的解决计划包括旁路滤波以及乃至运用精细参阅电压IC发生的参阅电压,例如ADR121,替代VS分压。

当规划带有外表扩大器和运算扩大器的电路时,这方面的考虑很重要。电源电压按捺技能用来阻隔扩大器免受其电源电压中的沟通声、噪声和任何瞬态电压改变的影响。这是十分重要的,由于许多实践电路都包括、连接着或存在于只能供给非抱负的电源电压的环境之中。别的电力线中的沟通信号会反应到电路中被扩大,而且在恰当的条件下会引起寄生振动。

现代的运算扩大器和外表扩大器都供给频率适当低的电源电压按捺(PSR)才能作为其规划的一部分。这在大多数工程师看来是天经地义的。许多现代的运算扩大器和外表扩大器的PSR目标在80~100dB以上,能够将电源电压的改变影响衰减到1/10,000~1/100,000。乃至最适度的40 dB PSR的扩大器阻隔对电源也能够起到1/100的按捺效果。不过,总是需求高频旁路电容(正如图1~7所示)而且常常起到重要效果。

此外,当规划工程师选用简略的电源电压电阻分压器而且用一只运算扩大器缓冲器为外表扩大器供给参阅电压时,电源电压中的任何改变都会经过该电路不经衰减直接进入外表扩大器的输出级。因而,除非供给低通滤波器,不然IC一般优秀的PSR功能会丢掉。

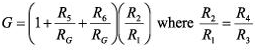

在图10中,在分压器的输出端添加一个大电容器以滤除电源电压的改变而且确保PSR功能。滤波器的-3 dB极点由电阻器R1/R2并联和电容器C1决议。-3 dB极点应当设置在最低有用频率的1/10处。

图10.确保PSR功能的参阅端退耦电路

上面示出的CF试用值能够供给大约0.03 Hz的–3 dB极点频率。接在R3两头的小电容器(0.01 μF)可使电阻器噪声最小。

该滤波器充电需求时刻。依照试用值,参阅输入的上升时刻应是时刻常数的几倍(这儿T=R3Cf= 5 s),或10~15s。

图11中的电路做了进一步改善。这儿,运算扩大器缓冲器起到一个有源滤波器的效果,它答应运用电容值小许多的电容器对相同大的电源退耦。此外,有源滤波器能够用来进步Q值然后加速导通时刻。

图11.将运算扩大器缓冲器接成有源滤波器驱动外表扩大器的参阅输入引脚

测验成果:运用上图所示的元件值,施加12 V电源电压,对外表扩大器的6 V参阅电压供给滤波。将外表扩大器的增益设置为1,选用频率改变的1 VP-P正弦信号调制12 V电源。在这样的条件下,跟着频率的减小,一向减到大约8 Hz时,咱们在示波器上看不到AC信号。当对外表扩大器施加低起伏输入信号时,该电路的测验电源电压规模是4 V到25 V以上。电路的导通时刻大约为2 s。

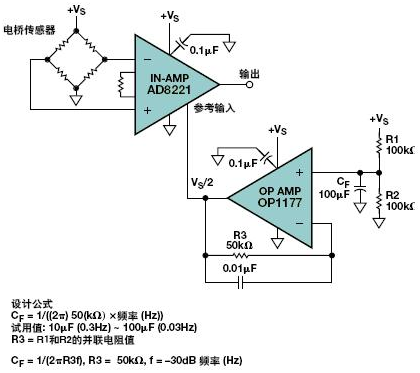

单电源运算扩大器电路的退耦

最终,单电源运算扩大器电路需求偏置共模输入电压起伏以操控AC信号的正向摆幅和负向摆幅。当从电源电压运用分压器供给偏置电压时,为了确保PSR的功能就需求适宜的退耦。

一种常用但不正确的办法是运用100 kΩ/100 kΩ电阻分压器(加0.1μF旁路电容)供给VS/2给运算扩大器的同相输入端。运用这样小的电容值对电源退耦一般是不行的,由于极点仅为32 Hz。电路呈现不稳定(“低频振动”),特别是在驱动理性负载时。

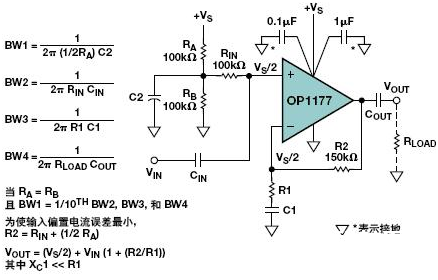

图12(反相输入)和图13(同相输入)示出了到达最佳退耦成果的VS/2偏置电路。在两种状况中,偏置电压加在同相输入端,反应到反向输入端以确保相同的偏置电压,而且单位DC增益也要偏置相同的输出电压。耦合电容器C1使低频增益从BW3降到单位增益。

图12.单电源同相输入扩大器电路正确的电源退耦计划。中频增益=1+R2/R1

如上图所示,当选用100 kΩ/100 kΩ电阻分压器时一个好的经历是,为取得0.3 Hz的–3 dB截止频率,应当选用的C2最小为10 ΩF,。而100 μF(0.03 Hz)实践上对一切电路都足够了。

图13.单电源反相输入扩大器正确的退耦电路,中频增益= – R2/R1