第一个差异当然是姓名:

SPI(Serial Peripheral Interface:串行外设接口);

I2C(INTER IC BUS)

UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)

第二,差异在电气信号线上:

SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。SPI总线可以完结 多个SPI设备相互衔接。供给SPI串行时钟的SPI设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。主从设备间可以完结全双工通讯,当有多个从设备时,还可以添加一条从设备挑选线。

假如用通用IO口模仿SPI总线,有必要要有一个输出口(SDO),一个输进口(SDI),另一个口则视完结的设备类型而定,假如要完结主从设备,则需输入输出口,若只完结主设备,则需输出口即可,若只完结从设备,则只需输进口即可。

I2C总线是双向、两线(SCL、SDA)、串行、多主控(multi-master)接口标准,具有总线裁定机制,十分适合在器材之间进行近距离、非经常性的数据通讯。在它的协议系统中,传输数据时都会带上意图设备的设备地址,因而可以完结设备组网。

假如用通用IO口模仿I2C总线,并完结双向传输,则需一个输入输出口(SDA),别的还需一个输出口(SCL)。(注:I2C材料了解得比较少,这儿的描绘或许很不齐备)

UART总线是异步串口,因而一般比前两种同步串口的结构要杂乱许多,一般由波特率发生器(发生的波特率等于传输波特率的16倍)、UART接纳器、UART发送器组成,硬件上由两根线,一根用于发送,一根用于接纳。

显着,假如用通用IO口模仿UART总线,则需一个输进口,一个输出口。

第三,从第二点显着可以看出,SPI和UART可以完结全双工,但I2C不可;

第四,看看牛人们的定见吧!

wudanyu:I2C线更少,我觉得比UART、SPI更为强壮,可是技术上也愈加费事些,由于I2C需求有双向IO的支撑,并且使用上拉电阻,我觉得抗干扰才能较弱,一般用于同一板卡上芯片之间的通讯,较少用于远距离通讯。SPI完结要简略一些,UART需求固定的波特率,就是说两位数据的距离要持平,而SPI则无所谓,由于它是有时钟的协议。

quickmouse:I2C的速度比SPI慢一点,协议比SPI杂乱一点,可是连线也比标准的SPI要少。

posted @2009-02-22 23:00陈广强 阅览(185) |谈论(0)| 修改

SPI总线

SPI总线简介

|

同步外设接口(SPI)是由摩托罗拉公司开发的全双工同步串行总线,该总线很多用在与EEPROM、ADC、FRAM和显现驱动器之类的慢速外设器材通讯。

SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备发动一个与从设备的同步通讯,然后完结数据的交流。SPI 接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(从使能信号)四种信号构成,CS 决议了仅有的与主设备通讯的从设备,如没有CS 信号,则只能存在一个从设备,主设备经过发生移位时钟来建议通讯。通讯时,数据由SDO 输出,SDI 输入,数据在时钟的上升或下降沿由SDO 输出,在紧接着的下降或上升沿由SDI 读入,这样经过8/16 次时钟的改动,完结8/16 位数据的传输。

SPI通讯

该总线通讯依据主-从装备。它有以下4个信号:

MOSI:主出/从入

MISO:主入/从出

SCK:串行时钟

SS:隶属挑选

芯片上“隶属挑选”(slave-select)的引脚数决议了可连到总线上的器材数量。

在SPI传输中,数据是同步进行发送和接纳的。数据传输的时钟依据来自主处理器的时钟脉冲,摩托罗拉没有界说任何通用SPI的时钟标准。但是,最常用的时钟设置依据时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL界说SPI串行时钟的活动状况,而CPHA界说相对于SO-数据位的时钟相位。CPOL和CPHA的设置决议了数据取样的时钟沿。

数据方向和通讯速度

SPI传输串行数据时首要传输最高位。波特率可以高达5Mbps,详细速度巨细取决于SPI硬件。例如,Xicor公司的SPI串行器材传输速度能到达5MHz。

SPI总线接口及时序

SPI总线包含1根串行同步时钟信号线以及2根数据线。

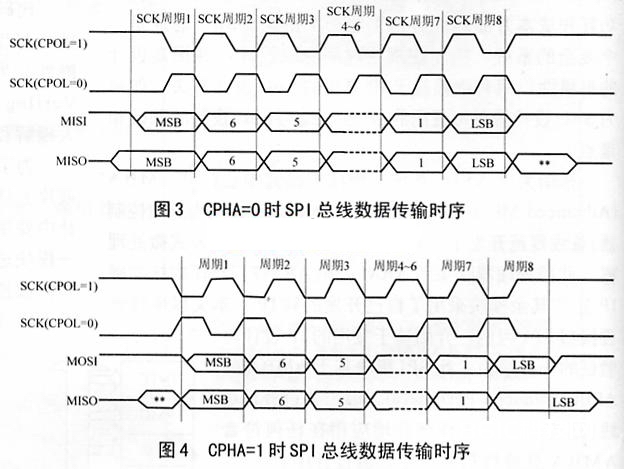

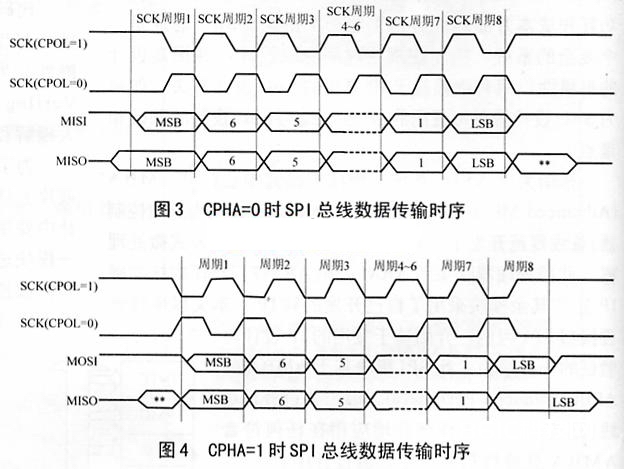

SPI模块为了和外设进行数据交流,依据外设作业要求,其输出串行同步时钟极性和相位可以进行装备,时钟极性(CPOL)对传输协议没有严重的影响。假如CPOL=0,串行同步时钟的闲暇状况为低电平;假如CPOL=1,串行同步时钟的闲暇状况为高电平。时钟相位(CPHA)可以装备用于挑选两种不同的传输协议之一进行数据传输。假如CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;假如CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通讯的外设备时钟相位和极性应该共同。SPI主模块和与之通讯的外设备时钟相位和极性应该共同。个人了解这句话有2层意思:其一,主设备SPI时钟和极性的装备应该由外设来决议;其二,二者的装备应该保持共同,即主设备的SDO同从设备的SDO装备共同,主设备的SDI同从设备的SDI装备共同。由于主从设备是在SCLK的操控下,一起发送和接纳数据,并经过2个双向移位寄存器来交流数据。SPI接口时序如图3、图4所示。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简略,主要是在sck的操控下,两个双向移位寄存器进行数据交流。

假定下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接纳、高位先发送。

那么第一个上升沿来的时分数据将会是sdo=1;寄存器=0101010x。下降沿到来的时分,sdi上的电平将所存到寄存器中去,那么这时寄存器=0101010sdi,这样在8个时钟脉冲今后,两个寄存器的内容相互交流一次。这样就完结里一个spi时序。

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/changshang/jieda/256067.html

|