3.1时钟体系介绍

UCS模块支撑低功耗。它内部含有三个时钟信号,用户能够自行挑选,找到功用和功耗的平衡点。UCS软件

装备后,只需求一两个晶振或许电阻,而不需求运用外部振动器。

UCS模块最多含有5个时钟源:

l

4MHZ~32MHZ时钟。

l

l

l

l

UCS模块有三个时钟信号(/体系)能够运用:

l

(假如能够用)。DCOCLKDIV为DCOCLK 在 FLL 模块中经过 1、2、4、8、19、32 分频后得到的频率。

ACLK 可由软件位作各个外围模块的时钟信号。ACLK 经 1、2、4、8、16、32 分频。ACLK/n是 ACLK

经1、2、4、8、16、32分频后作为外部电路运用。

l

XT2CLK(假如能够用)。DCOCLKDIV 为 DCOCLK 在 FLL 模块中经过 1、2、4、8、19、32 分频后得

到的频率。MCLK 能够经过1、2、4、8、16、32分频。MCLK 作为 CPU和体系时钟。

l

DCOCLKDIV,XT2CLK(假如能够用)。DCOCLKDIV为 DCOCLK 在 FLL模块中经过 1、2、4、8、19、

32分频后得到的频率。SMCLK 能够经过 1、2、4、8、16、32 分频。SMCLK 首要用于高速外围模块。

体系经过适宜的装备能够作为外部器材的时钟输入源。UCS模块图如下图所示:

MSP430学习笔记之二:时钟模块

MSP430系列单片机根底时钟首要是由低频晶体振动器,高频晶体振动器,数字操控振动器(DCO),锁频环(FLL)及FLL+等模块构成。因为430系列单片机中的类型不同,而时钟模块也将有所不同。尽管不同类型的单片机的时基模块有所不同,但这些模块产生出来的成果是相同的.在MSP430F13、14中是有TX2振动器的,而MSP430F11X,F11X1中是用LFXT1CLK来替代XT2CLK时钟信号的.在时钟模块中有3个(关于F13,F14)时钟信号源(或2个时钟信号源,关于F11X、F11X1):

1-LFXT1CLK: 低频/高频时钟源.由外接晶体振动器,而无需外接两个振动电容器.较常运用的晶体振动器是32768HZ。

2-XT2CLK: 高频时钟源.由外接晶体振动器。需求外接两个振动电容器,较常用的晶体振动器是8MHZ。

3-DCOCLK: 数字可操控的RC振动器。

1-ACLK: 辅佐时钟信号.由图所示,ACLK是从FLXT1CLK信号由1/2/4/8分频器分频后所得到的.由BCSCTL1寄存器设置DIVA相应为来决议分频因子.ACLK可用于供给CPU外围功用模块作时钟信号运用.

2-MCLK: 主时钟信号.由图所示,MCLK是由3个时钟源所供给的。他们分别是LFXT1CLK,XT2CLK(F13、F14,假如是F11,F11X1则由LFXT1CLK替代),DCO时钟源信号供给.MCLK首要用于MCU和相关体系模块作时钟运用。相同可设置相关寄存器来决议分频因子及相关的设置。

3-SMCLK: 子体系时钟,SMCLK是由2个时钟源信号所供给.他们分别是XT2CLK(F13、F14)和DCO,假如是F11、F11X1则由LFXT1CLK替代TX2CLK。相同可设置相关寄存器来决议分频因子及相关的设置。

MSP430X1X1系列产品中,其间XT1时钟源引脚接法有如3种运用。F13、14的XT1相同。需求留意的是,LFXT1只要作业在高频形式下才需求外接电容。

对以引脚较少的MSPX1XX系列产品中有着不一起基模块,详细如下:

MSP430X11X1:LFXT1CLK , DCO

MSP430F12X: LFXT1CLK , DCO

MSP430F13X/14X/15X/16X:LFXT1CLK , DCO , XT2CLK

MSP430F4XX: LFXT1CLK , DCO , XT2CLK , FLL+

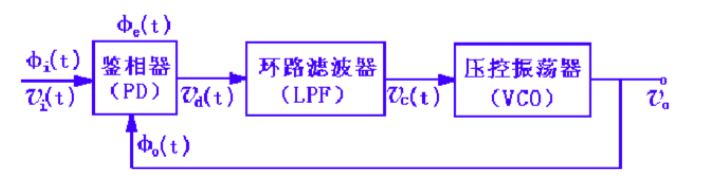

时钟产生器的原理阐明:问题的提出:1、高频、以便能对体系硬件恳求和事情作出快速呼应 2、低频率,以便将电流耗费降制至最少 3、安稳的频率,以满意定时器的运用。 4、低Q值振动器,以确保开端或中止操作没有延时MSP430选用了一个折衷的办法:便是用一个低频晶镇振,将其倍频在高频的作业频率上。一般选用这种技能的有用办法有两种,一个是说、锁相环、一个是锁频环,而锁相环选用模仿的操控简单引起“失锁”和易引起电容量的改动。而TI选用的是锁频环技能,它选用数字操控器DCO和频率积分来产生高频的运转时钟频率。

低功耗设置的技巧问题: 1、LPM4:在振动器封闭形式期间,处理机的一切部件作业中止,此刻电流耗费最小。此刻只要在体系上电电路检测到低点电平或任一恳求异步呼应中止的外部中止事情时才会重新作业。因此在规划上应含有或许需求用到的外部中止才选用这种形式。不然产生不行意料的成果。 2、LPM3:在DC产生器封闭期间,只要晶振是活动的。但此刻设置的根本时序条件的DC产生器的DC电流被封闭。因为此电路的高阻规划,使功耗被按捺。注:当从DC封闭到发动DC0要花一端时刻(ns-us) 3、LPM2:在此期间,晶镇振和DC产生器是作业的,所以可完成快速发动。4、LPM1:在此振动器现已作业,所以不存在发动时刻延时问题。结合上述特色,在写程序时要归纳考虑低功好耗特性,对外部事情的组织也很重要。你有必要在功用完成上归纳考虑才干到达你预期的作用。运用C言语可用如下的句子:_BIS_SR(LMP3_bits)和_BIC_SR(LPM3 bits) LPM3和LPM3_EXIT 它们的界说是相同的。这儿阐明在C言语环境中有些界说的函数是不行见的。但你能够从in430.h文件看到它们的界说。

DCOCTL DCO操控寄存器

DCO.2 DCO.1 DCO.0 MOD.4 MOD.3 MOD.2 MOD.1 MOD.0

DCO.0-DCO.4 界说8种频率之一,能够分段调理DCOCLK频率,相邻两种频率相差10%。而频率由注入直流产生器的电流界说。

MOD.0-MOD.4 界说在32个DCO周期中刺进的Fdco+1周期个数,而鄙人的DCO周期中为Fdco周期,操控转换DCO和DCO+1挑选的两种频率。假如DCO常数为7,表明现已挑选最高频率,此刻不能使用MOD.0-MOD.4进行频率调整。

BCSCTL1 根本时钟体系操控寄存器1

XT2OFF TXS DIVA.1 DIVA.0 XT5V Rsel.2 Resl.1 Resl.0

XT2OFF 操控XT2振动器的敞开与封闭。

TX2OFF=0,XT2振动器敞开。

TX2OFF=1,TX2振动器封闭(默以为TX2封闭)

XTS 操控LFXT1 作业形式,挑选需结合实际晶体振动器衔接状况。

XTS=0,LFXT1 作业在低频形式(默许)。

XTS=1,LFXT1 作业在高频形式(有必要衔接有高频相应的高频时钟源)。

DIVA.0 DIVA.1 操控ACLK分频。

0 不分频(默许)

1 2分频

2 4分频

3 8分频

XT5V 此位设置为0。

Resl1.0,Resl1.1,Resl1.2 三位操控某个内部电阻以决议标称频率。

Resl=0,挑选最低的标称频率。

……..

Resl=7,挑选最高的标称频率。

BCSCTL2 根本时钟体系操控寄存器2

SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR

SELM.1 SELM.0 挑选MCLK时钟源

0 时钟源为DCOCLK(默许)

1 时钟源为DCOCLK

2 时钟源为LFXT1CLK(关于MSP430F11/12X),时钟源为XT2CLK(关于MSP430F13/14/15/16X);

3 时钟源为LFTXTICLK。