预制与定制FPGA式原型板参加协同仿真(co-emulatiON and co-simulation)功用,可以供给高速、高能见度渠道,完成SoC的快速、前期验证。

体系芯片(SoC)规划的规划与复杂度不断地攀升。一起,产品在市场上的存活时刻不断地紧缩,当今的电子市场也关于上市所需的前置时刻十分灵敏。这些全都加深了SoC规划与验证团队的压力。事实上,现在广为承受的说法便是,验证占了全体SoC开发时刻的70%。所以,可以下降验证本钱、加快验证履行以及在开发初期尽早进行验证的作法,都是世人注视的焦点。

这篇文章首要介绍构成典型SoC规划与验证环境的首要要素;也会阐明传统验证处理计划的优缺陷,包含软件仿真、硬件辅佐加快与仿真,还有FPGA式原型板的运用。接着会阐明立异并且价格合理的做法,让规范FPGA式原型板可以改变成为完善的桌上型硬件仿真器。咱们引荐的这种做法是一种模范搬运(paradigm shift),能使既有的硬件仿真 (in-circuit emulation) 功用主动化,并且增加全新协同仿真功用,大幅进步预制与定制规划FPGA式原型板的验证功率。

典型的SoC规划与验证环境

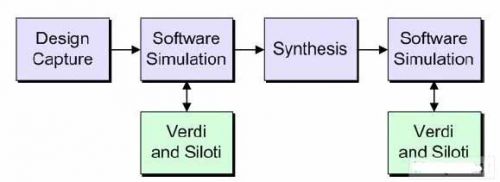

首要,让咱们来看看典型SoC规划与验证环境的前端部分。至少,这包含某些办法的规划输入、软件仿真办法的功用验证,还有逻辑归纳,如图1所示。乃至,这种规划环境现在大多也包含SpringSoft的Verdi?主动化侦错体系。Verdi体系让用户可以剖析自己软件仿真器1的成果并履行侦错,还可以主动使任何门级成果与对应的RTL源代码发生干系。

图1. 简化的SoC前端规划与验证环境。

林林总总功用验证的问题之一,便是要搜集与贮存的数据量。以软件仿真器为例,监督很多信号会大幅拖慢仿真速度,并且冗长的仿真进展又会导致更很多的数据;所以,许多规划与验证环境都运用了SpringSoft的Siloti?能见度主动增强体系,来削减记载规划中许多信号数据的担负。Siloti体系用来找出仿真进行中最低极限有必要记载的信号;然后Siloti体系会运用这些信号,主动且敏捷的发生一切需求但未记载的信号数据。

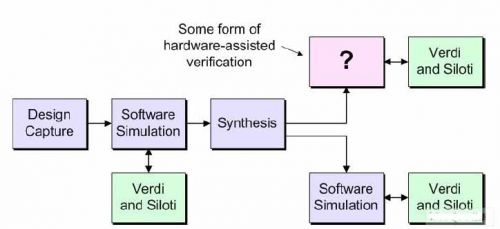

软件仿真的首要优势便是对规划有彻底的能见度;而首要的缺陷便是慢,即便在威力强壮、高阶作业站上履行,并选用Siloti能见度主动增强技能 – 当今大型SoC规划的软件仿真只能牵强到达几Hz的仿真速度 (也便是说,每秒钟只能有几回规划的实时主体系频率周期)。这表明,软件仿真一般仅适用于规划的一小部分,或许适用于全芯片规划的数十个频率周期罢了。可是,彻底验证现代化SoC需求不计其数乃至数百万频率周期,这时就需求某种办法的硬件辅佐验证,如图2所示。

图 2. 简化的SoC前端规划与验证环境,增加某种办法的硬件辅佐验证。

传统的硬件辅佐验证处理计划

各种硬件辅佐验证处理计划具有不同的功用、长处与缺陷。也有许多办法可以运用不同的体系,来处理不同类型的问题;包含硬件仿真(in-circuit emulation) 、买卖级协同仿真以及HDL协同仿真。

一般来说,传统的硬件辅佐验证处理计划仅包含硬件加快器与/或仿真器。FPGA式原型板一般不被视为可行的代替计划,由于缺少与作业站衔接的才能,并且无法供给满足的规划能见度以供侦错运用。

传统的硬件加快与/或仿真体系都是专属体系,运用定制规划的芯片、或规范FPGA,来建构特别意图体系。这些体系的意图是要尽或许好像软件仿真器一般运作,包含能见度与侦错功用等要素。这些体系运用可以驾御其定制芯片或架构的特别软件,供给大型容量与恰当快速的编译时刻,让规划可以映像到硬件上;他们也供给恰当优秀的规划能见度 (可见度与可控准则)。可是,这些体系十分贵重,难以让许多运用者、项目与团队广泛的运用。再者,一旦选用这种体系之后,就很难晋级到新一代的体系;除了新版定制规划芯片与体系需求消耗时刻来开发之外,还有必要考虑昂扬的过渡本钱等其他要素。

搬运到FPGA式原型板

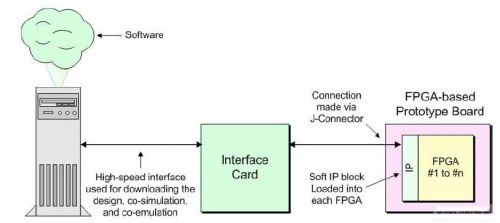

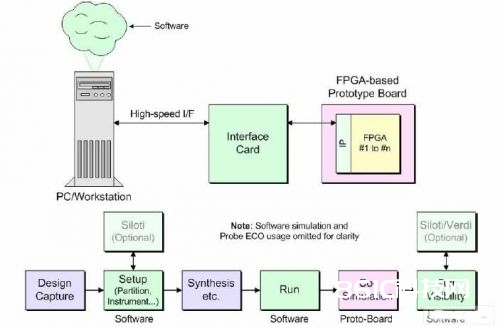

作为硬件加快器与仿真器的代替计划,许多规划业者运用可以现成购买的,或许由SoC验证团队定制规划FPGA式原型板。如图3的比如,规划在作业站上编译 (归纳) 后;映射、布局与绕线;然后将成果的FPGA配置文件 (或许是体系包含许多FPGA时的文件) 下载到原型板上。典型的运用模型适合于SoC规划 (或部分规划模块)验证时运用硬件仿真(in-circuit emulation)的办法;也便是说,如图3所示,运用实践输入/输出 (I/O) 信号来驱动。除了由外部体系所驱动 – 和带动之外,也可以把握实践的I/O信号以供逻辑剖析器等来进行后续剖析。

图 3. 以硬件仿真(in-circuit emulation)办法运作的传统FPGA式原型板环境的高阶出现。

传统FPGA式原型板的首要优势便是高效能,并且相对而言比较廉价,所以可以让许多运用者、项目与团队广泛的运用。此外,这些原型板可以运用最新一代的FPGA技能,让运用者可以快速而轻松地搬运到新一代原型板。而其首要缺陷便是难以设定,并且无法与作业站衔接以支撑协同仿真 (co-emulation and/or co-simulation)。再加上只能供给极有限的规划能见度,所以缺少精细的侦错功用。

强化传统FPGA式原型板

传统FPGA式原型板一般都装备J-Connector,期望让原型板可以衔接到外埠设备。本文提出的作法便是运用这个J-Connector,树立能与其衔接的特别适配卡,以扮演主机作业站与FPGA式原型板之间的桥梁,如图4所示。

图4. 新增适配卡与某些软IP (soft IP)。

FPGA式原型板与作业站之间的一切通讯都可以运用某些专属总线而建置起来,供给仿真与协同仿真所需的高性能。由于这种互连技能,运用者具有可架构和运用不同原型板以调配同一J-Connector的绝佳弹性。这种才能也表明,运用者可以快速并且容易地搬运到更快速和更巨大的FPGA式原型板,可以彻底革除传统硬件辅佐验证处理计划相关的约束。

接下来看看图4所示的软IP模块 (soft IP)。这些IP模块可下载至原型板上的各FPGA,然后可用来操控和监督FPGA式原型板与作业站之间的数据活动。因操作方式 (硬件仿真、协同仿真) 的不同,可以主动刺进恰当且必要的「特征」IP模块。这些IP模块可以编译到规划中,用来监控用户指定的恣意信号。如此一来,就可以把握和剖析来自数千信号仿真数百万频率周期的数据。

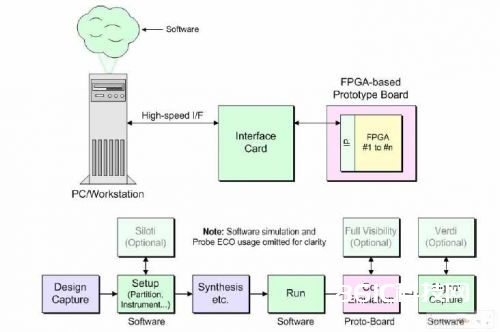

除了互连技能之外,本文的作法也需求如图5所示在作业站上履行的特别软件来履行许多功用,例如主动树立包含多颗FPGA的原型板。这个树立流程包含读取规划的RTL源代码 (以VHDL、Verilog、SySTemVerilog或混合式言语)、剖析FPGA内部与外部的内存、转化SoC频率已发生无hold-time问题的规划在FPGA中运用、切割完好SoC规划的RTL以便放入多颗FPGA,以及调整RTL来调配软IP模块与要监控的信号。

图5. 增加在作业站上履行的特别软件。

在验证途中,软件可以根据树立时指定的操作方式 (硬件仿真、协同仿真),操控和办理FPGA式原型板与作业站之间的通讯与数据活动。别的,能快速修正所监控信号的才能也很重要,这样才可以快速且容易地新增监控的信号,不用重复编译整个规划。最终,便是原型板上FPGA内部情况的能见度,这包含在特定时刻或以逐个频率周期为基准所供给的寄存器 (registers) 与内存输出,在进阶侦错时十分有用。

规划原型的「桌上型」验证

为了更彻底了解因本文所评论互连与软件主动化技能而完成的各种功用与运用方式,让咱们来看一些典范情境。最简略的比如便是图6所示的朴实硬件仿真运用。在桌上型作业站上履行的软件会主动切割规划,并预备原型板。在树立过程中,会在规划中置入一切必要的勘探点,以便在履行时把握特定信号数据。

图6. 硬件仿真情境的典范。

此外,运用者也可以选择性的运用Siloti能见度主动增强体系,来协助判别需求调查的最少信号量。以及运用Verdi主动化侦错体系来剖析FPGA式硬件原型板的成果,并履行侦错。由于树立软件会主动将任何门级信号干系至对应的RTL信号,Verdi体系调配RTL源代码可以加快侦错的进展。

买卖级协同仿真是可以大幅加快验证流程,其速度比仅运用软件仿真要快上数百或数千倍,常见的情况是testbench (或许是规划的一部份) 常驻在作业站上,而很多 (或悉数) 规划被加载到原型板。作业站上履行的软件会主动切割规划,主动树立原型板,然后刺进恰当的协同仿真根底架构 (例如SCEMI式处理设备)。在前述情境中,树立时,一切必要的勘探点都会置入规划中,以便在履行时可以把握特定的信号数据。或许,协同仿真可以暂停,也可以设置软件在特定时刻或依照逐个频率周期,将FPGA内部情况的彻底能见度输出,如图7所示。

图7. 买卖级协同仿真情境的典范。

最终,让咱们看看HDL协同仿真,这种加快验证流程,其速度比单仅运用软件仿真要快上数十倍。同样地,testbench (或许是规划的一部份) 常驻在作业站上,而很多 (或悉数) 规划被加载到原型板。在这个情境中,作业站上履行的软件会主动切割规划,树立原型板,和发生可供软件仿真器衔接的包装器(wrapper)。履行时,软件会操控原型板与ModelSim、NC或VCS等业界规范软件仿真器之间的协同仿真互动。好像前面几个情境中的评论一般,透过软件与FPGA内部技能的组合,可在特定时刻或依照逐个频率周期,将原型板上FPGA内部情况的能见度,包含寄存器与内存输出,如图8所示。

图8. HDL协同仿真情境的典范。

新一代原型验证渠道的长处

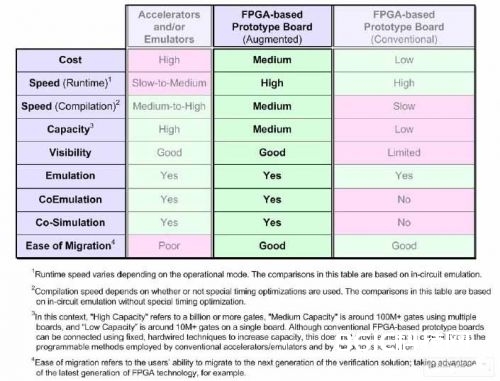

产品在市场上的存活时刻及上市前置时刻不断缩短造成了当今SoC规划与验证团队的极大压力。软件仿真供给对规划内部的100%能见度,可是只适合于规划的一小部分,或许整个规划的数十个频率周期罢了。可是,彻底验证现代SoC需求消耗不计其数乃至百万频率周期,所以需求某种办法的硬件辅佐验证。林林总总的硬件辅佐验证处理计划具有不同的功用、长处与缺点。表1供给了各种硬件辅佐验证技能的大概比较。

传统硬件加快器与仿真器供给大容量、相对快速的编译时刻,以及恰当杰出的规划能见度。可是,这些体系太贵重而难以广泛运用,并且由于搬运本钱昂扬,也难以与时俱进地晋级至新一代处理计划。比较上,传统FPGA式原型板供给高效能,并且比较廉价;可是,缺少规划能见度与精细的侦错功用,无法战胜今世SoC的复杂度,并且一般仅以硬件仿真方式来运用。

表1. 硬件辅佐验证技能的比较。

为了处理这些问题,咱们主张一种SoC验证的新办法,将传统FPGA式原型板改变成桌上型加快器/仿真器。这需求立异的互连技能,可以供给对预制与定制规划板的通用衔接;还有特别化的软件主动化,在作业站上以硬件仿真、协同仿真方式履行,并具有极高的规划能见度。

运用强化上述功用的FPGA式原型板,SoC开发人员可快速验证单个模块 (包含内部与第三方IP模块) 和规划模块是否正常运作,乃至于整个SoC规划的验证。这个新一代原型验证渠道可进步FPGA式原型版的出资报酬率及生产力,供给更高验证功率与弹性,并能快速搬运到装备最新FPGA技能的原型板。