11.3FPGA与DSP的通讯接口规划

FPGA与DSP的通讯接口能够分红以下几种。

·存储型接口,如EMIFA、EMIFB等。

·主机型接口,如HPI等。

·总线型接口,如PCI、EMAC等。

·串口型接口,如McBSP、McASP、SPI、UART等。

·特别类接口,如VLYNQ、VPORT等。

以上的接口中,比较常用的接口是EMIF和HPI。其间总线接口需求协议支撑,开发难度较大,串行接口开发简略,可是速率较慢。VPORT等特别接口一般是在特定的场合下运用,不具有通用性,而且需求修正DSP驱动,开发周期较长。

11.3.1根据TMS320C64x系列的EMIF接口规划

1.EMIF简介

TMSC64xEMIF是TMSC621xEMIF的增强版。它具有TMSC621x/TMSC671xEMIF的一切功用,并添加了以下新功用。

(1)EMIFA上的数据总线能够是64位宽,也能够是32位宽。

(2)EMIFB上的数据总线为16位宽。

(3)EMIF时钟ECLKOUTx为内部生成,并根据EMIF输入时钟。器材复位时,以下3个时钟之一会被装备为EMIF输入时钟。

·内部CPU时钟4分频。

·内部CPU时钟4分频。

·外部ECLKIN与TMSC64xEMIF接口的存储器应依照ECLKOUTx的时钟频率运转。

·可编程同步存储器接口操控器的同步操控引脚替换了固定的SBSRAM操控引脚。

·PDT引脚供给外部到外部传输支撑。

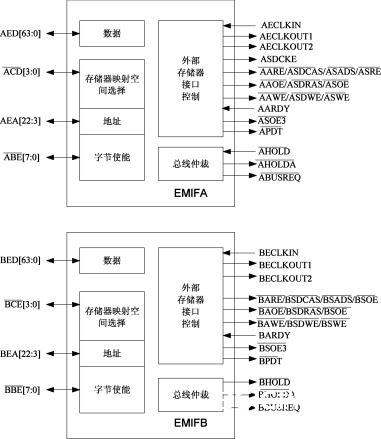

如图11.4所示为组成EMIFA和EMIFB接口的信号,表11.2对这些信号进行了描绘。端口A的信号都带前缀“A”,端口B的信号都带前缀“B”。为便利起见,一切信号称号都省掉了EMIF端口前缀。

EMIFA接口具有与8、16、32或64位体系接口的功用。EMIFB接口端口仅支撑8位和16位体系,如图11.5所示。

外部器材(主要是存储器)一般与总线的ED[7:0]字节侧右对齐。Endianess(字节次序)决议ED[7:0]位是作为字节0(littleendian(小端))仍是字节N(bigendian(大端),其间2N是总线宽度)存取。对不同字节通道的挑选,可经过低有用字节使能信号的运用(如表11.2所示)来完结。

图11.4EMIFA和EMIFB信号

表11.2 EMIF信号描绘

|

引脚 |

I/O/Z |

描绘 |

|

CLKOUT4 |

O/Z |

CPU时钟的4分 |

|

CLKOUT6 |

O/Z |

CPU时钟的6分 |

|

ECLKIN |

I |

EMIF时钟输入 |

|

ECLKOUT1 |

O/Z |

速率为ECLKIN、CPU/4或CPU/6时的EMIF输出时钟 |

|

ECLKOUT2 |

O/Z |

速率为ECLKIN、CLKOUT4或CLKOUT6时的EMIF输出时钟 |

|

ED[63:0] |

I/O/Z |

EMIFA64位数据总线 |

|

ED[31:0] |

I/O/Z |

EMIFA32位数据总线 |

|

ED[15:0] |

I/O/Z |

EMIFB16位数据总线 |

|

EA[22:3] |

O/Z |

EMIFA地址输出 |

|

EA[20:1] |

O/Z |

EMIFB地址输出 |

|

CE0 |

O/Z |

存储器空间0的芯片挑选 |

|

CE1 |

O/Z |

存储器空间1的芯片挑选 |

续表

|

引脚 |

I/O/Z |

描绘 |

|

CE2 |

O/Z |

存储器空间2的芯片挑选 |

|

CE3 |

O/Z |

存储器空间3的芯片挑选 |

|

BE[7:0] |

O/Z |

EMIFA64位字节使能,字节使能仅针对其对应的字节通道有用 如BE[0]对应ED[7:0] |

|

BE[3:0] |

O/Z |

EMIFA32位字节使能,字节使能仅针对其对应的字节通道有用 |

|

BE[1:0] |

O/Z |

EMIFB16位字节使能,字节使能仅针对其对应的字节通道有用 |

|

ARDY |

I |

异步安排妥当输入,低速外设刺进等候状况 |

|

SOE3 |

O/Z |

CE3的同步输出使能 |

|

AOE |

O/Z |

异步输出使能 |

|

SDRAS |

O/Z |

DRAM存储器的行地址选通脉冲 |

|

SOE |

O/Z |

同步输出使能 |

|

ARE |

O/Z |

异步读使能 |

|

SDCAS |

O/Z |

SDRAM存储器的列地址选通脉冲 |

|

SADS/SRE |

O/Z |

同步地址选通脉冲或读使能 |

|

AWE |

O/Z |

异步写选通脉冲 |

|

SDWE |

O/Z |

SDRAM的写使能 |

|

SWE |

O/Z |

同步写使能 |

|

HOLD |

I |

外部总线坚持恳求 |

|

HOLDA |

O |

外部总线坚持承认 |

|

BUSREQ |

O |

总线恳求 |

|

PDT |

O/Z |

外设数据传输 |

|

SDCKE |

O/Z |

SDRAM时钟使能 |

|

CLKOUT4 |

O/Z |

CPU时钟的4分 |

|

CLKOUT6 |

O/Z |

CPU时钟的6分 |

|

ECLKIN |

I |

EMIF时钟输入 |

|

ECLKOUT1 |

O/Z |

速率为ECLKIN、CPU/4或CPU/6时的EMIF输出时钟 |

|

ECLKOUT2 |

O/Z |

速率为ECLKIN、CLKOUT4或CLKOUT6时的EMIF输出时钟 |

|

ED[63:0] |

I/O/Z |

EMIFA64位数据总线14 |

|

ED[31:0] |

I/O/Z |

EMIFA32位数据总线 |

|

ED[15:0] |

I/O/Z |

EMIFB16位数据总线 |

|

EA[22:3] |

O/Z |

EMIFA地址输出 |

续表

|

引脚 |

I/O/Z |

描绘 |

|

EA[20:1] |

O/Z |

EMIFB地址输出 |

|

CE0 |

O/Z |

存储器空间0的芯片挑选 |

|

CE1 |

O/Z |

存储器空间1的芯片挑选 |

|

CE2 |

O/Z |

存储器空间2的芯片挑选 |

|

CE3 |

O/Z |

存储器空间3的芯片挑选 |

|

BE[7:0] |

O/Z |

EMIFA64位字节使能。字节使能仅针对其对应的字节通道有用 |

|

BE[3:0] |

O/Z |

BE7对应ED[63:56] |

|

BE[1:0] |

O/Z |

BE6对应ED[55:48] |

|

ARDY |

I |

BE5对应ED[47:40] |

|

SOE3 |

O/E |

BE4对应ED[39:32] |

|

BE3对应ED[31:24] |

||

|

BE2对应ED[23:16] |

||

|

BE1对应ED[15:8] |

||

|

BE0对应ED[7:0] |

图11.5按Endianess对齐字节

有关EMIF接口及其功用的完好概述,请参阅相关的TI数据手册(tms320c64xx.pdf,其间xx为15t、16t或18)。

2.FPGA的BlockRAM简介

Xilinx架构的FPGA都能够拜访模块存储器(BlockRAM)。Virtex、Virtex-E和Spartan-II器材中的这些4Kbit的模块在Virtex-II、Virtex-IIPro和Spartan-3器材中都增加到18Kbit的模块。

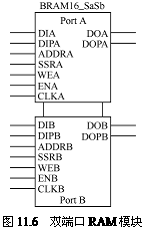

这些模块都是彻底同步、真实的双端存储器。用户可独登时从每个端口读出或向每个端口写入(但同一地址不能一同进行读和写)。别的,每个端口都有一个独立的时钟,而且对每个端口的数据宽度都能够独立进行装备。如图11.6所示为双端RAM模块的框图。

由FPGA逻辑和一批BlockRAM组成的FIFO取决于所构建的FIFO要求的宽度和深度。FIFO可运用XilinxCOREGenerator™东西构建,或许能够用HDL手动组合。

运用COREGenerator东西构建FIFO具有必定优势,即规划能够到达并完结很高的性能指标。依照规划规范用HDL构建的规划则可赋予规划人员彻底的规划自在。

3.FPGA与DSP的EMIF衔接

FPGA的灵活性使咱们能够将其用做具有可挑选总线宽度(8位~64位)的各类存储器而创立不同的规划。经过接口规划,可将FPGA用做同步或异步规范存储器,或同步或异步FIFO。经过接口规划,可将FPGA以同步或异步的方法衔接到EMIF。

在同步形式中,ECLKOUTx时钟用于驱动FPGA接口逻辑。此刻钟乃至能够驱动整个FPGA。FPGA的逻辑功用、专用乘法器、PPC405或MicroBlaze™处理器等使其具有了强壮的处理功用。这样,FPGA就能够用做协处理器或高速数据处理和传输器材。

FPGA的存储器容量小于TMSC64x类型DSP的寻址空间。FPGA存储器有必要运用FPGABlockRAM来完结。上述TMSC64x到FPGA的接口为FIFO结构,能够运用BlackRAM资源来完结。

FIFO接口可运用规范的TMSC64xEMIFFIFO接口机制。如表11.3所示为EMIF信号的总结。

表11.3 EMIF与FPGA的接口信号

|

信号称号 |

方向 |

|

CE |

DSP输出 |

|

AOE |

DSP输出 |

|

AWE |

DSP输出 |

|

ARE |

DSP输出 |

|

INTx |

DSP输入 |

|

INTy |

DSP输入 |

|

INTz |

DSP输入 |

|

ED[63:0] |

DSP双向 |

FIFO要求接连地读时钟和接连地写时钟。这些时钟由ARE和AWE信号生成,运用FPGA的本地时钟操控功用进行布线。

DSP具有3.3V的接口逻辑,所以用于衔接到EMIF的I/O组(bank)有必要指定为3.3VVCCIO。假如无法指定,就有必要运用电平移位器材。这一器材可为两个器材间的信号通路引进额定的时刻。

4.FIFO接口的规划实例

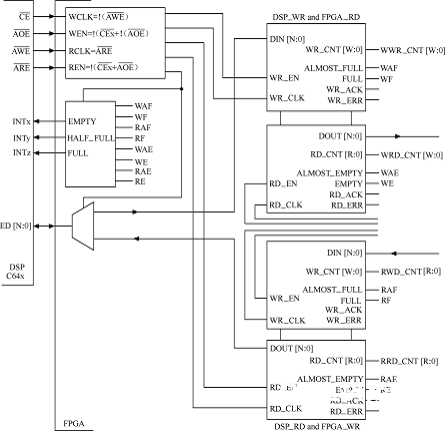

本规划运用了规范的EMIFFIFO设置。如图11.7所示为用于Xilinx公司的Virtex-IIPro和Spartan-3器材的规划示例。

图11.7根据FIFO的EMIF接口实例

数据组芯片使能信号(Cex)与异步输出使能(AOE)一同,用于为规划的写或读FIFO部分生成使能信号。此信号还用于为数据多路复用器和标志挑选逻辑生成使能信号。

FIFO的读写时钟经过本地时钟布线直接布线到FIFO时钟输入。

FIFO中运用的RAMB16组件因为沿着与EMIF相衔接的I/O块进行摆放,明显改进了时序。当BlockRAM组件的列的巨细与运用的I/O的数量相一同,即可构建快速的矩形接口。

本规划运用惯例的FIFO标志输出。要对标志逻辑施加额定操控,无论是针对DSP端仍是FPGA端,可运用写计数器和读计数器输出。

信号AINIT(图11.7中未显现)强制一切标志为高有用状况。AINIT宣布后,在第一个WR_CLK上,FULL和ALMOST_FULL标志变为无效,呈低状况。关于在首个RD_CLK边沿上的EMPTY和ALMOST_EMPTY符号,也会发生相同状况。

ALMOST_EMPTY和ALMOST_FULL标志标明只剩下了一个FIFO方位。运用WR_COUNT和RD_COUNT输出,能够构建用户界说的FIFO标志。这两个计数器的值都不反映FIFO内容(地址)的精确方位。FIFO的两个端口(时钟域)都存在时钟推迟,长度为一个时钟周期。

输出WR_COUNT和RD_COUNT为被推迟的内部FIFO高位地址计数器。为输出挑选两个比特,即可将FIFO的方位承认到总尺度的四分之一(如下面计数器解码示例中所示)。

计数器越宽,方位就能越精密。下面是计数器解码示例。

·COUNT[1:0]=0b00标明FIFO小于1/4满或1/4空。

·COUNT[1:0]=0b01标明FIFO在1/4和1/2满之间或1/4和1/2空之间。

·COUNT[1:0]=0b10标明FIFO在1/2和3/4满之间或1/2和3/4空之间。

·COUNT[1:0]=0b11标明FIFO大于3/4满或3/4空。

DSP对不同标志的反响取决于FPGA中读写FIFO的状况。

11.3.2根据TMS320系列DSP的主机接口(HPI)规划

1.HPI接口简介

HPI接口是一种数据宽度为16位的并行端口(C64xx系列DSP中,HPI口的数据宽度到达32位)。经过HPI口,主机能够直接对CPU的存储器空间进行操作。

在C621x、C671x系列DSP中,没有留出专门的EDMA通道来履行HPI口的拜访操作,而是直接将HPI口衔接到内部的地址发生硬件上,因此进步了对内部存储空间的拜访速度。

HPI口内部加入了两个8级深度的读写缓冲,能够履行地址自增的读写操作,进步读写操作的吞吐量。HPI口为内部CPU供给了规范32位的数据接口,一同为外部主机也供给了一个经济的16位接口,所以对外部主机而言,每次读写有必要履行成对的16位操作。

关于C64xx系列DSP,HPI能够挑选16位(HPI16)和32位(HPI32)两种形式。

关于C621x、C671x系列DSP,HPI口内部有3个寄存器,别离是操控寄存器(HP%&&&&&%)、地址寄存器(HPIA)和数据寄存器(HPID)。这3个寄存器能够直接被主机拜访,主机每履行一次对CPU内部存储空间的拜访都有必要先对操控寄存器和地址寄存器写入相应的值,然后才干对数据寄存器进行读写操作。

HPI口的外部接口是由数据总线HD[15:0]以及一部分用于描绘和操控HPI接口的操控信号组成,这些操控信号的详细类型如表11.4所示。

表11.4 HPI信号描绘

|

引脚 |

描绘 |

|

HCNTL[1:0] |

操控HPI的操作类型 |

|

HHCNTL |

半字承认输入,“0”、“1”别离标明一次字传输的第一个半字和第二个半字 |

|

HR/W |

读/写挑选 |

续表

|

引脚 |

描绘 |

|

HRDY |

安排妥当状况标志 |

|

HINT |

中止标志,DSP向主机提出中止 |

|

HAS |

差异地址/数据复用总线的数据与地址 |

|

HDS1、HDS2、HCS |

数据选通输入,三者合作可用于发生一个HPI内部选通讯号HSTROBE,这个信号能够用以下公式来描绘: HSTROBE=[NOT(HDS1XORHDS2)]ORHCS |

关于一个写HPI口的操作,应首要使能HCS,改变HDS1或HDS2,可使HSTROBE信号发生一个下降沿。HPI口在这个下降沿采样操控信号HCNTL[1:0]、HHWIL和HR/W,一同在使能HCS的一同驱动HRDY,以使主机进入等候状况。直到HRDY发生下降沿,标明HPID已清空,能够接纳新的数据。此刻HSTROBE也将发生一个上升沿,并采样HD[15:0]上的数据并将其送入HPID,以完结第一个半字的写入。

关于第二个半字的写入,因为32位的HPID现已清空,能够直接写入数据。不会呈现未准备好的状况,所以HRDY一向坚持为低,与第一个字节的写入相同。该操作也在HSTROBE的下降沿采样操控信号,并在HSTROBE的上升沿采样数据总线HD[15:0]的数据并送HPID,以完结一个32位的写入操作。

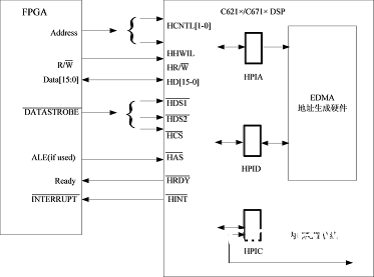

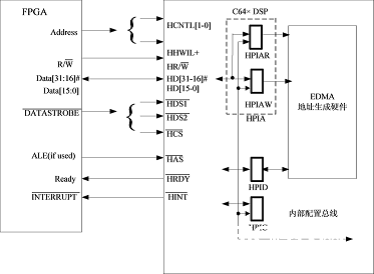

2.FPGA与DSP的HPI衔接实例

FPGA与HPI的接口衔接比较简略,便是将HPI接口相关的信号悉数衔接到FPGA的管脚。如图11.8和图11.9所示别离是FPGA和TI不同系列的DSP的衔接框图。

图11.8FPGA与C621x、C671x系列DSP的HPI接口互联框图

图11.9FPGA与C64x系列DSP的HPI接口互联框图