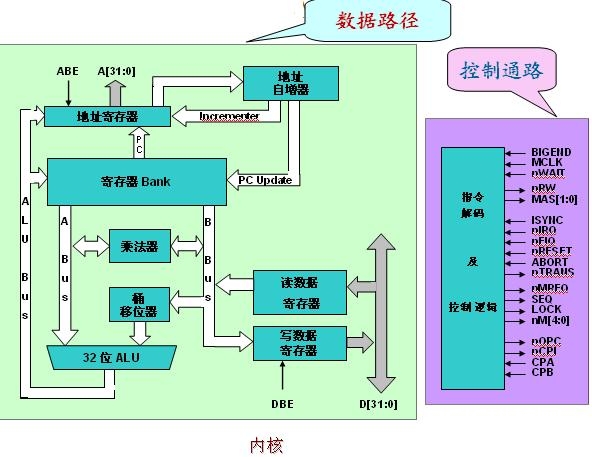

ARM处理器结构

ARM和Thumb状况

RISC技能

流水线技能

超标量技能

ARM和Thumb状况

V4版今后有:

(1)32位ARM指令集

(2)16位Thumb指令集,功用是ARM指令集的功用子集。

ARM7TDMI核今后,T变种的ARM微处理器有两种作业状况:

(1)ARM状况

(2)Thumb状况。

当ARM微处理器履行32位的ARM指令集时,作业在ARM状况;

当ARM微处理器履行16位的Thumb指令集时,作业在Thumb状况

Thumb技能介绍

ARM7体系结构被广泛运用的时分,嵌入式操控器的商场依然由8位、16位处理器占据。这些产品不能满意高端运用。这些运用需求32位RISC处理器的功用和更优于16位CISC处理器的代码密度。

为了处理代码密度的问题,ARM添加了T变种。

Thumb从32位ARM指令会集抽出来的36条指令格局,可从头编成16位的操作码。

在运转时,16位的Thumb指令又由处理器解压成32位指令。

Thumb核有2套独立的指令集,它使规划者得到ARM32位指令功用的一起,又能享有Thumb指令集发生的代码方面的优势,在功用和代码巨细之间获得平衡。

和ARM指令集比较,Thumb指令集具有以下的约束:

完结相同的操作,Thumb指令一般需求更多的指令,因而在对体系运转时刻要求严苛的场合,ARM指令集更为适宜。

Thumb指令集没有包含进行反常处理时需求的一些指令,因而在反常中断时,仍是需求运用ARM指令,这种约束决议了Thumb指令需求与ARM指令合作运用。

ARM与Thumb状况转化

在程序的履行进程中,微处理器可以随时在两种作业状况之间切换,而且该改动不影响处理器的作业形式和相应寄存器中的内容。

进入Thumb状况:当操作数寄存器的状况位(位[0])为1时,履行BX指令。

进入ARM状况:当操作数寄存器的状况位(位[0])为0时,履行BX指令。

RISC技能

嵌入式微处理器可以分为两类:CISC和RISC;

CISC(Complex Instruction Set Computer):杂乱指令体系核算机;跟着核算机技能的开展而不断引进新的杂乱的指令集,核算机的体系结构会越来越杂乱。

大约有20%的指令会被重复运用,占整个程序代码的80%,而余下的80%的指令却不常常运用,在程序规划中只占20% 。

RISC(Reduced Instruction Set Computer):精简指令体系核算机;- 选用固定长度的指令格局

- 运用单周期指令

- 很多运用寄存器

- 可用加载/存储指令批量传输数据

- 在循环处理中运用地址的主动增减

RISC技能与CISC技能比较

RISC技能

ARM处理器选用加载/存储(Load/Store)体系结构是典型的RISC处理器,即只要Load/Store的存/取指令可以拜访存储器,其他指令都不答应进行存储器操作。

RISC体系结构根本特色:

(1)大多数指令只需求履行简略和根本的功用,其履行进程在一个机器周期内完结。

(2)只保存加载/存储指令。操作数由加载/存储指令从存储器取出放寄存器内操作。

(3)芯片逻辑不选用或少选用微码技能,而选用硬布线逻辑。

(4)削减指令数和寻址方法。

(5)指令格局固定,指令译码简化。

(6)优化编译。

RISC技能

ARM体系结构还选用了一些特别的技能:

一切的指令都可依据前面的履行成果决议是否被履行,进步了指令的履行功率。

可用Load/Store指令批量传输数据,以进步数据的传输功率。

可在一条数据处理指令中一起完结逻辑处理和移位处理。

RISC和CISC各有优势,边界并不那么显着。

现代的CPU往往选用CISC的外围,内部加入了RISC的特性,如超凡指令集CPU便是交融了RISC和CISC的优势,成为未来的CPU开展方向之一。

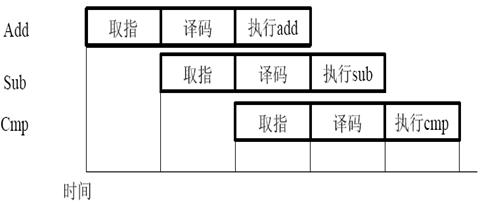

流水线技能

是一种将每条指令分解为多步,并让各步操作堆叠,然后完结几条指令并行处理的技能;

程序中的指令仍是一条条次序履行,但可以预先取若干条指令,并在当时指令没有履行完时,提早发动后续指令的另一些操作进程,然后可加速程序的运转速度;

开发和规划嵌入式体系的进程中,CPU的功用是一个非常重要的考虑要素。

流水线技能是在本质上影响程序履行速度的要素。

因为核算机中一条指令的各个履行阶段相对独立,因而,现代CPU大多规划成流水线型的机器,在这种类型机器中几个指令可以并行履行。选用流水线的堆叠技能大大进步了CPU的运转功率。

当流水线内部的信息晓畅活动时,CPU流水线可以作业得最好。

但实践运用中,指令各履行阶段的操作时刻长短不同,有一些指令序列可能会打断流水线内的信息流,所以有时流水线操作不非常晓畅,会暂时下降CPU的履行速度。

单周期指令的履行进程

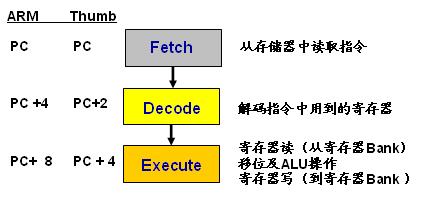

ARM的3级流水线

ARM7架构选用了一个3段的流水线:

(1)取指:将指令从内存中取出来。

(2)译码:操作码和操作数被译码以决议履行什么功用。为下一周期预备数据途径需求的操控信号。这一级指令”占有“译码逻辑,而不是”占有”数据途径

(3)履行:履行已译码的指令。指令占有数据途径,寄存器仓库被读取,操作数在桶行移位器中被移位。ALU发生运算成果并回写到意图寄存器中,ALU成果依据指令需求更改状况寄存器的条件位。

流水线形式下PC的更改进程

多周期ARM指令的3级流水线操作

数据途径涉及到一切履行周期、地址核算和数据传送。译码逻辑总是发生数据途径鄙人一个周期运用的操控信号,因而除译码周期以外,在STR地址核算周期也发生数据传送所需的操控信号。

取指的存储器拜访和履行的数据途径占用都是不行一起同享的资源,关于多周期指令来说,假如指令杂乱以至于不能在单个时钟周期内完结履行阶段,就会发生流水线堵塞。

ARM的流水线规划问题

1)缩短程序履行时刻:

Tprog:履行一个程序所需时刻;

Ninst:履行该程序的指令条数;

CPI:履行每条指令的均匀时钟周期数;

Fclk:处理器的时钟频率。

办法:

进步时钟频率fclk(导致流水线的级数添加 )。

削减每条指令的均匀时钟周期数CPI(需求处理流水线的相关问题 )

2)处理流水线相关:

结构相关:某些指令在流水线中堆叠履行时,发生资源抵触 。

办法:1)选用分离式指令Cache和数据Cache。2)ALU中选用独自加法器来完结地址核算。

数据相关:当一条指令需求前面指令的履行成果,而这些指令均在流水线中堆叠履行时,就可能引起流水线的数据相关。

数据相关有“写后读”、“写后写”和“读后写”等。

办法:1)旁路技能。2)流水线互锁技能。

操控相关:当流水线遇到分支指令和其他会改动PC值的指令时,就会发生操控相关。

办法:1)引进延时分支。2)尽早核算出分支搬运成功时的PC值(即分支的方针地址)。

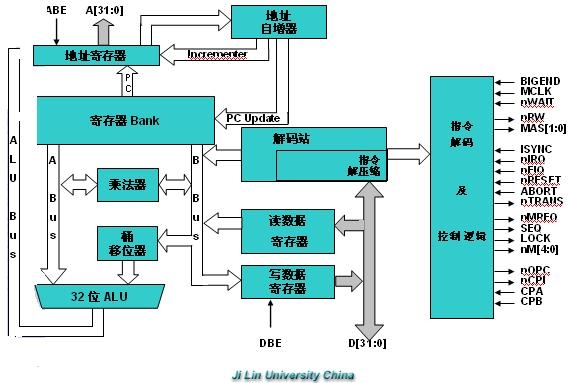

ARM的5级流水线

ARM9和StrongARM架构都选用了5级流水线.

添加了I-Cache和D-Cache,把存储器的取指与数据存取分隔;

添加了数据写回的专门通路和寄存器;

把指令的履行进程分割为5部分:

取指:将指令从指令存储器中取出,放入指令流水线中。

指令译码:对指令进行译码,从寄存器堆中读取寄存器操作数。

履行:把一个操作数移位,发生ALU成果。假如指令是Load或Store,在ALU中核算存储器的地址。

数据缓存:假如需求,拜访数据存储器;不然,ALU的成果仅仅简略地缓冲一个时钟周期,以便使一切指令具有同样地流水线流程。

写回 :将指令发生地成果写回到寄存器堆。

流水线比照

超标量履行

经过重复设置多套指令履行部件,一起处理并完结多条指令,完结并行操作,来到达进步处理速度的意图。

一切ARM内核,包含盛行的ARM7、ARM9和ARM11等,都是单周期指令机。

ARM公司下一代处理器将是每周期能处理多重指令的超标量机。

超标量处理机:一个时钟周期内一起履行多条指令的处理机。

超标量处理器中的多指令单元

超标量与流水线技能是兼容的,为了可以在一个时钟周期内一起发射多条指令,超标量处理机有必要有两条或两条以上可以一起作业的指令流水线。但与此一起,也带来了多流水线的调度问题和操作部件的资源抵触问题。

超标量处理器在履行的进程中有必要动态地查看指令相关性。

假如代码中有分支指令,有必要将分支被履行和分支不被履行这两种状况分隔考虑。

核算履行时刻几乎是不行能的。