现在国际上有两种文明,一种是人类社会组成的的碳基文明,一种是各种芯片组成的硅基文明——因为简直一切的芯片都是以单晶硅为质料制作的,芯片体系的总数比人类的数量还多出数十上百倍。芯片咱们族里边也分各种不同类型的芯片,从陈旧的用电子管堆出来的成吨的逻辑门到现在的超级数据中心,电子技能的开展走过了一代又一代,到了今日,各种芯片更是百家争鸣,芯片厂商百家争鸣。

可是,这么多芯片,依照功用分类,有专门用于核算的、有专门用于操控的、有专门用于存储的……依照集成电路规区分,有超大规划,大规划,和陈旧的中规划、小规划。而详细到了类型,又有CPU,SoC,DSP……有这么多的芯片,真的差异铲除也是要花上一番功夫的,这篇文章就能够带领咱们了解一些根底的、用来处理数据的集成电路芯片。

在这些专门用于处理数据的芯片中,最常用的便是由微处理器构成的微处理器体系,小到一块单片机,大到数据中心的几十路几十核地表最强处理器,都是由简略的微处理器体系开展而来,微处理器是运用最广泛的芯片。首要了解微处理器及微处理器体系,对接下来了解各种芯片及操控体系的很有协助。

微处理器体系

微处理器体系,包括了各品种型的核算机,微操控器/单片机。国际上的微处理器体系的总数比人类总数还多得多。它的根本作业原理是用程序操控体系的行为。

微处理器体系的根本操作进程是中央处理器(Central Processing Unit, CPU)不断地从存储器取指并履行,完结对体系的全面办理。

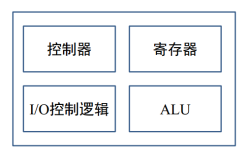

一、CPU结构和功用CPU的结构:

▲图:CPU的结构

1) 操控器:完结指令的读入、寄存、译码和履行。

2) 寄存器:暂存用于寻址和核算进程的发生的地址和数据。

3) I/O操控逻辑:担任CPU中与输入/输出操作有关的逻辑。

4) 管用逻辑运算单元(Arithmetic & Logic Unit, ALU):运算器中心,担任进行算术运算、逻辑运算和移位操作,用来进行数值核算和发生存储器拜访地址。

CPU的功用:

1) 与存储器之间交流信息。

2) 和I/O设备之间交流信息。

3) 为了使体系正常作业而接纳和输出必要的信号,如复位信号、电源、输入时钟脉冲等。

二、微处理器体系的结构

▲图:微处理器体系的结构

1) CPU的外部特征便是数量有限的输入输出引脚。

2) 数据总线:用于CPU和存储器或I/O接口之间传送数据,双向通讯;数据总线的条数决议了CPU和存储器或I/O设备一次最多能交流数据的位数,是微处理器的位数的判据,例如:Intel 386DX、ARM Cortex-M3是32位微处理器;Intel选用了IA-64架构的处理器、PowerPC 970是64位处理器;相似地,还有愈加陈旧的8位、16位处理器等。

3) 地址总线:CPU通过地址总线输出地址码用以挑选某一存储单元或某一成为I/O端口的寄存器,单向通讯;地址总线的条数决议了地址码的位数,从而决议了存储空间的巨细,例如:地址总线宽度(条数)为8,则能够符号2^8 = 256个存储单元,若每个存储单元的字长为8 bit,则最大能够接入体系的存储空间为256kB。

4) 操控总线:用来传送自CPU宣告的操控信息或外设送到CPU的状况信息,双向通讯;

微处理器体系的程序规划言语:程序规划言语(Programming Language),又称为编程言语,是用来界说核算机程序的,通过代码向处理机宣告指令。编程言语让开发者能够准确地供给核算机所运用的数据,并准确地操控在不同状况下所应当采纳的举动。最早的编程言语是在核算机创造之后发生的,其时是用来操控提花织布机及主动演奏钢琴的动作。在电脑范畴已创造了上千不同的编程言语,并且每年仍有新的编程言语诞生。许多编程言语需求用指令办法阐明核算的程序,而有些编程言语则归于声明式编程,阐明需求的效果,而不阐明怎么核算。

机器言语:机器言语的每条句子便是处理器能够直接履行的一条指令,这些指令是以二进制0、1序列的办法表明,对应数字集成电路的凹凸电平。不同的处理器指令的机器代码各不相同,完结的详细功用也将不相同,按着一种核算机的机器指令编写的程序,不能在另一种核算机上履行。

示例:(仅作为示例,不代表实在硬件的机器代码)

指令的机器代码:

0000’0000 STORE

0000’0001 LOAD

地址的机器代码:

0000’0000 寄存器R0

0000’0001 寄存器R1

长处:功用和代码一一对应,CPU能够直接履行,功率最高。

缺陷:只要二进制0、1序列,单调,难以辨识。

汇编言语:用简练的英文字母、符号串来替代一个特定的机器言语指令——二进制0、1序列:用助记符(Memoni)替代操作码,用地址符号(Symbol)或标号(Label)替代地址码。汇编言语与机器言语一一对应,所以和机器言语相同对核算机硬件的依赖性很大。

示例:加法运算(分号表明接注释)

MOV R1,? R3;

将寄存器R3的值赋予R1

LDR R2, [R4]

;将寄存器R4的值代表的地址对应的存储空间的值赋予R2

ADCS R0, R1, R2

;将寄存器R1、R2与之前的进位值相加且进位,存储到寄存器R0

长处:汇编句子和机器言语一一对应,助记符与标号往往与实践意义相关,比较于机器言语,愈加直观,简略了解,履行功率上相似。

缺陷:不同的处理器指令集不同,移植性欠好;即便完结简略的数据处理(如累加,简略排序等)所需的代码体积很大,处理实践问题所需的作业量夸大,本钱高。

高档言语:运用接近于数学言语或人类言语的表达描绘程序。

特征:比较于面向机器开发的机器言语和汇编言语,高档言语具有较高的可读性,并且代码量大大削减;高档言语一般远离对硬件的直接操作,安全性较高,也有部分高档言语能够运用调用汇编言语的接口操控硬件;高档言语有许多老练、易于运用、可移植的数据结构与算法,使开发流程大大简化,节约开发本钱,易于保护;开展迅速,社区齐备,能够很方便地求助,处理遇到的各种问题;现已有许多各具特征、用以处理不同范畴问题且开展适当齐备的高档言语供开发者选用,如:适宜初学者了解编程思维的Basic;功率颇高,接近于硬件操控,适宜体系、硬件驱动编程与嵌入式开发的C/C++;跨渠道、可移植特性优秀的Java;调配Visual Studio能够快速开发项意图C#。NET;适宜于数据剖析、人工智能,越来越被喜爱的Python;Microsoft公司为未来的量子核算而开发的Q#,等等。比方MATLAB、HTML、JavaScript这样的用以在不同范畴大显神通的言语亦能够称之为高档言语。

示例:加法运算

int a = 1, b = 2, c;

c = a + b;

长处:不依赖于硬件,移植性好;不必场合选用适宜的言语,开发功率高。

缺陷:不直接运用硬件,需求编译-链接履行或解说履行,没有运用到详细硬件的特征,功率比较于机器言语和汇编言语不高;先天的特征决议了高档言语在底层的规划中无法彻底替代机器言语和汇编言语。

能够看出,微处理器体系的中心部件是CPU,运用微处理器体系操控外部的设备作业的本质便是运用编写软件程序的手法来操控外部设备。因为CPU现已是一个完好的、封装好的部件,体系的规划人员只能通过编写软件,再经由编译器或解说器翻译为机器能够了解的代码来履行,CPU并没有专门的硬件电路来完结彻底地操控外部设备的作业,这种完结办法是软件完结,是一种通用的完结,操控信号从软件到硬件要通过若干次转化,但有的时分,工程和规划范畴往往需求高速高功用的芯片来完结操控与核算,这时分就需求愈加强壮的CPU或将几个CPU用一些技能并行起来协同作业,本钱就会添加。这时分,能够无妨试试规划专门的硬件来满意作业的需求。

三、专用集成电路

专用的集成电路(Application Specific Integrated Circuit, ASIC)是一种为专门意图而规划的集成电路。是指应特定用户要求和特定电子体系的需求而规划、制作的集成电路。ASIC的特征是面向特定用户的需求,ASIC在批量生产时与通用集成电路比较具有体积更小、功耗更低、牢靠性前进、功用前进、保密性增强、本钱下降一级长处。

ASIC分为全定制和半定制。全定制规划需求规划者完结一切电路的规划,包括芯片规划的一切流程,因而需求许多人力物力,灵敏性好但开发功率低下。假如规划较为抱负,全定制能够比半定制的ASIC芯片作业速度更快。半定制ASIC运用准逻辑单元(Standard Cell),规划时能够从规范逻辑单元库中挑选SSI(小规划集成电路,如门电路)、MSI(中规划集成电路,如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器乃至体系级模块(如乘法器、微操控器等)和IP核,这些逻辑单元现已布局完毕,并且规划得较为牢靠,规划者能够较方便地完结体系规划。

当今ASIC的规划方向现已越来越多地运用可编程逻辑器材来结构,开发门槛和难度不断下降,流程不断简化,本钱不断下降,事务也开端变得丰厚且多元化。现在ASIC现已走向了深度学习、人工智能、第五代移动通讯技能(5G)等高新技能范畴,在可编程逻辑器材两大巨子Xilinx和Altera的推进下,能够预见未来的ASIC规划将是可编程逻辑器材(尤其是现场可编程门阵列,FPGA)的全国。

四、可编程逻辑器材

可编程逻辑器材(Programmable Logic Device, PLD)是一种通用集成电路,它是ASIC的一个子集,逻辑功用能够依照用户对器材编程来确认。一般的PLD的集成度很高,足以满意规划一般的数字体系的需求。这样就能够由规划人员自行编程而把一个数字体系“集成”在一片PLD上,而不必去请芯片制作厂商规划和制作ASIC芯片了,因为假如芯片需求量不大,规划制作ASIC的单片本钱是很高的。

PLD与一般数字芯片不同的是:PLD内部的数字电路能够在出厂后才规划决议,乃至能够无限制改动,而一般数字芯片在出厂前就现已决议其内部电路,无法在出厂后再次改动,现实上一般的模仿芯片、通讯芯片、微操控器也都相同,出厂后就无法再对其内部电路进行更改。最近闹得沸反盈天的Intel公司的芯片缝隙事情,便是因为CPU的内部电路现已无法更改,所以只能规划新的CPU芯片来处理,或是丢失一些功用用软件修补的办法来补偿。

五、可编程逻辑器材的开展进程

最早的可编程逻辑器材(PLD)是1970年制成的可编程只读存储器(PROM),它由固定的与阵列和可编程的或阵列组成。PROM选用熔丝技能,只能写一次,不能擦除和重写。跟着技能的开展,尔后又呈现了紫外线可擦除只读存储器(UVEPROM)和电可擦除只读存储器(EEPROM)。因为其价格便宜、速度低、易于编程,适宜于存储函数和数据表格。

可编程逻辑阵列(PLA)于20世纪70年代中期呈现,它是由可编程的与阵列和可编程的或阵列组成,但因为器材的价格比较贵、编程杂乱、资源运用率低,因而没有得到广泛运用。

可编程阵列逻辑(PAL)是1977年美国MMI公司首先推出的,它选用熔丝编程办法,由可编程的与阵列和固定的或阵列组成,选用双极性工艺制作,器材的作业速度很高。因为它的规划很灵敏,输出结构品种许多,因而成为榜首个得到遍及运用的可编程逻辑器材

通用阵列逻辑(GAL)是1985年Lattice公司最早创造的可电擦写、可重复编程、可设置加密位的PLD。GAL在PAL的根底上,选用了输出逻辑宏单元办法(EECMOS)工艺结构。在实践运用中,GAL对PAL仿真具有百分之百的兼容性,所以GAL简直彻底替代了PAL,并能够替代大部分规范SSI、MSI集成芯片,因而取得广泛运用。

可擦除可编程逻辑器材(EPLD)是20世纪80年代中期Altera公司推出的根据UVEPROM和CMOS技能的PLD,后来开展到选用EECMOS工艺制作的PLD,EPLD的根本逻辑单元是宏单元,宏单元是由可编程的与阵列、可编程寄存器和可编程I/O三部分组成的。从某种意义上讲,EPLD是改善的GAL,它在GAL根底上许多添加输出宏单元的数目,供给更大的与阵列,集成密度大幅前进,内部连线相对固定,延时小,有利于器材在高频下作业,但内部互连才干较弱。

杂乱可编程逻辑器材(CPLD)是20世纪80年代末Lattice公司提出了在线可编程技能(SP)今后于20世纪90年代初推出的。CPLD至少包括三种结构:可编程逻辑宏单元可编程I/O单元和可编程内部连线,它是在EPLD的根底上开展起来的,选用EECMOS工艺制作,与EPLD比较,添加了内部连线,对逻辑宏单元和I/O单元也有很大改善。

现场可编程门阵列(FPGA)器材是Xilinx公司1985年首家推出的,它是一种新式的高密度PLD,选用CMOS-SRAM工艺制作。FPGA的结构与门阵列PLD不同,其内部由许多独立的可编程逻辑模块(CLB)组成,逻辑块之间能够灵敏地相互连接,CLB的功用很强,不只能够完结逻辑函数,还能够装备成RAM等杂乱的办法。装备数据寄存在芯片内的SRAM中,规划人员可现场修正器材的逻辑功用,即所谓的现场可编程。FPGA呈现后遭到电子规划工程师的遍及欢迎,开展十分迅速。

FPGA和CPLD都具有体系结构和逻辑单元灵敏、集成度高以及适用范围宽的特征。这两种器材兼容了简略PLD和通用门阵列的长处,可完结较大规划的电路,编程也很灵敏,与ASIC比较,具有规划开发周期短、规划制作本钱低,开发东西先进、规范产品无须测验、质量安稳等长处,用户能够重复地编程、擦除、运用,或许在外围电路不动的状况下用不同软件就可完结不同的功用以及可实时在线查验。

CPLD是一种比PLD杂乱的逻辑元件。CPLD是一种用户可根据各自需求而自行结构逻辑功用的数字集成电路。与FPGA比较,CPLD供给的逻辑资源相对较少,可是经典CPLD构架供给了非常好的组合逻辑完结才干和片内信号延时可猜测性,因而关于要害的操控运用比较抱负。

FPGA是在PAL、GAL、EPLD等可编程器材的根底上进一步开展的产品。它是作为ASIC范畴中的一种半定制电路而呈现的,供给了丰厚的可编程逻辑资源、易用的存储、运算功用模块和杰出的功用,既处理了定制电路的缺乏,又克服了原有可编程器材门电路数有限的缺陷。

FPGA和CPLD因为结构上的差异,各具本身特征。因为FPGA的内部结构触发器份额和数量多,所以它在时序逻辑规划方面更有优势:而CPLD因具有与或门阵列资源丰厚、程序掉电不易失等特征,适用于组合逻辑为主的简略电路。全体来说,因为FPGA资源丰厚功用强壮,在产品研制方面的运用杰出,当时新推出的可编程逻辑器材芯片首要以FPGA类为主,跟着半导体工艺的前进,其功率损耗越来越小,集成度越来越高。

在微处理器体系上,软件规划师用程序规划言语操控整个体系的正常作业,而在可编程器材范畴,操作的方针不再是一组组数据类型,而是一些硬件器材,如存储器,计数器等,乃至是一些愈加底层的触发器、逻辑门,有的乃至要准确到集成晶体管开关级的操控。并且许多器材不再是次序的堵塞式作业,而是并行的触发作业,经典的程序流程操控思维在可编程器材范畴不适用。规划人员需求运用一种能够结构硬件电路的言语,即硬件描绘言语。

六、硬件描绘言语

硬件描绘言语(Hardware Description Language, HDL)是一种用办法化办法描绘逻辑电路和体系的言语。运用这种言语,逻辑电路体系的规划能够从上层到基层(从笼统到详细)逐层描绘自己的规划思维,用一系列分层次的模块来表明极端杂乱的逻辑体系。然后,运用电子规划主动化(EDA)东西,逐层进行仿真验证,再把其间需求变为实践电路的模块组合,通过主动归纳东西转化到门级电路网表。接下来,再用专用集成电路(ASIC)或现场可编程门阵列(FPGA)主动布局布线东西,把网表转化为要完结的详细电路布线结构。据统计,现在在美国的硅谷约有90%以上的ASIC和PLD选用硬件描绘言语进行规划。

硬件描绘言语HDL的开展至今已有30多年的前史,其成功地运用于规划的各个阶段:建模、仿真、验证和归纳等。到20世纪80年代,已呈现了上百种硬件描绘言语,对规划主动化曾起到了极大的促进和推进效果。可是,这些言语一般各自面向特定的规划范畴和层次,并且许多的言语运用户莫衷一是。因而,需求一种面向规划的多范畴、多层次并得到遍及认同的规范硬件描绘言语。20世纪80年代后期至90年代,VHDL和Verilog HDL言语习惯了这种趋势的要求,先后成为电气和电子工程师协会(Institute of Electrical & Electronics Engineers, IEEE)规范。

现在,跟着超大规划FPGA以及包括SoC内核FPGA芯片的呈现,软硬件和谐规划和体系规划变得越来越重要。传统意义上的硬件规划越来越倾向于与体系规划和软件规划结合。硬件描绘言语为习惯新的状况,迅速开展,呈现了许多新的硬件描绘言语,像System Verilog,SystemC、Cynlib C++等;另一方面,PLD规划东西在原先仅支撑硬件描绘言语规划输入的根底上,日益添加对传统高档规划言语(如C/C++)的规划支撑。

现在,硬件描绘言语可谓是百家争鸣,有VHDL、Verilog HDL、Superlog、SystemC、System Verilog、Cynlib C++、C Level等。全体而言,在PLD开发范畴运用最广的仍是VHDL和Verilog HDL。跟着逻辑体系开发规划的不断增大,SystemC和System Verilog等体系级硬件描绘言语也得到越来越多的运用。

VHDL

早在1980年,因为美国军事工业需求描绘电子体系的办法,美国国防部开端进行VHDL的开发。1987年,IEEE将VHDL拟定为规范。参考手册为IEEE VHDL言语参考手册规范草案1076/B版,于1987年同意,称为IEEE 1076-1987。可是,起先VHDL仅仅作为体系规范的一个规范,而不是为规划而拟定的。第二个版别是在1993年拟定的,称为VHDL-93,添加了一些新的指令和特点。

虽然有“VHDL是一个4亿美元的过错”这样的说法,但VHDL毕竟是1995年曾经仅有拟定为规范的硬件描绘言语,这是它不争的现实和优势;但一同它的运用的确比较费事,并且其归纳库至今也没有规范化,不具有晶体管开关级模仿规划的描绘才干。现在来说,关于特大型的体系级逻辑电路规划,VHDL是较为适宜的。

本质上,在底层的VHDL规划环境是由Verilog HDL描绘的器材库支撑的,因而,它们之间的互操作性十分重要。现在,Verilog和VHDL的两个国际安排OVI(Open Verilog International)、VI正在谋划这一作业,预备树立专门的作业组来和谐VHDL和Verilog HDL言语的互操作性。OVI也支撑不需求翻译,由VHDL到Verilog的自在表达。

Verilog HDL

Verilog HDL是在1983年,由GDA(Gateway Design AUTOMATION)公司的Phil Moorby创始的。Phil Moorby后来成为Verilog-XL的首要规划者和Cadence公司的榜首合伙人。在1984-1985年,Phil Moorby规划出了榜首个名为Verilog-XL的仿真器;1986年,他对Verilog HDL的开展又作出了另一个巨大的奉献:提出了用于快速门级仿真的XL算法。

跟着Verilog-XL算法的成功,Verilog HDL言语得到迅速开展。1989年,Cadence公司收买了GDA公司,Verilog HDL言语成为Cadence公司的私有财产。1990年,Cadence公司决议揭露Verilog HDL言语,所以树立了OVI安排,担任促进Verilog HDL言语的开展。根据Verilog HDL的优越性,IEEE于1995年拟定了Verilog HDL的IEEE规范,即Verilog HDL 1364-1995;2001年发布了Verilog HDL 1364—2001规范,在这个规范中,加入了Verilog HDL – A规范,使Verilog HDL有了模仿规划描绘的才干

SystemC

跟着半导体技能的迅猛开展,SoC现已成为当今集成电路规划的开展方向,智能手机,平板电脑里的处理器,严格地来说实践上是SoC,因为其上集成了CPU、图形处理单元(Graphic Processing Unit, GPU)、数字信号处理器(Digital Signal Processor)、基带(Baseband)信号处理器等。在体系芯片的各个规划(像体系界说、软硬件区分、规划完结等)中,集成电路规划界一直在考虑怎么满意SoC的规划要求,一直在寻觅一种能一同完结较高层次的软件和硬件描绘的体系级规划言语

SystemC正是在这种状况下,由Synopsys公司和Coware公司积极响应现在各方对体系级规划言语的需求而合作开发的。1999年9月27日,40多家国际闻名的EDA公司、IP公司、半导体公司和嵌入式软件公司宣告树立“开放式SystemC联盟”。闻名公司Cadence也于2001年加入了SystemC联盟。SystemC从1999年9月联盟树立初期的0.9版别开端更新,从1.0版到1.1版,一直到2001年10月推出了最新的2.0版。

七、常见的数据处理芯片

已然现已梳理了两大类(微处理器,专用集成电路)芯片的概念和原理,接下来就了解一下常见的芯片

MCU

日常日子中最常见得到的微处理器体系便是咱们身边的微型核算机,也便是个人电脑(Personal Computer, PC),能够使台式机、笔记本,或是PC界的新秀——各种炫酷的二合一设备。这些看起来杂乱无比的电子体系都是由最简略的微处理器体系开展起来的。可是日子中并不需求那么多的电脑,比方想要做一台能够主动操控加热保温的电饭煲,其CPU功用或许只需求电脑这样的咱们伙的沧海一粟即可,也不需求杂乱的输入输出设备,在规划上大能够雷厉风行地将用不到的部分砍掉,灵敏地将CPU、时钟发生器(Clock)、随机存储器(Random Access Memory, RAM)、只读存储器(Read-Only Memory, ROM)和需求的外部设备集成起来小型化,这种通过大改观的微处理器体系,其一切部分都集成在了一块芯片上,称为微操控器或单片机(Micro Controller Unit, MCU)。现在MCU是运用最广泛的一种电子操控芯片,其操控程序能够由特别的烧录东西下载到ROM中,行使体系的功用。这些ROM能够使所以PROM、UVEPROM、EEPROM等,若MCU上没有集成ROM,也能够外接ROM。依照体系结构,微处理器体系能够分为冯·诺依曼结构(也称普雷斯顿结构)和哈佛结构,其差异是程序与数据的寄存办法不同,相同地,MCU芯片也能够分为这两种结构,灵敏地满意需求。

MPU

微处理器单元(Micro Processor Unit, MPU),便是把许多CPU集成在一同并行处理数据的芯片。浅显来说,MCU集成了RAM,ROM等设备;MPU则不集成这些设备,是高度集成的通用结构的中央处理器矩阵,也能够认为是去除了集成外设的MCU。

PLD(CPLD/FPGA)

因为现在广泛运用的PLD是CPLD和FPGA,因而把这两种芯片作为比如介绍。前面现已介绍过,CPLD/FPGA的内部结构和CPU彻底不同,内部电路能够被屡次修正,能够依照用户的编程构成不同的组合逻辑电路、时序逻辑电路结构,是一种“全能”的芯片,CPLD/FPGA看起来像一个CPU,其实不然,因为运用CPLD/FPGA完结操控是纯硬件完结,本质上和运用不计其数根本逻辑门建立的数字逻辑电路没有差异。因而能够直接用HDL编程在CPLD/FPGA里建立出一个“CPU”(有时还有硬盒和软核之分,限于篇幅,不再赘述),再做好相应的I/O、总线,便是一个简略的微处理器体系了。可是这样一来,又变成了软件操控,PLD的硬件操控优势化为乌有。故CPLD/FPGA常常和实践的CPU调配运用,在CPLD/FPGA上编写一些较杂乱算法的运算电路,当CPU处理到这些杂乱使命时,就交由CPLD/FPGA进行处理,处理完毕今后再将效果回来给CPU,前进操控体系的全体功用。

ADC、DAC

天然界的物理量分为模仿(Analog)量和数字(Digital)量两种。模仿量在必定范围内的取值是接连的,个数是无量的;数字量在必定范围内的取值是离散的,个数是有限的。核算机只能处理离散的数字量,所以模仿信号有必要通过改换才干交由核算机处理。将天然界的物理量转化为接连改变的电流或电压(故称“模仿”),在满意奈奎斯特采样定理(Nyquist Sampling Theory,也称香农采样定理,Shannon Sampling Theory)的条件下采样,得到时域离散信号,再经量化器(能够是线性量化和非线性量化)量化后数字信号,最终通过一道编码得到二进制的0、1数字信息,才干交由核算机处理。以上的这一道改换称为模数转化(A/D),能够将这部分电路集成到一块芯片上,这便是模数转化电路(Analog Digital Circuit, ADC),相应的也有数模转化(D/A)和数模转化电路(Digital Analog Circuit, DAC)芯片,进行D/A的时分相同要在数学和信息论上满意相关定理。

DSP

数字信号处理器(Digital Signal Processor, DSP)是用来高速处理数字信号的专用芯片。

通过ADC转化好的数字信号,数据量往往很巨大,直接交由CPU处理的功率是不高的,并且CPU还要进行更多的通用核算的使命。因而,常常选用专用的电路来处理数字信号,如数字滤波、快速傅里叶改换、时频剖析、语音信号和图画信号的处理加工等。这些运算往往很杂乱,许多触及复数的累加、累乘运算,举个比如:离散傅里叶改换的核算就十分杂乱,可是运用时域抽取或频域抽取的快速傅里叶改换算法后就能够大大削减运算量,可是电路较为杂乱。将能完结这些杂乱运算的电路集成在一块芯片上,能在一个时钟周期完结一次乘加运算,使其能完结如基2-FFT蝶形运算、音频滤波、图画处理等杂乱运算,这样的芯片叫做DSP。DSP也是一种特别的CPU,特别适宜信号的处理,如3G中的Node B就许多运用了DSP进行信号处理。DSP关于流媒体的处理才干远远的优于CPU,现在手机上的语音信号都是由DSP处理的。现阶段DSP的概念正在变得含糊,如ARM9的架构就不像是一颗CPU,更像是一颗DSP。现在有许多芯片,其上都集成了DSP,GPU,基带处理器等,越来越多的传统上分立的芯片被集成到一同,协同作业曾经进功率,下降能耗,这也是未来的一个趋势。

SoC

跟着半导体技能、移动互联网和智能终端的迅猛开展,传统的微处理器体系的开展现已跟不上年代的潮流,现代信息技能火急地需求一种功用多,功用强,功耗低的芯片来满意越来越多的智能设备的需求。SoC便应运而生。

SoC的全称是System on a Chip,望文生义,便是在一块芯片上集成一整个信息处理体系,称为片上体系或体系级芯片。这个界说现在也不尽清晰,因为不同用处的SoC上集成的部件是不相同的,一般说来,SoC是一个完好的全体,现已具有了整个数字体系的完好功用它也是一种ASIC,其间包括完好的操控体系并有嵌入式的软件。

SoC也代表着一种技能,是一种以确认体系功用为方针,各个模块的软硬件协同开发,最终把开发效果集成为一块芯片的技能。因为功用丰厚,又要求有不俗的功用发挥,SoC已然是功用最为丰厚的硬件,其上集成了CPU、GPU、RAM、ADC/DAC、Modem、高速DSP等各种芯片,有的SoC上还有必要集成电源办理模块,各种外部设备的操控模块,充分考虑各总线的散布运用……现如今,智能手机里的SoC上就集成了以上的部件和基带处理器等许多相关的通讯模块。

SoC的电路比较于传统的微处理器体系愈加杂乱,其对规划和制作工艺的要求天然更上一层楼,对软硬件协同开发的依赖性适当高。迄今为止,在半导体职业名列前茅的企业才有自主规划制作SoC的才干,现在在功用和功耗灵敏的终端芯片范畴,SoC已占有主导地位,人们每天运用的手机里边,就有一颗颗功用微弱,永久在线的SoC在为咱们服务。就连传统的软件大厂微软也推出了根据高通公司的骁龙835渠道的Windows操作体系;并且SoC的运用正在扩展到更广的范畴,SoC在无人机技能、主动驾驶,深度学习等职业也有越来越多的运用,用一块单芯片就能完结完好的电子体系,是半导体职业、IC工业未来的开展方向。