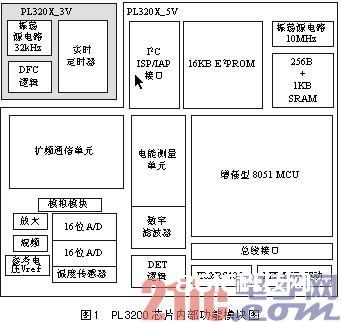

摘 要:PL3200芯片是一种兼容8051指令的SoC芯片,它包含多个功用扩展模块,具有电能丈量、载波扩频等强壮的功用。本文介绍PL3200的首要特色及其载波通讯功用模块,并针对该芯片提出一种电力线载波通讯的完结计划。 关键词:PL3200 直接序列扩频 载波通讯 8051 引 言: 扩频通讯便是待传输的信息数据被伪随机码调制,完结频谱扩展后再传输,接纳端选用相同的伪随机码进行解调及相关处理,康复原始数据。这种通讯办法与一般常见的窄带通讯办法不同,是扩展频谱后进行宽带通讯,再在接纳端进行相关处理,康复成窄带后解调数据。扩频通讯具有强抗搅扰性、抗噪声、抗多径式微、可码分复用等长处,是比较先进的通讯技能。 电力线载波通讯是指用电力线路作为通讯媒体进行通讯,现在被广泛运用于工业主动操控体系、电能办理体系、家用电器体系及核算机终端接口等场合。它运用现成的电力线路来传送数据,无需别的架起通讯线路,也不占用现有的通讯频率资源,特别适用于组成小型局域网和完结大楼内的主动操控。但在电力线上进行信号传输,作业环境恶劣,线路阻抗小、搅扰大且时变性大,沟通噪声对数据的影响及信号的衰减也都很大。扩频通讯办法因其扩频载波信号的带宽一般较大,而受搅扰的频率规模所占份额相对减小,因此能够较好的扫除电力线上的随机搅扰。现在,电力线载波通讯正朝着运用扩频通讯技能的方向开展。 PL3200是具有电力线载波通讯功用的内嵌8051增强型高速微处理器的新式SoC产品。该芯片选用新式的CMOS数/模混合工艺制作,具有成本低、功用高、功用强壮等特色,能够很便利的运用于电力线通讯范畴。 1 PL3200的首要特色 PL3200是内嵌了8051指令的高速微处理器芯片,其软件易于开发,具有8/16位双形式ALU,能够8倍速于规范8051处理器,运转速度快,数据处理能力强。图1为PL3200的基本功用结构框图。

PL3200芯片选用0.35μm超大规模数/模混合CMOS制作工艺,是具有多项知识产权的SoC(System on Chip)规划。该芯片内置高精度数字多功用电能计量电路,计量规范完全符合世界GB/T 17883和GB/T 17215;电流通道内置可程序设定增益放大器(PGA);内置了双通道电流采样、正/负功指示数字逻辑电路;内置扩频通讯调制/解调电路;内置 4%26;#215;32段LCD显现操控/驱动电路或8%26;#215;8段LED显现操控/驱动电路;内置可数字频率校对的实时钟;内置可对电能计量精度和实时钟精度进行温度分段线性补偿的温度传感器;内置2.5V%26;#177;8%电压源基准;内置串行程序存储器编程接口,支撑在体系编程 (ISP);选用5V单电源供电;内置完善的电源电压监测电路。 2 内嵌微处理器部分功用概述 PL3200内嵌的增强型8051兼容微处理器,装备了8/16位ALU、256B+1024B SRAM以及16KB E2PROM、3个8/16位守时器/计数器,1个看门狗守时器以及3个外部中止,为用户供给丰厚的嵌入式资源和抱负的运用开发渠道。其增强型8051兼容微处理器,选用超级指令流水线架构,平等主频情况下,8倍速于规范8051微处理器。别的,该芯片还具有两个全双工UART(通用异步收发器),一个可装备为38kHz的红外通讯形式,另一个可装备为RS485通讯形式,供给了多种便利的数据传输办法。 3 载波通讯模块的原理及功用设置 PL3200芯片内集成的载波通讯单元选用QPSK调制办法,并具有可变伪随机码速率(带宽)的多地址通讯技能。载波通讯单元选用直接序列扩频办法。在扩频接纳的进程中首要包含载波信号的捕获和同步。 捕获是接纳模块在扩频序列准确同步前,查找接纳信号,使接纳信号的扩频序列与本地扩频序列在相位上进入可同步坚持的规模之内,即二者的相位在一个扩频序列码元之内。因为载波通讯单元所选用的扩频伪码具有很强的自相关性,所以通过比较本地伪码和接纳序列之间的相关性与设定阈值的凹凸,就能在捕获进程中止定是否中止伪码的滑动,以完结捕获。捕获完结后进入盯梢阶段,动态地调整本地伪码产生器的时钟速率,使本地伪码能够主动地和接纳到信号的伪随机码坚持准确同步。扩频序列的盯梢电路选用全数字基带推迟确认环(delay locked loop)电路。在载波通讯单元每次置为发送态后,硬件会首先发送40个伪码周期的全“1”序列,用于使接纳端与发送端的伪随机码同步和用于辨认帧头的8 个伪码周期的帧头序列,软件不需要进行相应的处理。在载波通讯单元置为接纳态后,硬件会在每次伪随机码同步后,开端从数据流中查找帧头序列。当检出帧头序列后,才真实开端接纳数据,并以字节的办法送到SSC_BUF寄存器中。在载波通讯单元,每处理一个字节的数据,都是通过SSC_BUF寄存器与CPU之间进行数据交互完结的。 PL3200对扩频数据选用QPSK调制办法,其载波中心频率为120kHz,伪随机码速率可到达30kbps和15kbps。依据伪随机码的速率不同,数据速率可到达1kbps和500bps。因为该芯片选用了63位的Gold/Kasami序列,然后完结了码分多址,其地址数目最多可达40个,其间32个Gold序列,8个Kasami序列,因为运用了扩频技能,可使各地址之间的搅扰减到最小。 载波通讯单元每次由收态转为发态后,CPU应在4ms内将新的待发数据填入到SSC_BUF寄存器中,不然硬件将会在4ms后,主动由发态转为收态。载波通讯单元处于发态时,应该在每次发送缓冲标志为空时,立行将新的待发数据填入SSC_BUF寄存器中。当最终一字节待发数据向SSC_BUF寄存器填入完毕后,CPU进行的数据交换进程完毕。载波通讯单元在悉数数据发送完结后,会主动由发态转为收态(强制的由发态置为收态可能会导致最终一字节数据丢掉)。在接纳端,每次通讯数据包正常接纳完毕后,软件能够通过对载波通讯状况寄存器(00H)的写操作,来强制告诉接纳逻辑从头开端新的数据帧查找。 PL3200载波通讯单元的详细设定,是通过对载波通讯寄存器组(SSC Register Bank)不同地址的寄存器,写入对应的操控字来完结的。设定功用时,先向载波通讯操控字地址挑选寄存器(SSC_ADR)中写入选中的载波通讯寄存器组的地址,再向载波通讯操控字数据寄存器(SSC_DAT)写入设定的操控字。载波通讯寄存器组(SSC Register Bank)各地址对应的寄存器如表1所列。

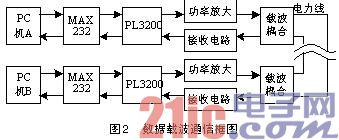

在PL3200的载波通讯寄存器组中,对地址为02H(载波通讯操控寄存器1)、04H(伪随机码捕获门限寄存器)和05H(伪随机码精同步门限寄存器)进行写操作时,要撤销写保护,才能够将数据写入对应的寄存器中。若对寄存器不再进行写操作时,应将写保护使能。撤销写保护的办法是,用程序向 SSC_ADR寄存器写入FFH,选中写保护寄存器的地址,再向SSC_DAT寄存器写入FFH,即可撤销写保护,并由程序向相应的寄存器进行写操作。在对相应的寄存器进行完写操作后,由程序向SSC_ADR寄存器写入FFH,再向SSC_DAT寄存器中写入一非FFH的数据,写保护将会被使能。在载波通讯寄存器组中,00H的寄存器用来指示载波通讯单元处于收态仍是发态,以及数据和帧头的接纳发送标志;02H的寄存器可设置挑选伪码的品种(Kasami 码或是Gold码)、伪随机码的地址挑选位(Kasami码可选8个地址,Gold码可选32个地址)以及伪随机码的速率(30K码速率或15K码速率) 及由此确认的数据速率(1Kbps或500bps);03H的寄存器用来设置伪随机码捕获的门限阈值,在载波通讯单元为接纳态时,设定本地与接纳到的伪随机码序列相位同步的捕获门限值,硬件会按每个伪码周期对本地产生的伪码与接纳到的伪码进行核算,核算的成果与门限值比较,若小于门限值将进行一次相位调整,调整起伏为半个伪码码元宽度,直到高于设定的捕获门限值时,才不再作调整,一般若伪码码率为30K时,捕获门限值将调整至40H左右;05H的寄存器用于设定在接纳状况时,本地与发送端伪随机码序列相位同步的精同步门限值,当高于伪码捕获门限值时,将进行精同步调整,硬件能够辨认本地伪码和接纳到的伪码相位是超前仍是滞后,然后进行向前或向后的相位调整,当小于设定的门限值时,以为精同步现已同步,将不再进行调整。 4 运用于扩频载波通讯的规划 运用PL3200的扩频载波通讯功用,规划一个数据收发渠道。数据由PC机A的串口RS232宣布,经MAX232电平转化后,送入芯片 PL3200。在芯片中,先由扩展串口UART接纳数据,经内嵌8051的操控处理,送入载波通讯单元,对数据进行直接序列扩频,扩频后的信号经 120kHz的载波频率调制后输出。 此信号经功率放大后可由线圈耦合到低压电力线上,完结电力线载波通讯。在接纳端,先通过线圈将电力线上的信号耦合出来,对信号进行滤波限幅,将限幅后的信号送入PL3200进行捕获、同步及解扩处理,经由内嵌8051的操控,由芯片的UART串口,经电平转化后,送到PC机B的RS232接口,进入PC 机。反之,B的数据按相反的途径传送给A。整个渠道的结构框图如图2所示。

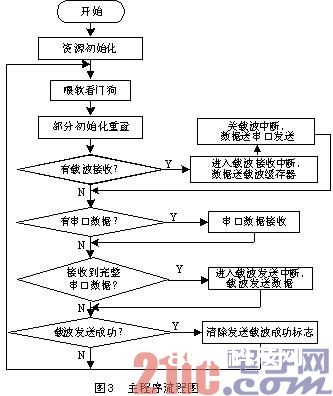

载波通讯为总线办法通讯,所以载波单元的常态有必要设置为接纳态,对载波模块可分配不同的通讯地址。因为载波通讯速率相对于主频低许多,为进步CPU功率,数据的接纳和发送均规划为中止办法处理,每次进入中止,完结对数据接纳或发送的处理操作。 依照数据的传送进程,用C言语编写芯片的操控程序,规划主程序流程如图3所示。

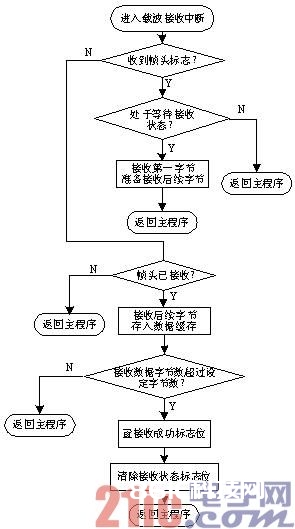

体系在上电后进入主程序,在主程序的延时阶段进行复位操作,随后进行资源初始化操作,对寄存器作初始化设置。为了避免程序因为意外原因此导致死机,PL3200专门规划了一套看门狗电路,当程序死机后,通过一段由寄存器操控的守时时刻后,看门狗电路从头复位8051。所以,程序在运转时,每隔一段时刻距离,就要不断地复位看门狗电路。将复位看门狗电路的操作编成中止子程序,每隔一段时刻后对变量赋值,复位看门狗电路,此即喂狗操作。在进行部分寄存器的初始化重置后,程序顺次查看载波接纳中止和串口接纳中止。如有载波数据,则进入载波接纳中止,将数据送入载波缓存数组,随后送串口发送。如有串口数据,则依照协议格局将数据取出,存入串口数据缓存数组,待数据接纳完好后,进入载波发送中止,将缓存中的数据送载波发送,成功后将标志位铲除。主程序再次进入循环,检测载波中止或串口中止。主程序对中止进行循环检测,直到有数据中止产生,进入中止处理程序。 当载波通讯单元中止使能位有用时,CPU的中止2将会被装备成在载波通讯中,用于数据字节发送或接纳的中止。产生载波中止时,程序查询载波通讯寄存器地址00H的bit0位:当该位为0时,进入载波接纳状况;当该位为1时,进入载波发送状况。 载波接纳中止的流程如图4所示。在载波接纳的进程中,先要查询载波通讯寄存器00H的帧头标志位,如收到帧头,且芯片处于等候接纳状况,则接纳数据的榜首字节;如接纳的不是帧头,则判别帧头是否已被接纳,而持续接纳后续字节。最终,将接纳的数据送入载波数据缓存数组,如接纳字节数超越设定值,则置接纳成功位给串口,并铲除正在接纳状况位,完毕载波中止,进入串口发送中止。

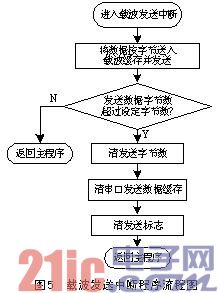

载波发送中止的流程如图5所示。当串口接纳完数据后,置载波发送标志位,进入载波发送中止。中止程序将串口缓存数据组中的数据按字节送入载波缓存发送,直至载波发送的字节数超越设定字节数,完毕载波发送,并清串口缓存数据组的数据。在铲除载波发送标志后,完毕中止,回来主程序,进行下一轮的发送接纳查询。

结 语 运用SoC芯片PL3200规划电力线载波扩频数据渠道,运用极端简洁,运用C言语来进行程序规划非常便利。一起,因为运用灵敏的ISP编程办法,使程序的修正及下载也非常便利,能够灵敏的进行功用扩展。