尽管跟着技术的开展,现代的数字芯片现已集成了越来越多的功用,可是关于略微杂乱一点的体系来说,许多时分独自一个芯片很难完结一切的作业,这就需求和其它芯片合作起来作业。比方咱们现在的CPU的处理才干越来越强,许多CPU内部乃至集成了显现处理的功用,可是依然需求合作外部的内存芯片来存储暂时的数据、需求合作桥接芯片扩展硬盘、USB等外围接口;现代的FPGA内部也能够集成CPU、DSP、RAM、高速收发器等,但有些场合或许还需求合作专用的DSP来进一步进步浮点处理功率、合作额定的内存芯片来扩展存储空间、合作专用的物理层芯片来扩展网口、USB等,或许需求多片FPGA互连来进步处理才干。所以的这一切,都需求用到相应的总线来完成多个数字芯片间的互连。假如咱们把各个功用芯片幻想成人体的各个功用器官的话,总线便是血脉和经络,通过这些途径,各个功用模块间才干进行有用的数据交换和协同作业。

咱们常常运用到的总线依据数据传输方法的不同,能够分为并行总线和串行总线。

并行总线:

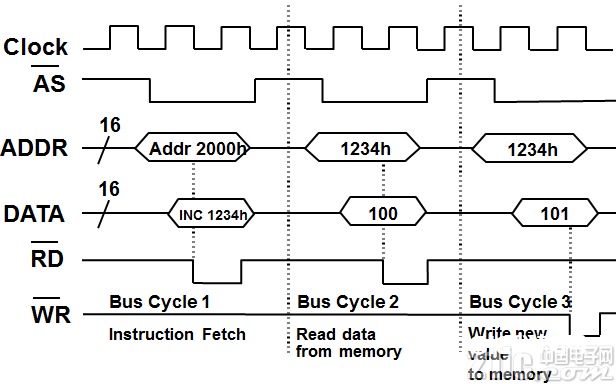

并行总线是数字电路里最早也是最遍及选用的总线结构。在这种总线上,要传输的数据线、地址线、操控线等都是并行传输,比方要传输8位的数据宽度,就需求8根数据信号线一起传输,假如要传输32位的数据宽度就需求32根数据信号线一起传输。除了数据线以外,假如要寻址比较大的地址空间,还需求许多根地址线的组合来代表不同的地址空间。下图是一个典型的微处理器的并行总线的作业时序,其间包含了1根时钟线、16根数据线、16根地址线以及一些读写操控信号。

许多经典的处理器都选用了并行的总线架构。比方咱们熟知的51单片机就选用了8根并行数据线和16根地址线;CPU的开山祖师,Intel 公司的8086微处理器开端推出时具有16根并行数据线和16根地址线;现在许多嵌入式体系中广泛运用的ARM处理器则大部分运用32根数据线以及若干根地址线。

并行总线的最大优点是总线的逻辑时序比较简单,电路完成起来比较简单,可是缺陷也是十分显着的。比方并行总线的信号线数量十分多,会占用许多的管脚和布线空间,因而芯片和PCB板的尺度很难完成小型化,特别是假如要用电缆进行远距离传输时,因为信号线的数量十分多,使得电缆变得十分贵重和粗笨。

选用并行总线的别的一个问题在于总线的吞吐量很难继续进步。关于并行总线来说,其总线吞吐量=数据线位数×数据速率。咱们能够通过进步数据线的位数来进步总线吞吐量,也能够通过进步数据速率来进步总线吞吐量。以个人核算机里从前十分盛行的PCI总线为例,其最早推出时总线是32位的数据线,作业时钟频率是33MHz,其总线吞吐量=32bit×33MHz;后来为了进步其总线吞吐量推出的PCI-X总线,把总线宽度扩展到64位,作业时钟频率最高进步到133MHz,其总线吞吐量=64bit×133MHz。下图是PCI插槽和PCI-X插槽的一个比照,能够看到PCI-X因为运用了更多的数据线,其插槽更长(来历:网络图片)。

可是跟着人们关于总线吞吐量的要求的不断进步,这种进步总线带宽的方法遇到了瓶颈。首要因为芯片尺度和布线空间的约束,64位数据宽度现已几乎是极限了。别的一方面,这64根数据线是共用一个采样时钟,为了确保一切的信号都满意其树立坚持时刻的要求,在PCB上布线、换层、拐弯时需求确保准确等长。而总线作业速率越高,关于各条线的等长要求就越高,关于这么多根信号要完成等长的布线是很难做到的。

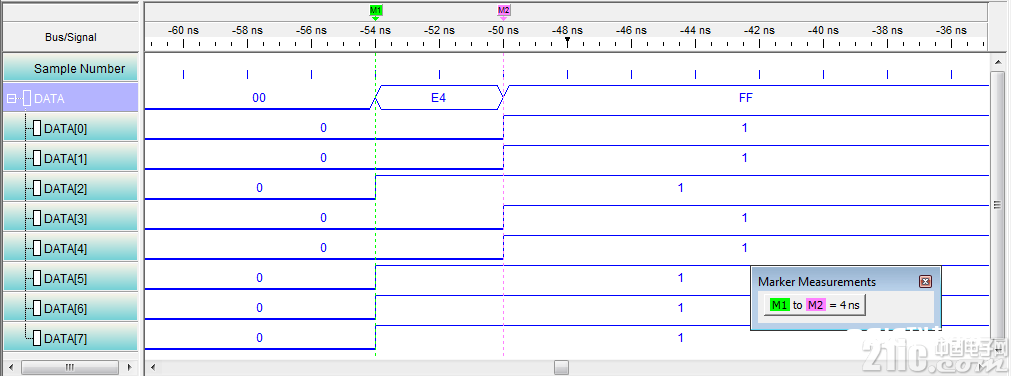

下图是用逻辑分析仪收集到的一个实践的8位总线的作业时序,咱们能够看到在数据从0x00跳变到0xFF状况过程中,这8根线实践并不是准确一起跳变的。

关于并行总线来说,更丧命的是这种总线上一般挂有多个设备,且读写共用,各种信号分叉形成的反射问题使得信号质量进一步恶化。

串行总线:

为了处理并行总线占用尺度过大且对布线等长要求过于严苛的问题,跟着芯片技术的开展和速度的进步,越来越多的数字接口开端选用串行总线。所谓串行总线,便是并行的数据在总线上不再是并行地传输,而是时分复用在一根或几根线上传输。比方在并行总线上传输1个Byte的数据宽度需求8根线,而假如把这8根线上的信号时分复用在一根线上就能够大大削减需求的走线数量,一起也不需求再考虑8根线之间的等长联系。

选用串行总线今后,就单根线来说,因为上面要传输本来多根线传输的数据,所以其作业速率一般要比相应的并行总线高许多。比方曾经核算机上的扩展槽上广泛运用的PCI总线选用并行32位的数据线,每根数据线上的数据传输速率是33Mbit/s,演变到PCI-E(PCI-Express)的串行版别后每根线上的数据速率至少是2.5Gbit/s(PCI-E 1代规范),现在PCI-E的数据速率现已达到了5Gbit/s(PCI-E 2代规范)或8Gbit/s(PCI-E 3代规范)。选用串行总线的另一个优点是在进步数据传输速率的一起节省了布线空间,一起芯片的功耗也降低了,所以在现代的电子设备中,当需求进行高速数据传输时,运用串行总线的越来越多。

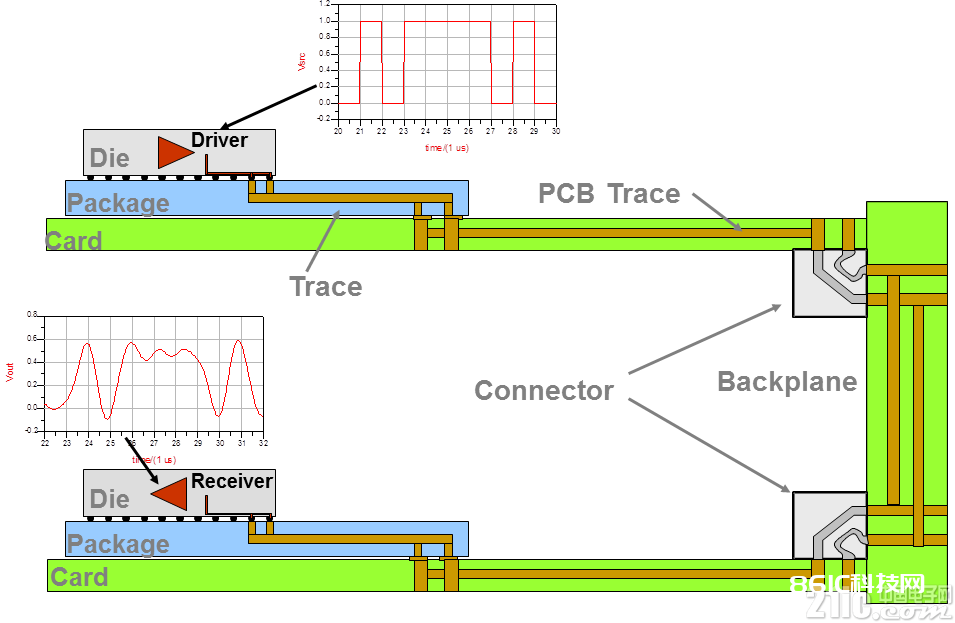

数据速率进步今后,关于阻抗匹配、线路损耗和颤动的要求就更高,稍不留意就很简单发生信号质量的问题。下图是一个典型的1Gbps的信号从发送端通过芯片封装、PCB板、衔接器、背板传输到接纳端的信号途径,从中咱们能够看到在发送端的挨近抱负的0、1跳变的数字信号抵达接纳端后因为高频损耗、反射等的影响信号波形现已变得十分恶劣,所以串行总线的规划关于数字电路的工程师来说是个很大应战。

运用串行总线的设备的体积、功耗和数据传输速度都比运用并行接口的设备更有优势,因而得到了广泛的运用。比方曾经在核算机上广泛运用的衔接打印机的DB25的并口现已被USB和网口替代,曾经衔接硬盘的40pin的PATA接口现已被串行的SATA接口替代,曾经核算机上的PCI扩展槽现已被PCI-Express替代。可是如前所述,选用串行总线今后信号的数据速率一般都会有几倍乃至几百倍的进步,关于电路的规划和测验都提出了很高的要求,因而需求规划和测验工程师把握许多的高速规划的相关常识和技术。