导言

在CCD图画采会集,需求对图画收集体系的功用进行评价,而因为CCD相机的研发时间长,研发本钱高,而且不易于控制,因而,研发出开发周期短、易于控制的图画方针发生器成为评价图画收集体系中很重要的一步。

图画方针发生器的规划首要是根据数字图画的常识,使用FPGA的大容量、高集成度、数据安稳等长处来规划图画数据流,完成CCD相机的大部分功用。

该图画方针发生器使用可编程逻辑器材的优秀功用,选用VHDL言语编程,而且在盛行的FPGA芯片上完成,它能发生灰度阶图画、静态方针图画和运动方针图画。在静态方针图画和运动方针图画中,布景区域和方针区域的对比度反差很大。输出的图画的像素选用12位灰度级标明,发生的图画巨细是2K×1K。

1、规划原理

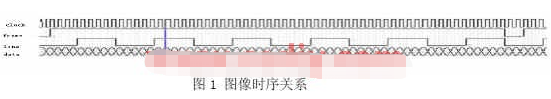

在图画信号的生成中,最重要的是时序联系,首要的信号有:像素时钟、帧信号、行信号和数据信号。以6×6巨细的图画为例,它们和像素数据构成的时序联系如下。在图1中,帧信号(frame)包含6个行(line)有用信号,同时行信号又包含6个有用的时钟信号,这样便能够生成简略的6×6巨细的图画。使用这个原理,便能够生成2K×1K巨细的图画。

2、硬件规划描绘

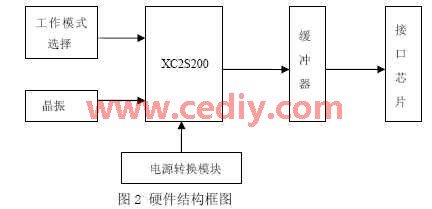

整个体系的结构框图如图2所示。

在图2中,作业形式挑选用来决议体系是作业在灰度阶图画、静态方针图画仍是运动方针图画的形式;FPGA选用Xilinx公司的XC2S200,该芯片的最高作业频率为200MHz,集成体系门为20万门,5292个逻辑单元,用来发生一切的图画数据信号;该图画方针发生器的接口选用两种办法:LVDS接口和Camera Link接口,其间LVDS接口芯片是美国国家半导体公司的DS90C031,Camera Link接口芯片是该公司的DS90CR283。

3、图画数据的规划

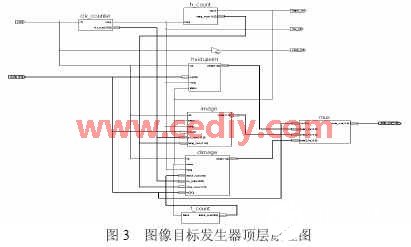

该规划选用模块化规划办法,先用VHDL生成底层模块:灰度阶图画发生模块、静态方针图画发生模块和运动方针图画发生模块等,然后使用原理图输入法将各底层模块调入顶层中,构成整个图画方针发生器,最终的图画方针发生器的顶层原理图如图3所示。

图画方针发生器首要由以下几个模块组成:

1) 时钟计数模块

该模块是一个模2147计数器,在对时钟计数的过程中计数器计到2047,就会发生一个低电平,标明发生一行图画,低电平保持100个时钟周期,即行消隐期是100个时钟周期。

2) 行计数模块

行计数模块是一个模1123计数器。对行信号计数的过程中,计到1023,输出一个低电平,阐明发生一帧完好的图画,该低电平保持50个行周期,即场消隐期是50个行周期。

3) 灰度阶图画发生模块

当m《3:0》=“0000”时,图画方针发生器作业在灰度阶图画输出的形式下。灰度阶图画即图画像素的灰度值逐次加1,加至最大(212),再回来至0,然后逐次循环。

4) 静态方针图画发生模块

当m《3:0》=“0001”时,图画方针发生器作业在发生静态方针图画形式下。

静态方针图画发生模块的输入首要是行计数器模块和时钟计数模块的输出,输出首要是图画灰度值数据。静态方针图画选用时钟计数模块和行计数模块发生的地址(行数和列数)来界定每一方针的巨细,每一个图画方针块的巨细是100×100,在该区域内,图画灰度值全为1,在该区域外为布景区域,图画灰度值全为0。

5)图画帧数判别模块

图画帧数判别模块首要是根据本规划的要求规划的一个模11计数器,确保11幅图画循环呈现。图画帧数判别模块的首要输入信号是图画的帧信号,帧信号是一幅完好图画的标志,当检测到帧信号的高电平跳变沿,阐明开端一帧新的图画数据。

6) 运动方针图画发生模块

运动方针图画发生模块以图画帧判别模块模块、时钟计数模块、行计数模块的输出做为输入,其间,时钟计数模块和行计数模块的输出发生列地址和行地址,图画帧数判别模块的输出能够确保11帧图画循环呈现,每一帧图画的方针区域都不相同,这样便能够发生运动方针图画。在每一帧图画中,由时钟计数器和行计数器发生的地址来界定方针区域的规模,在该区域内,像素灰度值全为1,为方针区域,在该区域外,像素灰度值全为0,为布景区域。输出是12位图画灰度值数据。该模块发生的方针区域巨细是100×50 。

最终,咱们用原理图输入法将上述生成的模块调入顶层原理图编辑器中,最终完好的图画方针发生器如上面的图3所示。

定论

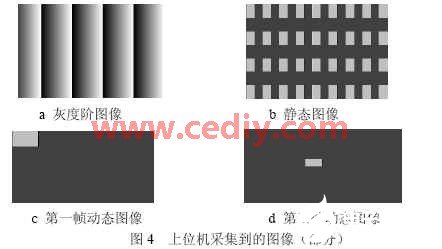

将本图画方针发生器和CL160图画收集卡相连,在上位机收集得到灰度阶图画、静态图画和榜首、第三帧动态图画如图4所示。

根据FPGA的图画方针发生器具有结构简略,开发周期短,数据安稳等长处,能敏捷投入实践使用之中。该图画发生器具有CCD相机常用的LVDS和Camera Link接口,能和许多常用的具有这两种接口的图画收集卡衔接,具有很大的通用性,只需求修正部分时序就能够满意其他的需求,具有很好的可移植性。

在实践的图画收集体系的评价中,使用该方针发生器验证了图画收集体系并不存在丢帧、丢点等现象,在图画存储中,还经过该方针发生器来检测存储速度是否能满意要求,在实践使用中,发现因为数据传输速率大,发现存储速度不能满意要求,后经过改善存储器存储区安排来满意存储速度的要求。

责任编辑:gt