1 导言

CCD(Charge Coupled Devices——电荷耦合器材)具有尺度小、精度高、功耗低、寿命长及电子自扫描等长处,在图画传感和非触摸丈量范畴得到广泛的运用。因为CCD的转化功率、信噪比等光电特性只要在适宜的时序驱动下才干到达规划所规则的最佳值,输出安稳牢靠的信号,因而,驱动电路的规划也就成为其运用中的关键问题之一。不同厂家、不同类型CCD器材的驱动时序各不相同,使CCD的驱动电路很难规范化和产品化。笔者规划的依据FPGA的驱动电路是可再编程的,假如要改动驱动电路的时序,添加或削减某些功用,只需对器材从头编程,在不改动任何硬件的情况下可完成驱动电路的更新换代。

2 CCD作业参数和时序剖析

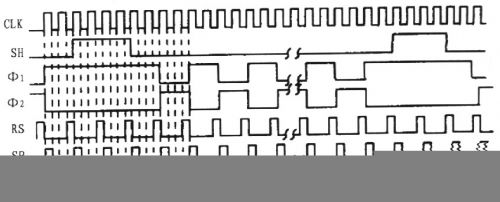

依据工程项目的技能要求,本体系选用日本TOSHIBA公司的TCDl208AP型电路作为传感器。该器材具有优秀的光电特性,有2 160个像元,其驱动信号的时序如图l所示。

由TCDl208AP的时序图能够看出,TCDl208AP选用二相驱动脉冲作业,时序脉冲驱动电路供给4路作业脉冲,即光积分脉冲SH,电荷搬运脉冲φ1、φ2,输出复位脉冲RS。体系供给的主时钟频率CLK为4 MHz,设定数据输出频率为1 MHz。TCDl208AP的典型最佳作业频率为l MHz,该器材具有2160位有用像元,正常作业时要有52个虚设单元输出(DUMMY 0UTPUTS)信号(含暗电流信号)。因为该器材是二列并行传输,所以在一个周期内至少要有1 106(2 212/2=1 106)个φ1脉冲,即TSH>1106Tφ1。别的,由时序图能够看出,当SH信号为高电平期间,CCD堆集的信号电荷包经过搬运栅进入移位寄存器,移位脉冲φ1、φ2要求坚持一个高和低的电平状况。

3 FPGA器材的挑选

依据规划要求和工程需求,本规划选用Altera公司Cyclone系列产品中的EPlCl2Q240C8型嵌入式可编程逻辑器材。EPlCl2Q240C8选用依据1.5 V、0.13μm及全层铜SRAM工艺,其密度添加至20 060个逻辑元件(LE),RAM添加至288 KB。它具有用于时钟的锁相环、DDR SDR和快速周期RAM(FCRAM)存储器所需的专用双数据率(DDR)接口,具有在体系可编程特性。其装备办法有被迫型和主动型,被迫型装备是在上电后由计算机经过编译后发生sof文件运用专用的下载电缆装备电路。主动型装备是在上电后由专门的可编程装备电路(EPCS4)主动对EP1C12Q240C8电路进行装备。

4 CCD驱动电路规划

驱动电路的功用是发生确保发生CCD器材正常作业的搬运时钟、传输时钟、采样坚持时钟、复位时钟、信号处理电路和A/D转化电路所需求的同步脉冲、像元时钟和箝位脉冲。只要驱动脉冲与CCD的杰出合作才干充分发挥CCD的光电转化特性,输出安稳牢靠的光电信号。

曾经选用数字逻辑电路来规划线阵CCD驱动电路,因为选用多个计数器、触发器和门电路,电路杂乱,抗干扰能力差,并且时序较难合作,不易调试。假如选用FPGA驱动办法发生驱动信号,体系用同一时钟对这4路驱动信号进行操控,以确保相互之间的确认时间联系,然后运用分频器对时钟脉冲分频以发生各路驱动信号所需的波形,发生如图1所示的驱动信号就便利得多。

该体系的规划选用Altera公司的QUARTUSⅡ开发体系。QUARTUSⅡ开发体系是一种全集成化的可编程逻辑规划环境,它支撑硬件描绘言语(VHDL)、状况图和原理图三种输入办法,履行编译、逻辑归纳、仿真以及编程等功用。规划进程包含4个阶段:规划输入、规划完成、规划验证和器材编程,如图2所示。整个流程是一个输入、完成、验证的递归进程,直到规划正确和完好。

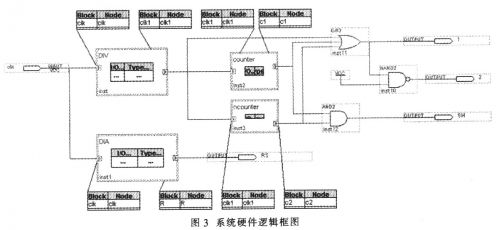

原理图输入办法简略直观,也是最常用的。如选用硬件描绘言语的输入办法如VHDL或Verilog,其可移植性和可读性都好,但归纳构成的数据格式文件往往比原理图输入办法更占可编程器材的资源。为了进步芯片的运用率,一起选用原理图输入办法还能够生成新的特别功用模块,鉴于体系规划不大,因而选用原理图输入办法进行本体系的规划。因为TCDl208AP是二相驱动办法,依据TCDl208AP驱动信号的时序联系,能够确认φl=φ2=0.5 MHz,输出复位脉冲RS=l MHz。

在确认了SH、φ1、φ2和RS的参数后,能够依据它们之间的时序联系规划硬件逻辑框图。各路脉冲分别为RS=1 MHz,占空比为l:4,方波;φ1=φ2=0.5 MHz,占空比为1:l,方波,φ1、φ2在并行搬运时有一个大于SH=1的宽脉冲。其间的各个模块选用VHDL言语进行规划,如图3所示。

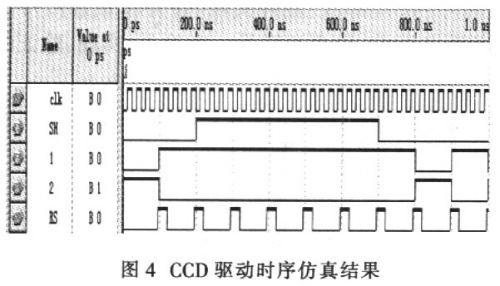

编译后,最终得到仿真的波形成果如图4所示。

5 结束语

本规划选用QUARTUSⅡ开发体系完成编程,完成了电路功用的规划、时序归纳与剖析及文本和图形输入,并依据工程需求将成果下载到Altera公司的Cyclone系列FPGA芯片EPlCl2Q240C8中发生CCD驱动时序,不光得到了杰出的CCD输出作用,并且大大简化电路规划,进步牢靠性,下降功耗,加速研制速度。