前面评论了GPIO数据存放器和屏蔽结构的用法,这儿再接着评论一下涉及到GPIO的其它存放器用法。从GPIO界说的结构体中能够看出,除了前面评论的DATA存放器以外,还剩下有8个存放器,偏移地址从0x8000到0x801C,它们都在GPIO设置中起着重要的效果,下面就逐个进行评论。

首先看DIR存放器,其偏移地址为0x8000,特点为可读可写,它担任GPIO引脚的方向,即引脚是用做输入仍是输出,由该存放器的设置来决议。尽管DIR存放器也是32位结构,但由于LPC1114每组只需12个引脚,所以只用了其间的低12位。当位为0 时做输入,为1时做输出,12位与12个引脚逐个对应,每位设置对应一个引脚。在默许状况下DIR的值为全0,所以在默许状况下一切的引脚为输入状况。要改动引脚状况,可经过写DIR存放器对应的位来完成。例如,要把端口0的第1、3、5脚设为输入,其它全为输出,履行句子“LPC_GPIO0->DIR = 0xFD5;”就能够了。

接下来看IS存放器,其偏移地址为0x8004,特点为可读可写,它担任GPIO引脚外部中止的触发方法,即引脚呼应中止是电平触发仍是边缘触发,由该存放器的设置来决议。IS存放器也只用了32位中的低12位,当位为0 时挑选边缘触发,为1时挑选电平触发,12位与12个引脚逐个对应,每位设置对应一个引脚。在默许状况下IS的值为全0,所以在默许状况下一切的引脚在外部中止时是边缘触发方法。要改动引脚中止的触发方法,可经过写IS存放器对应的位来完成。例如,要把端口1的第11脚设为电平触发,履行句子“LPC_GPIO1->IS |= 0x800;”就能够了。别的,在挑选触发方法时要注意,若挑选了电平触发,必需求考虑是否会在触发电平坚持期间引发屡次外部中止呼应。一般状况下,挑选边缘触发方法就不会存在这个问题。

接着看IEV存放器,其偏移地址为0x800C,特点为可读可写,它担任合作上面的IS存放器来确认详细的触发方法。即:若IS装备为边缘触发方法,则IEV担任挑选是上跳沿仍是下跳沿;若IS装备为电平触发方法,则IVE担任挑选是高电平触发仍是低电平触发。IVE存放器也只用了32位中的低12位,当位为0 时挑选下跳沿触发或低电平触发方法,为1时挑选上跳沿触发或高电平触发方法,12位与12个引脚逐个对应,每位设置对应一个引脚。在默许状况下IEV的值为全0,所以在默许状况下一切的引脚在外部中止时是下跳沿触发或低电平触发方法。要改动引脚中止的详细触发方法,可经过写IEV存放器对应的位来完成。例如,要把端口2的第5脚设为高电平触发,履行两句句子“LPC_GPIO1->IS |= 0x020;LPC_GPIO1->IVE |=0x020;”就能够了。别的要着重一点,IEV存放器有必要和IS存放器合作运用。一般来说,应先装备IS,再装备IVE。

接下来是IBE存放器,其偏移地址为0x8008,特点为可读可写,它担任GPIO在外部中止时,用来挑选是否运用双边缘触发方法。在某些特别运用的当地(比方需求一起捕获脉冲的上跳沿和下跳沿时),需求在程序中频频转化触发方法,而在LPC1114中由于有IBE存放器,所以操作就简略多了,只需经过设置IBE存放器来使能对应引脚的双沿触发方法就能够了。IBE存放器也只用了32位中的低12位,当位为0 时封闭双沿触发,此刻的触发方法由IEV存放器决议。为1时敞开双沿触发,12位与12个引脚逐个对应,每位设置对应一个引脚。在默许状况下IBE的值为全0,所以在默许状况下一切的引脚在外部中止时双沿触发方法处于封闭状况。要使能双边缘触发方法,可经过写IBE存放器对应的位来完成。例如,要把端口3的第1脚设为双沿触发方法,履行两句句子“LPC_GPIO2->IS &= ~0x002;LPC_GPIO2->IBE |=0x002;”就能够了。别的有一点需求着重一下,假如某引脚被IBE设置为双边缘触发,则其对应的IEV设置就不起效果了。还有便是IBE存放器也有必要和IS存放器合作运用,一般来说,应先装备IS,再装备IBE。

下一个是IE存放器,其偏移地址为0x8010,特点为可读可写,它担任使能GPIO引脚的外部中止功用。该存放器也只用了32位中的低12位,当位为0 时中止功用被屏蔽(即中止不使能),为1时中止功用未屏蔽(即中止使能),12位与12个引脚逐个对应,每位设置对应一个引脚。在默许状况下IE的值为全0,所以在默许状况下一切的引脚不运用外部中止(中止悉数被屏蔽)。要使能某引脚的外部中止功用,可经过写IE存放器对应的位来完成。例如,要敞开端口0的第1引脚中止功用,履行句子“LPC_GPIO0->IE = 0x002;”就能够了。

再下一个是RIS存放器,其偏移地址为0x8014,特点为只读,它担任查询哪个GPIO引脚上有中止请求。该存放器也只用了32位中的低12位,当位为0 时标明对应引脚上没有外部中止请求产生,为1时标明对应引脚上有外部中止请求产生,12位与12个引脚逐个对应,每位设置对应一个引脚。在复位时RIS的值为全0,标明一切的引脚复位时都没有外部中止请求产生。假如某个引脚上RIS对应的值为1,则标明该引脚上有契合条件的中止请求产生,此刻若对应的IE位也为1(即敞开该引脚的中止功用),就会产生该引脚的中止呼应。但假如对应的IE位不为1,则不会呼应中止。

接下来是MIS存放器,其偏移地址为0x8018,特点为只读,它和上面的RIS存放器根本是相同的,能够用于查询是否有中止呼应。不同点在于,RIS是只需引脚上满意中止触发条件它对应的位就被置1,但它不必定被呼应,由于它有或许被屏蔽了(例如对应的IE位没有被置1),因而RIS不能断定中止是否呼应了,而只能断定有契合条件的中止请求产生;但在MIS存放器中,若相应的位被置1了,则阐明这个中止必定被呼应了,因而能够经过程序查询MIS存放器的方法来判别是否有中止被呼应,是哪个引脚上的中止被呼应。其实MIS存放器表征的便是屏蔽之后的中止状况,它也只用了32位中的低12位,当位为0 时标明对应引脚上没有外部中止呼应,为1时标明对应引脚上有外部中止呼应,12位与12个引脚逐个对应,每位设置对应一个引脚。

最终一个是IC存放器,其偏移地址为0x801C,特点为只写,它用来铲除中止边缘检测逻辑。它也只用了32位中的低12位,当位为0 时不起效果,即对外部中止无任何影响,为1时标明对应引脚上的边缘触发端口位被清零,12位与12个引脚逐个对应,每位设置对应一个引脚。之所以要设IC存放器,是由于在中止呼应后(仅边缘型触发),在RIS和MIS存放器中相应的位不会被主动清零,因而在中止呼应后需求在IC存放器的相应位中写1来进行清零,以确保后续中止的正常触发。

以上是GPIO中各存放器功用的根本介绍,至于详细的运用方法,会在后边中止一章中做详细评论,这儿先不赘述了。

接下来评论一下GPIO端口引脚的装备。从第一章中现已知道,LPC1114引脚复用的许多,除了第0端口中的3、第2端口中的2~10和第3端口中的4、5引脚外,其他的引脚都具有第二功用。乃至包含复位端RESET都复用在了GPIO0_0引脚。为了完成引脚上各复用功用间的切换,在处理器内部专门设立了一个引脚装备存放器IOCON。用户能够经过IOCON来装备每一个I/O的下列功用特性:

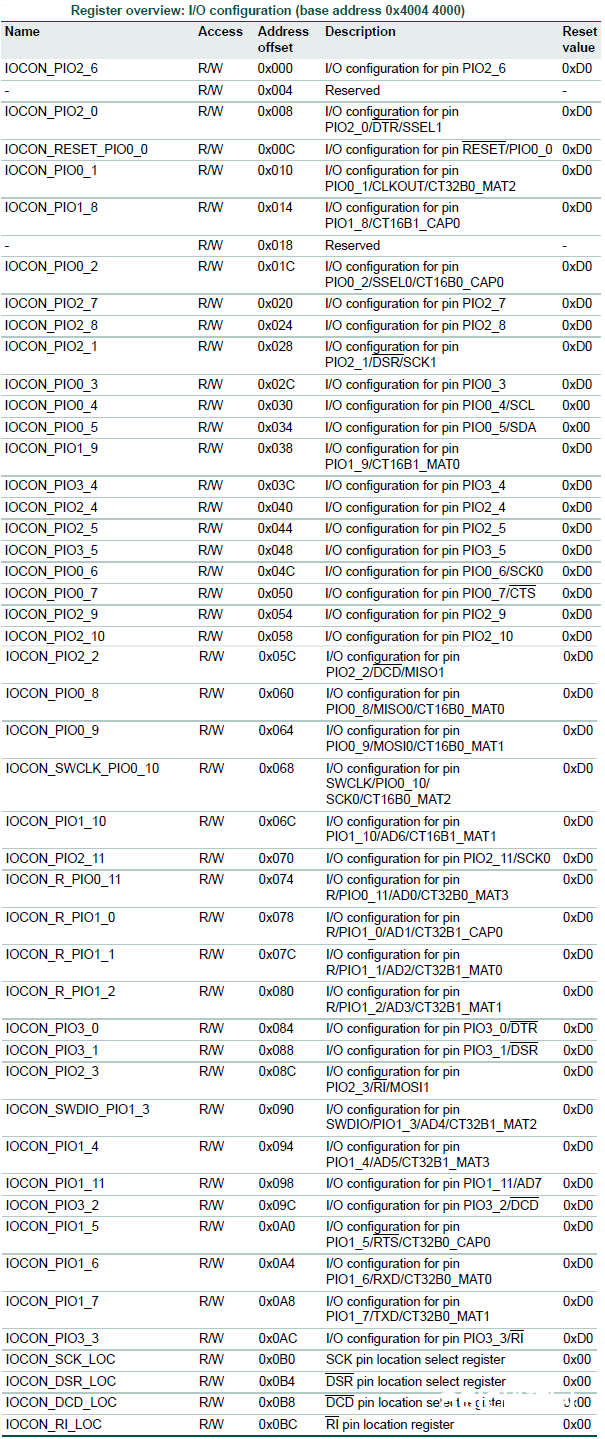

从表中能够看出,IOCON存放器的基址为0x40044000,坐落内存地图中的ABP模块内。它所对应的结构体界说如下:

{

__IO uint32_t PIO2_6; /*!< Offset: 0x000 (R/W) I/O configuration for pin PIO2_6 */

uint32_t RESERVED0[1];

__IO uint32_t PIO2_0; /*!< Offset: 0x008 (R/W) I/O configuration for pin PIO2_0/DTR/SSEL1 */

__IO uint32_t RESET_PIO0_0; /*!< Offset: 0x00C (R/W) I/O configuration for pin RESET/PIO0_0 */

__IO uint32_t PIO0_1; /*!< Offset: 0x010 (R/W) I/O configuration for pin PIO0_1/CLKOUT/CT32B0_MAT2 */

__IO uint32_t PIO1_8; /*!< Offset: 0x014 (R/W) I/O configuration for pin PIO1_8/CT16B1_CAP0 */

uint32_t RESERVED1[1];

__IO uint32_t PIO0_2; /*!< Offset: 0x01C (R/W) I/O configuration for pin PIO0_2/SSEL0/CT16B0_CAP0 */

__IO uint32_t PIO2_7; /*!< Offset: 0x020 (R/W) I/O configuration for pin PIO2_7 */

__IO uint32_t PIO2_8; /*!< Offset: 0x024 (R/W) I/O configuration for pin PIO2_8 */

__IO uint32_t PIO2_1; /*!< Offset: 0x028 (R/W) I/O configuration for pin PIO2_1/nDSR/SCK1 */

__IO uint32_t PIO0_3; /*!< Offset: 0x02C (R/W) I/O configuration for pin PIO0_3 */

__IO uint32_t PIO0_4; /*!< Offset: 0x030 (R/W) I/O configuration for pin PIO0_4/SCL */

__IO uint32_t PIO0_5; /*!< Offset: 0x034 (R/W) I/O configuration for pin PIO0_5/SDA */

__IO uint32_t PIO1_9; /*!< Offset: 0x038 (R/W) I/O configuration for pin PIO1_9/CT16B1_MAT0 */

__IO uint32_t PIO3_4; /*!< Offset: 0x03C (R/W) I/O configuration for pin PIO3_4 */

__IO uint32_t PIO2_4; /*!< Offset: 0x040 (R/W) I/O configuration for pin PIO2_4 */

__IO uint32_t PIO2_5; /*!< Offset: 0x044 (R/W) I/O configuration for pin PIO2_5 */

__IO uint32_t PIO3_5; /*!< Offset: 0x048 (R/W) I/O configuration for pin PIO3_5 */

__IO uint32_t PIO0_6; /*!< Offset: 0x04C (R/W) I/O configuration for pin PIO0_6/SCK0 */

__IO uint32_t PIO0_7; /*!< Offset: 0x050 (R/W) I/O configuration for pin PIO0_7/nCTS */

__IO uint32_t PIO2_9; /*!< Offset: 0x054 (R/W) I/O configuration for pin PIO2_9 */

__IO uint32_t PIO2_10; /*!< Offset: 0x058 (R/W) I/O configuration for pin PIO2_10 */

__IO uint32_t PIO2_2; /*!< Offset: 0x05C (R/W) I/O configuration for pin PIO2_2/DCD/MISO1 */

__IO uint32_t PIO0_8; /*!< Offset: 0x060 (R/W) I/O configuration for pin PIO0_8/MISO0/CT16B0_MAT0 */

__IO uint32_t PIO0_9; /*!< Offset: 0x064 (R/W) I/O configuration for pin PIO0_9/MOSI0/CT16B0_MAT1 */

__IO uint32_t SWCLK_PIO0_10; /*!< Offset: 0x068 (R/W) I/O configuration for pin SWCLK/PIO0_10/SCK0/CT16B0_MAT2 */

__IO uint32_t PIO1_10; /*!< Offset: 0x06C (R/W) I/O configuration for pin PIO1_10/AD6/CT16B1_MAT1 */

__IO uint32_t PIO2_11; /*!< Offset: 0x070 (R/W) I/O configuration for pin PIO2_11/SCK0 */

__IO uint32_t R_PIO0_11; /*!< Offset: 0x074 (R/W) I/O configuration for pin TDI/PIO0_11/AD0/CT32B0_MAT3 */

__IO uint32_t R_PIO1_0; /*!< Offset: 0x078 (R/W) I/O configuration for pin TMS/PIO1_0/AD1/CT32B1_CAP0 */

__IO uint32_t R_PIO1_1; /*!< Offset: 0x07C (R/W) I/O configuration for pin TDO/PIO1_1/AD2/CT32B1_MAT0 */

__IO uint32_t R_PIO1_2; /*!< Offset: 0x080 (R/W) I/O configuration for pin nTRST/PIO1_2/AD3/CT32B1_MAT1 */

__IO uint32_t PIO3_0; /*!< Offset: 0x084 (R/W) I/O configuration for pin PIO3_0/nDTR */

__IO uint32_t PIO3_1; /*!< Offset: 0x088 (R/W) I/O configuration for pin PIO3_1/nDSR */

__IO uint32_t PIO2_3; /*!< Offset: 0x08C (R/W) I/O configuration for pin PIO2_3/RI/MOSI1 */

__IO uint32_t SWDIO_PIO1_3; /*!< Offset: 0x090 (R/W) I/O configuration for pin SWDIO/PIO1_3/AD4/CT32B1_MAT2 */

__IO uint32_t PIO1_4; /*!< Offset: 0x094 (R/W) I/O configuration for pin PIO1_4/AD5/CT32B1_MAT3 */

__IO uint32_t PIO1_11; /*!< Offset: 0x098 (R/W) I/O configuration for pin PIO1_11/AD7 */

__IO uint32_t PIO3_2; /*!< Offset: 0x09C (R/W) I/O configuration for pin PIO3_2/nDCD */

__IO uint32_t PIO1_5; /*!< Offset: 0x0A0 (R/W) I/O configuration for pin PIO1_5/nRTS/CT32B0_CAP0 */

__IO uint32_t PIO1_6; /*!< Offset: 0x0A4 (R/W) I/O configuration for pin PIO1_6/RXD/CT32B0_MAT0 */

__IO uint32_t PIO1_7; /*!< Offset: 0x0A8 (R/W) I/O configuration for pin PIO1_7/TXD/CT32B0_MAT1 */

__IO uint32_t PIO3_3; /*!< Offset: 0x0AC (R/W) I/O configuration for pin PIO3_3/nRI */

__IO uint32_t SCK_LOC; /*!< Offset: 0x0B0 (R/W) SCK pin location select Register */

__IO uint32_t DSR_LOC; /*!< Offset: 0x0B4 (R/W) DSR pin location select Register */

__IO uint32_t DCD_LOC; /*!< Offset: 0x0B8 (R/W) DCD pin location select Register */

__IO uint32_t RI_LOC; /*!< Offset: 0x0BC (R/W) RI pin location Register */

} LPC_IOCON_TypeDef;

上述结构体界说在头文件LPC11xx.h中。

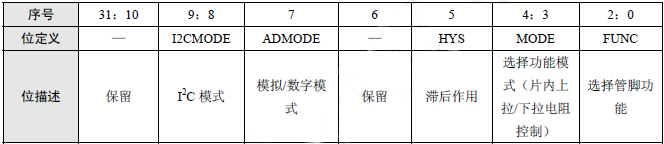

每一个IOCON存放器都是32位结构,但它最多只用了其间的低11位,由于依据各引脚功用不同,设置所占用的位数是不相同的。为了便利评论,下表给出一个IOCON存放器的一般位域界说描绘,在实践用到引脚的不同设置时,请自行查询数据手册。

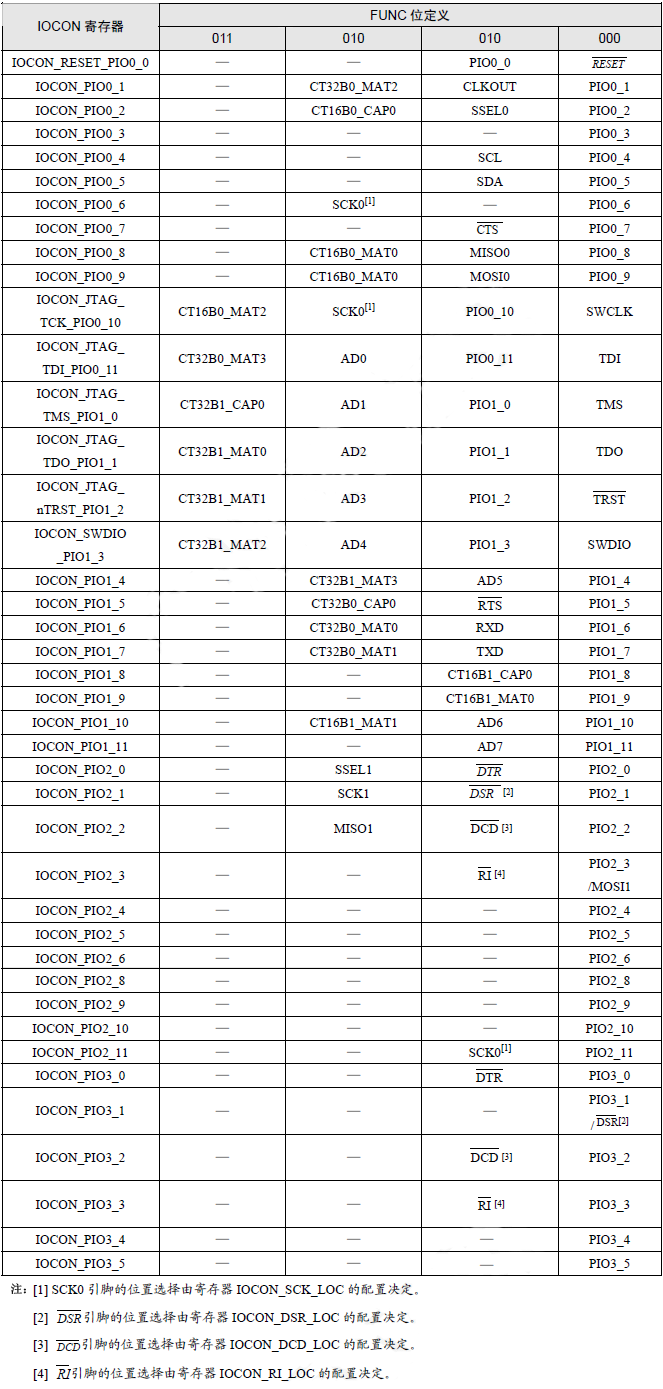

下表是上表中引脚复用功用(FUNC)的挑选状况。

从上表中能够看出,由于LPC1114各引脚的复用功用数量不相同,所以关于每一个引脚FUNC位的设置要依据详细引脚来定,不能想当然混为一谈。比方,不能以为FUNC为全0时引脚便是运用IO功用,由于端口1的第0~3引脚和端口0的第0、第10~11引脚在FUNC为全0时就不是IO引脚。

下面临引脚装备做几点阐明:

1.若引脚被装备为GPIO,则可用DIR存放器来设置其方向(即输入/输出);若装备为非GPIO功用时,DIR设置无效。

2.若引脚被装备为GPIO,则默许为带上拉的方法,但无论是上拉仍是下拉,都是弱拉式的(片内40k电阻),若要强拉有必要外接电阻。

3.滞后效果即为输入缓冲,它只能在外部引脚电压为2.5~3.6V时才干运用,当电压低于2.5V时有必要禁能。

4.挑选A/D转化方法时,内部数字接纳部分被断开,以确保输入电压的精度,若只接纳凹凸电平,有必要设为数字方法,不然读不到电平。

5.只需部分引脚有A/D方法和I2C方法(见FUNC表),其它引脚装备为此方法时无效,若引脚装备为A/D方法后,滞后和上/下拉装备无效。

6.一切引脚装备的IOCON在复位时,值为0xD0,表明默许时引脚为复用功用第0组,上拉电阻方法,禁能滞后特性,数字方法。

7.在运用程序装备时,要注意IOCON的第6位(保存位)有必要写1,因其复位值为1。

8.其它四个多于的特别装备存放器(SCK_LOC、DSR_LOC、DCD_LOC、RI_LOC)首要用来定位某引动功用的引脚,详细用法请参考手册。

9.在装备IOCON之前有必要把IOCON的时钟(坐落AHBCLKCTRL存放器中的第16位)翻开,不然装备不了,装备完成后再把时钟封闭,以节省电能。

最终来看几个比如:

一、要求把端口0的第0脚装备为GPIO口,方向为输出,带上拉,输出值为0。

履行:LPC_SYSCON->SYSAHBCLKCTRL |= (1<<16);

LPC_IOCON->RESET_PIO0_0 = 0xD1;

LPC_SYSCON->SYSAHBCLKCTRL &= ~(1<<16);

LPC_GPIO0->DIR |= 0x001;

LPC_GPIO0->MASKED_ACCESS[1] = 0x000;

二、要求把端口1的第1脚装备为A/D输进口。

履行:LPC_SYSCON->SYSAHBCLKCTRL |= (1<<16);

LPC_IOCON->R_PIO1_1= 0x42;

LPC_SYSCON->SYSAHBCLKCTRL &= ~(1<<16);

三、要求把端口1的第3脚装备为CT32B1_MAT2方法。

履行:LPC_SYSCON->SYSAHBCLKCTRL |= (1<<16);

LPC_IOCON->SWDIO_PIO1_3= 0xD3;

LPC_SYSCON->SYSAHBCLKCTRL &= ~(1<<16);