1 概述

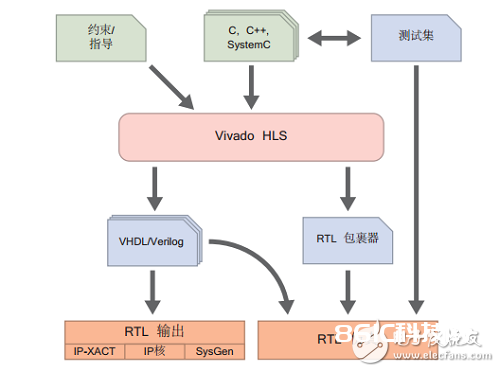

Vivado HLS 是 Xilinx 供给的一个东西,是 Vivado Design Suite 的一部分,能把根据 C 的规划 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上完结用的 RTL 规划文件 (VHDL/Verilog 或 SystemC)。

1.1 vivado hls 的规划流程

图1 vivado hls的作业流程

Vivado HLS 流程有三种不同的 RTL 格局能够供给。如下:

IP-XACT — IP-XACT 是由 SPIRIT 财团提出的一种公共的规划 IP 的文档标准。这是一种被广泛运用的描绘 IP 的 XML 模版,它与详细的东西无关并且机器可读 。

IP Core — 挑选这个选项的时分,你的 IP 会被输出成能被输入到 XPS 去的格局。

SysGen — 这个选项让你能把成果 RTL 文件输出成一个能够用在 System Generator 的规划中的包。

1.2 TCL脚本简介

TCL(最早称为“东西指令言语”"Tool Command Language", 可是现在现已不是这个意义,不过咱们依然称号它为TCL)是一种脚本言语。 由John Ousterhout创立。 TCL很好学,功用很强壮。TCL经常被用于 快速原型开发,脚本编程,GUI和测验等方面。TCL念作“踢叩” "TIckle".

2 labs2 运用tcl脚本进行c,c++到RTL级的仿真归纳

利用上一节labs1的工程文件fir.c fir.h fir_test.c运用tcl脚本运转来完结整个工程的仿真,归纳,以及完结生成ip等动作。愈加便利和方便的完结咱们的规划。

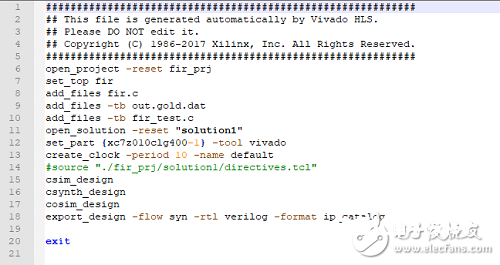

Run_hls.tcl脚本源码如下:

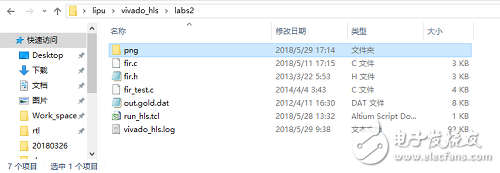

Labs2工程目录如下图。包含fir.c、fir.h、fir_test.c、out.gold.dat以及run_hls.tcl等文件。

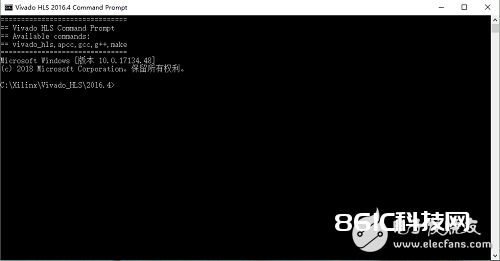

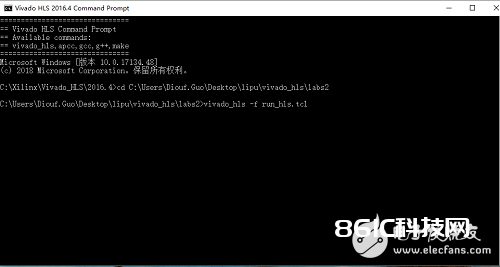

第一步 翻开 vivado hls command prompt 如下图

第二步 cd 到labs2目录下图

第三步 输入vivado_hls -f run_hls.tcl 回车

整个脚本运转的进程如下视频:

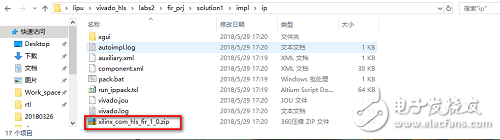

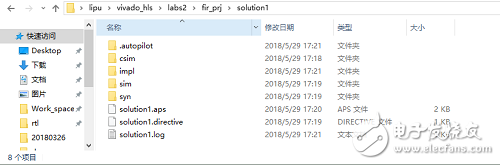

运转完结后labs2目录如下图

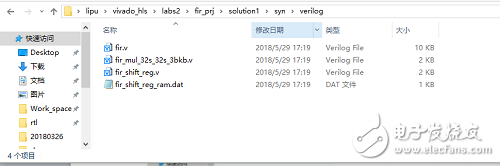

和labs1相同生成了咱们所需求的csim,sim,syn,impl和fir滤波器的verilog文件。完结了c转化成verilog的进程。下节将演示怎么增加fir滤波器ip和vivado生成modelsim仿真库以及联合modelsim仿真fir滤波器。