本文首要讲了一下关于3V-5V电平转化电路图,下面一起来学习一下:

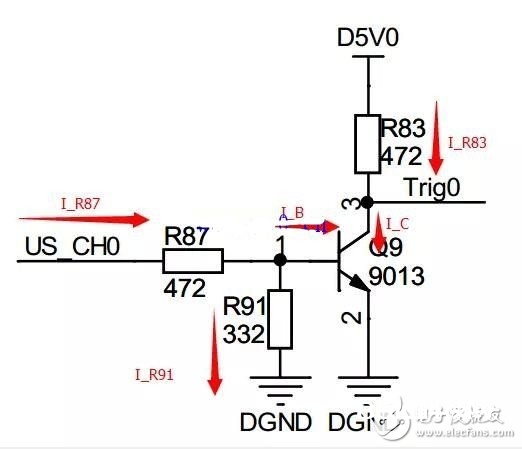

如图左端接3.3VCMOS电平,可所以STM32、FPGA等的IO口,右端输出为5V电平,完成3.3V到5V电平的转化。

现在来剖析下各个电阻的效果(捉住的中心思路是三极管的Vbe导通时为稳定值0.7V左右):

假定没有R87,则当US_CH0的高电平直接加在三极管的BE上,》0.7V的电压要到哪里去呢?

假定没有R91,当US_CH0电平状况不确定时,默许是要Trig输出高电平仍是低电平呢?因而R91起到固定电平的效果。一起,假如无R91,则 只需输入》0.7V就导通三极管,门槛电压太低了,R91有提高门槛电压的效果(可拜见第二末节关于蜂鸣器的剖析)。

可是,加了R91又要留意了:R91假如太小,基极电压近似

只要Vb》0.7V时才能使US_CH0为高电平时导通,上图的Vb=1.36V

假定没有R83,当输入US_CH0为高电平(三极管导通时),D5V0(5V高电平)直接加在三极管的CE级,而三极管的CE,三极管很简单就损坏了。

再进一步剖析其作业机理:

当输入为高电平,三极管导通,输出胁迫在三极管的Vce,对电路测验成果仅0.1V

当输入为低电平,三极管不导通,输出相当于对下一级电路的输入运用10K电阻进行上拉,实践测验成果为5.0V(空载)

请留意:

关于大电流的负载,上面电路的特性将体现的不那么好,因而这儿一向着重——该电路仅适用于10几mA到几十mA的负载的电平转化。