当时车载电子体系的归纳化程度跟着计算机和电子技能的开展不断提高,对视频处理的归纳化要求也不断提高,怎么对多种外视频源进行处理与对输出通路进行操控,是车载视频处理中面对的越来越杰出的问题。本文评论的要点是以DSP+FPGA为中心的视频处理模块的规划与完结,能够完结多路视频的切换挑选输出操控和视频缩放显现的功用,一起具有通讯操控等功用。

1 视频处理模块体系结构

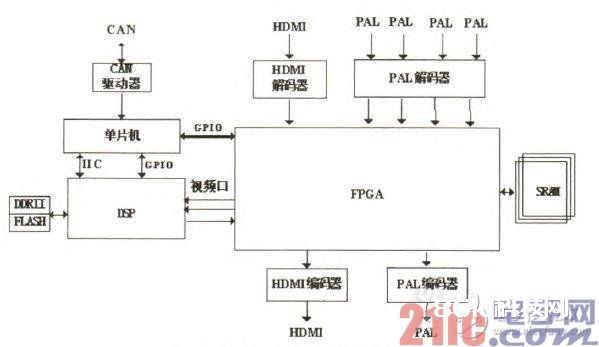

视频处理模块的体系结构如图1所示,首要包含以下功用电路:

(1)DSP电路;

(2)存储器电路,包含DDRII及FLASH;

(3)FPGA功用电路;

(4)1路高清HDMI接纳电路;

(5)l路标清HDMI发送电路;

(6)4路PAL-D接纳电路;

(7)11路PAL-D发送电路;

(8)CAN通讯接口电路,选用单片机内部集成的CAN通讯操控器完结;

(9)电源转化电路;

(10)时钟电路;

(11)复位及监控电路。

图1视频处理模块体系结构示意图

视频处理模块以DSP+FPGA为中心,通过CAN总线对其进行功用操控,支撑四路PAL视频输入及1路高清HDMI视频输入,在FPGA内进行视频缩放处理与切换操控,某些杂乱、特别的视频处理功用由DSP来完结,终究输出2路标清视频,其间1路标清数字HDMI视频,1路标清模仿PAL视频。

2 DSP电路规划

DSP选用TI公司的DM648处理器,DM648是TI公司为视频处理使用开发的一款高性能低功耗处理器,它集成了5个视频端口和图画协处理器,首要具有以下特性:

(1)处理内部主频1.1GHz,处理速度到达8800MIPS,每个时钟周期能够履行8个32位C64Xx+指令;

(2)具有32kb的LIPProgramRAM和32kb的L1DDataRAM:

(3)具有支撑512kbyte的L2UnifiedMappedRAM;

(4)支撑小端形式;

(5)具有5个可装备的视频口;

(6)集成外部EMIFS存储器办理接口,可办理512Mbytes的DDR2SDRAM和128Mbytes的FLASH;

本规划中,DSP通过专用的DDRII接口外接512MB的DDRII存储器,通过EMIF接口外接32MB的FLASH。DSP的专用视频口,装备成 2个输入视频端口和1个视频输出端口,输入视频端口接纳FPGA送来的视频数据,输入视频端口既能够接纳16bit的高清YCrCb数据,也能够接纳契合 BT656规范的8bit标清YCrCb数据;输出视频端口输出契合BT656规范的8bit标清YCrCb数据,DSP将输出的视频数据送给FPGA。

3 FPGA电路规划

FPGA用于接纳、转发及处理各种视频信号,完结视频缩放、视频切换等功用。

FPGA共有如下几种功用接口:

(1)外视频PAL.D数字视频接纳接口,4路,契合BT656格局的YCrCb信号,每路视频接口为8位数据信号,1位时钟线,时钟频率27MHz;

(2)外视频高清视频YCrCb接纳接口:1路,16位数据信号,l位时钟线,时钟频率74.25MHz,4位操控线;

(3)接纳DSP送来的标清数据:1路,契合BT656格局的YCrCb信号,8位数据信号,1位时钟线,时钟频率27MHz;

(4)标清数字视频发送接口:1路,契合BT656格局的YCrCb信号,8位数据信号,1位时钟线,时钟频率27MHz;

(5)PAL.D数字视频发送接口:1路,契合BT656格局的YCrCb信号,8位数据信号,1位时钟线,时钟频率27MHz,2位操控信号;

(6)送给DSP的高清数字视频接口:1路,16位数据信号,l位时钟线,时钟频率74.25MHz,4位操控线;

(7)送给DSP的标清数字视频接口:1路,契合BT656格局的YCrCb信号,8位数据信号,l位时钟线,时钟频率27MHz;

(8)视频缓存接口:3片SRAM存储器。

视频处理模块中,FPGA是其功用操控与处理算法完结的中心器材。跟着FPGA工艺和技能的不断开展,其逻辑容量、存储器资源、DSP乘加器、软硬IP核资源都在不断地扩展和丰厚比,使以FPGA为中心完结杂乱功用的硬件规划成为可能。FPGA芯片选用Xilinx公司的Spartan6系列低功耗FPGA-XC6SLXl00,XC6SLXl0芯片丰厚的逻辑资源与存储器资源答应进行杂乱的视频处理逻辑开发口。

4 FPGA内部视频处理逻辑规划

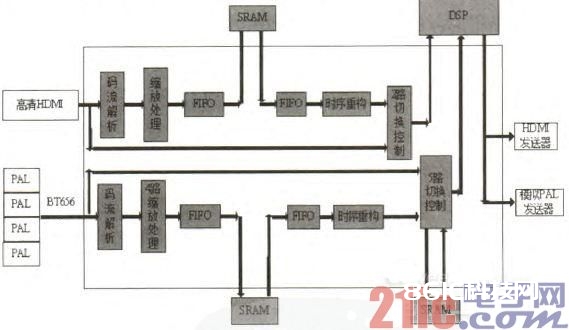

FPGA逻辑结构功用框图如图2所示。

高清HDMI的视频信号时序为契合高清规范的16bit色彩深度的YCrCb信号,经缩放处理模块缩小后送入SRAM缓存,高清视频分辨率经缩小后由 1920×1080i变为640×4801,该视频数据经时序重构模块填充成720×576i,并契合BT656规范。高清原始视频和缩放后的视频经2路切换操控模块之后挑选性地送入DSP的视频端口。

4路PAL视频解码后图画信号时序为契合BT656格局的8bit宽度YCrCb信号,分辨率为720×576i。4路PAL视频通过缩放处理后组成l路视频,分别在屏幕的左上、左下、右上及右下四个方位显现4路PAL视频,每一路 PAL视频的分辨率缩小为360×288。处理之后的PAL视频与原始4路PAL视频通过5路切换处理之后输入1路PAL视频送给DSP。

DSP处理后的视频送给FPGA,在FPGA内部做1分2处理后输出2路标清视频。

图2FPGA逻辑功用框图

5结束语

本文介绍根据DSP+FPGA的视频处理模块的规划与完结,FPGA担任完结视频缩放及视频切换的功用,DSP担任视频的特别处理,供给多路视频恣意切换显现,减少了视频显现通道的推迟,较好地满意了车载视频归纳显现的需求。