1 DDS概述

1.1 DDS基本原理

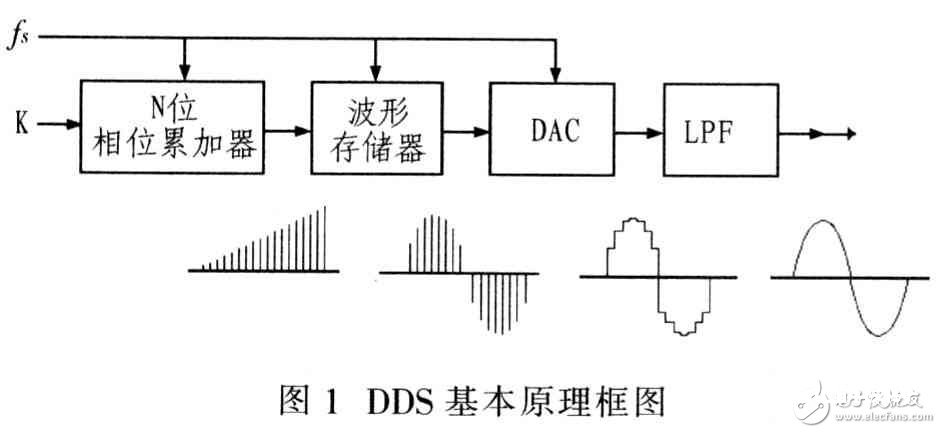

直接数字组成技能(Direet Digital Synthesis,简称DDS)是树立在采样定理基础上,首要对需求发生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后经过查表读取数据,再经D/A转化器转化为模拟量,将保存的波形从头组成出来。DDS基本原理框图如图1所示。

由图l看出,除了滤波器(LPF)之外,DDS体系都是以数字集成电路完结,因而DDS体系易于集成和小型化。DDS体系的参阅时钟源通常是一个具有高稳定性的晶体振荡器,整个体系的各个组成部分供给同步时钟。频率字(FSW)实际上是相位增量值(二进制编码),作为相位累加器的累加值。相位累加器在每一个参阅时钟脉冲输入时,累加一次频率字,其输出相应添加一个步长的相位增量。由于相位累加器的输出衔接在波形存储器(ROM)的地址线上,因而其输出的改动就相当于查表。这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出。ROM的输出送到D/A转化器,经D/A转化器转化成模拟量输出。

1.2 DDS的基本参数及其核算

在体系时钟脉冲的效果下,相位累加器不断累加,即不断查表,把波形数据送到D/A转化器转化成模拟量输出,然后组成波形。滤波器则进一步滑润D/A转化器输出的近似正弦波的锯齿阶梯波,一起衰减不必要的杂散信号。设频率字(FSW)的值为d,体系时钟频率为f,相位累加器的字长为N,则体系的输出频率为:

2 恣意波形发生器的规划方案

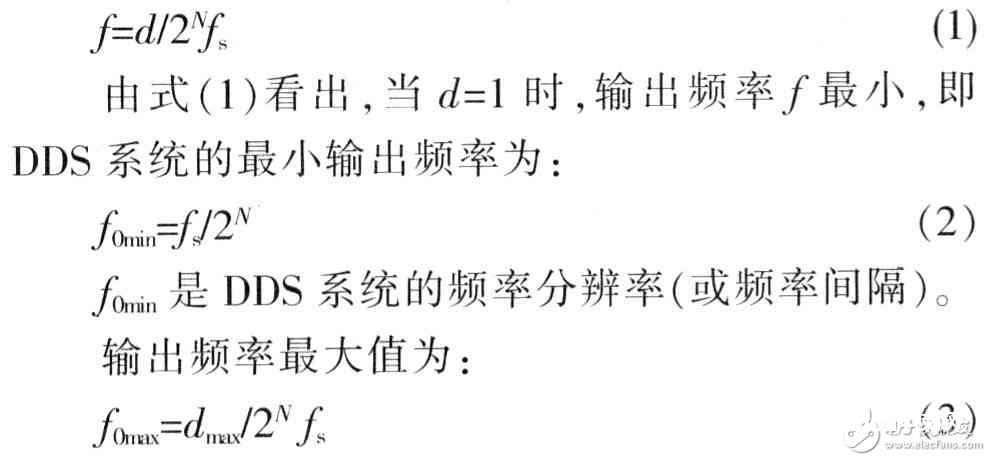

根据DDS技能的恣意波形发生器首要由微处理器操控模块、键盘与显现模块、DDS通道的FPGA完结模块、D/A转化模块以及滤波器模块组成。一起片外扩展了4 KB程序存储器SRAM和6 KB数据存储器ROM,别离用于存储波形抽样数据和3种规范输出波形抽样数据。本体系规划原理如图2所示。

2.1 微处理器操控模块

选用AT89C5l单片机完结数据处理和操控其他电路作业。将键盘接纳的数据经过特定算法转化成二进制码,再将处理后的操控字、波形参数和其他器材的操控信号发送出去。

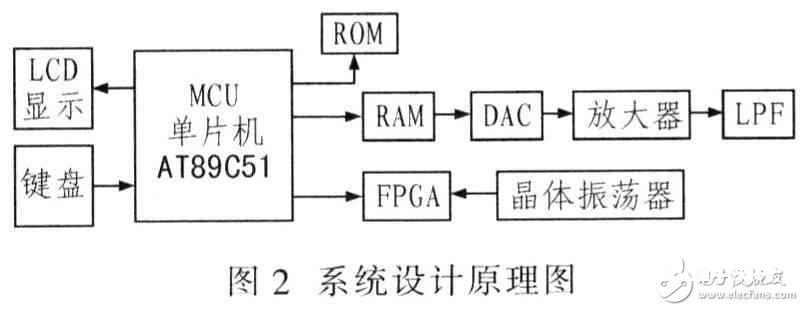

由于AT89C5l单片机首要接口有:微处理器与扩展器材的接口;微处理器与FPGA模块的接口;微处理器与键盘、显现模块的接口;微处理器与输出幅值调理电路的接口。由于单片机的输出引脚有限,需扩展其引脚。本规划选用8255器材扩展单片机的输出引脚,8255的PA用于相位操控字的输出;PB用于频率操控字的输出;PC是位可控输出端,用于DDS作业方法的操控字和波形参数的操控字输出引脚。AT89C5l单片机与FPGA的接口电路如图3所示。

2.2 键盘与显现模块

由于本体系规划的丈量设备需求设置输出波形、频率、电压等参数,并且监控程序需求菜单驱动,因而需求设置键盘。键盘选用外接4×4软键盘,运用软件扫描方法取得按键信息。由于按键需求去颤动,因而选用软件编程方法完结,这样能够节约硬件资源,简化电路规划。

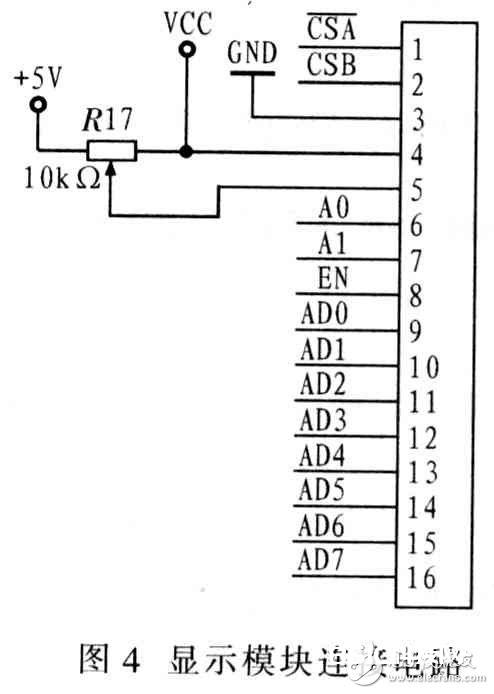

液晶显现可供给人机交互界面和体系运转状况,选用精工的MGLS 19264液晶显现屏。该液晶显现屏内置2块HD61202U液晶显现驱动操控器。其间CSA,CSB作为左、右屏片选信号,接单片机A8、A9引脚。一起单片机用地址Al作为R/W信号操控数据总线的数据流向;地址AO作为D/I信号操控寄存器的挑选;E信号由单片机的读信号RD和写信号WR组成发生,完结核算机对内置HD61202U图形液晶显现模块的电路衔接。电位器用来调理显现屏的对比度,如图4所示。液晶显现左半屏命令字地址为0EOOH;状况字地址为0EIOH;写显现命令字地址为0E0lH;读显现命令字地址为0EllH;右半屏对应地址为0D00H、0D10H、0D0lH、0DllH。

2.3 DDS通道的FPGA完结模块

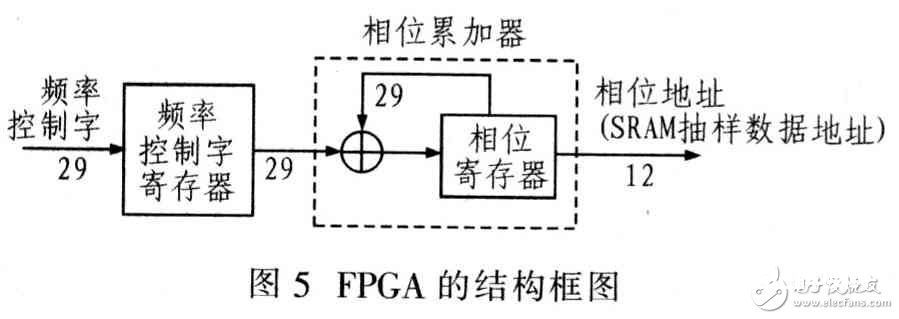

该模块规划是DDS信号组成的要害部分,首要由相位累加器、地址总线操控器、数据总线操控器与SRAM组成。其间,除了SRAM外,其他3个模块都由FPGA完结。

相位累加器是整个DDS体系的要害,直接影响整个体系的功用。图5给出的FPGA结构框图中相位累加器实质上是一个带反应的29位加法器,它把输出数据作为反应数据和由微处理器送来的频率操控字接连相加,然后发生有规则的29位相位地址码。规划中选用流水线技能完结29位加法。当输入所需频率时,转化成频率操控字来驱动FPGA作业,然后发生所需波形频率。整个模块规划进程运用FPGA的开发软件完结并进行仿真。

2.4 D/A转化模块

D/A转化器是DDS体系的中心器材,其速度和特性直接影响整个体系的功能。从树立时刻、尖峰脉冲能量、位数和积分线性等四个方面挑选D/A转化器。由于DDS体系的作业频率一般都很高,因而首要应选用高速D/A转化器。其次是考虑信噪比问题,增大D/A转化器的位数,可减小电压幅值量化差错,增大信噪比,因而,选用了12位的D/A转化器。

2.5 滤波器模块

滤波器分为两组:一组是椭圆函数滤波器,用于正弦波的滤波;另一组是线性滤波器,用于其他规范波形的滤波。

3 结语

本体系规划的DDS电路选用FPGA完结,单片机操控整个体系,发生恣意波形。因而,根据DDS技能的波形发生器结构简略,成本低,并且提高了信号源输出信号的分辨率。运用FPGA规划的DDS电路要比选用专用DDS器材更灵敏,性价比更高。但在规划时应留意线路板的布线,以削减外界搅扰,下降输出信号的杂散性。