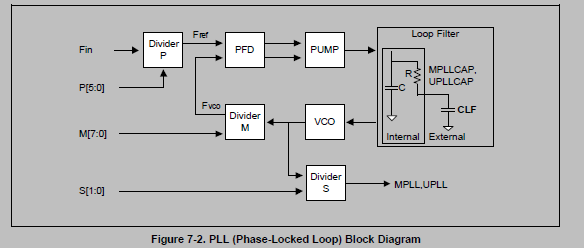

S3C2440的默许作业主频有两种12MHz和16.9344MHz,也便是咱们的晶振的频率,但一般12MHz的晶振用的比较多,Fin便是指咱们接的晶振频率。咱们都知道s3c2440上电正常作业后频率是远远大于12MHz和16.9344MHz的,咱们的s3c2440的cpu正常作业时的频率便是405MHz,因而这就需求一个电路来提高频率,在s3c2440的datasheet中找到了这个电路,下面这个便是PLL电路:

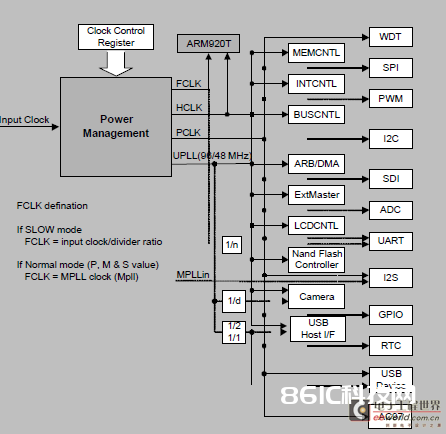

图中给出了各种接口设备运用的时钟信号

首要讲下FCLK,首要看下datasheet中的介绍:

The Clock control logic in S3C2440A can generate the required clock signals including FCLK for CPU, HCLK for the

AHB bus peripherals, and PCLK for the APB bus peripherals.

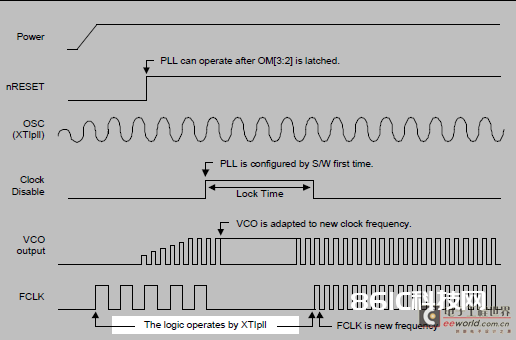

1、上电几毫秒后(power由低变高),晶振输出安稳,此刻FCLK=晶振频率,nRESET信号康复高电平后,CPU开端履行指令。

2、咱们能够在程序最初发动MPLL,在设置MPLL的几个寄存器后,需求等候一段时刻(Lock Time),MPLL的输出才安稳。在这段时刻(Lock Time)内,FCLK停振,CPU停止作业。Lock Time的长短由寄存器LOCKTIME设定。