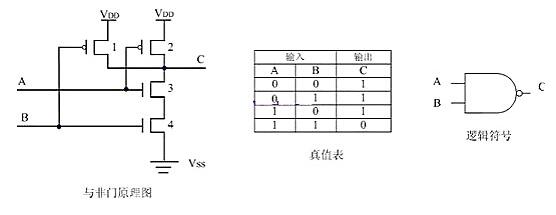

与非门

与非门(英语:NANDgate)是数字逻辑中完成逻辑与非的逻辑门,功用见左边真值表。若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1)。与非门是一种通用的逻辑门,由于任何布尔函数都能用与非门完成。

与非门作业原理

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD共同,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持共同,输出高电平。

③、A输入低电平,B输入高电平时,状况与②相似,亦输出高电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地共同,输出低电平。

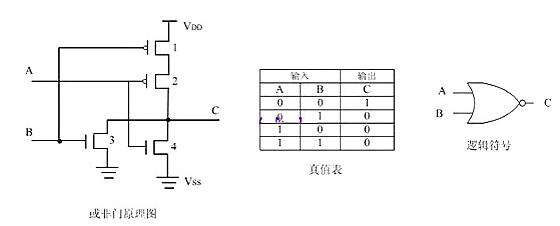

或非门

或非门(英语:NORgate)是数字逻辑中完成逻辑或非的逻辑门,功用见右侧真值表。若输入均为低电平(0),则输出为高电平(1);若输入中至少有一个为高电平(1),则输出为低电平(0)。或非是逻辑或加逻辑非得到的成果。或非是一种具有函数齐备性的运算,因而其他任何逻辑函数都能用或非门完成

或非门作业原理

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD共同,输出高电平。

②、A输入高电平,B输入低电平时,1、4管导通,2、3管截止,C端输出低电平。

③、A输入低电平,B输入高电平时,状况与②相似,亦输出低电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地共同,输出低电平。