规划了一组根据CPLD的PLC背板总线协议接口芯片,协议芯片能够区别PLC的背板总线的周期性数据和非周期性数据。具体介绍了经过Verilog HDL言语规划状况机、协议帧控制器、FIFO控制器的进程,25MHz下背板总线作业安稳的实验成果验证了协议芯片规划的可行性。

可编程逻辑控制器(PLC)主机是经过背板总线支撑扩展模块的衔接, 背板总线是PLC 主机同I/O扩展模块之间的高速数据通路,支撑主机和扩展模块之间的I/O 数据改写。背板总线的技能水平决议了PLC 产品的I/O 扩展才能,是PLC 规划制作的核心技能。现在,PLC 大多选用串行通讯技能完成背板总线,串行总线引线少、硬件成本低,跟并行总线比较不容易受搅扰,串行总线能够进步在恶劣的工厂和工业环境下自动化设备的可靠性。用于串行通讯技能的可选类型包含I2C、UART、SPI、USB 和以太网等,一般来说,许多作为PLC 主芯片的单片机本身都集成了这些外设部件。可是单片机内部集成的I2C、UART、SPI 外设通讯速率太慢,底子不能满意底板总线的通讯速度要求。USB 和以太网的通讯速度尽管很快但因为它们都是通用的接口,在通讯协议处理时需求单片机的干涉, 单片机处理数据速度较慢,因而全体通讯速度依然很慢。一台大型的PLC 收集上千点I/O 数据的时刻一般不到1ms,要满意如此高速的通讯要求有必要规划专门的背板总线。

1 背板总线作业原理

如图1 所示,根据背板总线的数据通讯流程如下:

(1)PLC 主机的指令经过主机协议芯片发送到背板总线;(2)从机协议芯片把接纳到的指令给扩展模块的单片机, 某一个扩展模块的单片机做出应对,经过从机协议芯片把应对数据送往背板总线;(3)主机协议芯片收到应对数据,并送往PLC主机的单片机。

图1 背板总线通讯框图

PLC 主机发往背板总线的数据能够分红两类:一类是I/O 改写数据,具有周期性,数据交换十分频频;另一类是确诊性数据,具有非周期性,呈现时机较少。

2 协议芯片规划

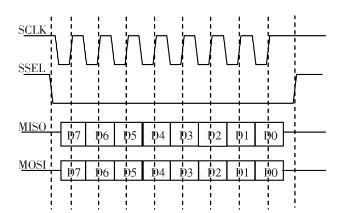

本规划界说背板总线选用相似SPI 串行通讯的标准,用于通讯的引线共4 根,包含时钟信号SCLK、片选信号SSEL、写数据引线MISO 和读数据引线MOSI;支撑主机和从机一起收发数据,数据位格局如图2 所示,数据帧在SSEL 信号为低电平时传输。

图2 背板总线数据标准

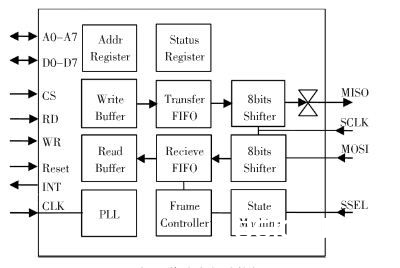

主机和从机协议芯片的内部结构框图相同,如图3 所示。

协议芯片内部有状况机控制器、帧控制器、移位寄存器、接纳/发送FIFO 和读写缓存。单片机发送的周期性、非周期性数据帧,首要都写到写缓存,在发送FIFO 中进行排队发送,在SPI 时钟SCLK 的驱动下数据帧被转换为串行数据发送到背板总线;在SPI 时钟的效果下, 接纳来自背板总线上的串行数据;在状况机和帧控制器的协调下,接纳FIFO 中的有用数据帧被提取并放进读缓存区,等候单片机来读取,假如是非周期性数据则发中止信号告诉单片机来取数据。读缓存中的周期性数据是能够掩盖的,新接纳到的周期性数据直接掩盖旧的周期性数据,而非周期性数据是独自寄存的,不能掩盖,由单片机读取并铲除。

图3 协议芯片内部结构框图

协议芯片使得外接的单片机能够在闲暇的情况下拜访读缓存和写缓存,单片机不用频频地经过中止技能处理周期性数据,也使得PLC 主机能够无等候地拜访从机的周期性数据。

3 根据CPLD 的协议芯片完成

3.1 CPLD 芯片选型。

本规划选用lattice 公司的MachXO 系列芯片,该系列CPLD 集成了部分FPGA 的功用, 除了内置丰厚的LUT 资源以外,还有很多分布式的SRAM 位和嵌入式的专用于FIFO 规划的SRAM 块, 并有模仿锁相环(PLL)支撑时钟信号的倍频、分频等,I/O引脚可装备成1.2/1.5/1.8/3.3V 电平兼容。

3.2 根据Verilog HDL 言语的硬件程序规划

本规划选用Verilog HDL 言语进行协议芯片的程序规划,Verilog HDL 言语是一种硬件描绘言语,规划数字芯片时能够依照层次描绘,并能够进行时序建模。本规划选用混合规划方式,首要规划的模块有状况机、协议帧检测、FIFO 控制器规划等。

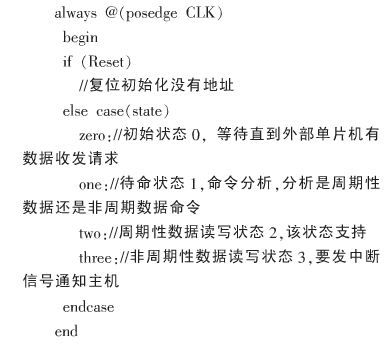

1)状况机规划。

协议芯片的顶层模块是状况控制器部分,协议芯片共有四个状况, 别离处理根据Verilog HDL 程序言语的状况机描绘伪代码如下:

2)协议帧检测。

本协议芯片的帧校验和选用简略的加和方式进行,在接纳一方,假如数据帧中有用数据的加和同后续的校验和字节相同,则协议是正确的,不然丢掉该帧。协议帧校验和核算的代码如下:

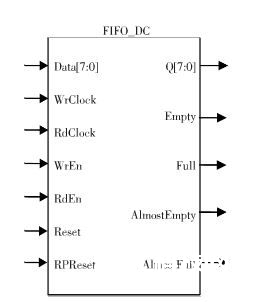

3)FIFO 规划。

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 块的资源,Lattice 公司的ispLEVER 7.0 软件供给了可装备的IP 软核,该软核能够选用根据嵌入式SRAM 块完成, 也能够运用查找表完成,FIFO 的IP 核框图如图4 所示,FIFO 的可装备参数包含FIFO字节深度、EmptyFull、Almostempty 和AlmostFull触发字节深度、数据宽度、巨细端方式等。

图4 可装备FIFO 控制器IP 软核框图

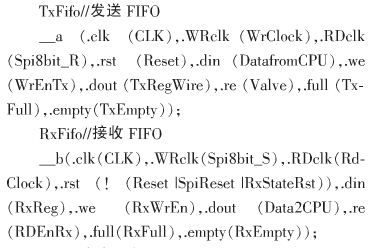

用Verilog HDL 言语完成的发送和接纳FIFO控制器的实例代码如下:

3.3 协议芯片归纳

Verilog HDL 程序经过Lattice 公司的CPLD 开发软件ispLEVER 7.0 进行编译、归纳,屡次测验后终究挑选了Lattice 公司MachXO 系列CPLD 中的MachXO2280 芯片, 归纳后的主机协议芯片占用CPLD 资源的60%左右, 从机协议芯片占用CPLD资源的45%左右,FIFO 控制器充分利用了MachXO2280芯片内部的嵌入式RAM 块, 一起利用了锁相环完成高频率的时钟作业。最终经过LSC ispVM(R)System 烧写软件经JTAG 口下载到CPLD 芯片中进行协议芯片功用验证测验。

4 结语

本文规划的背板总线协议芯片在背板串行总线时钟频率为25MHz、信号电平为LVTTL,底板引线长度为40cm,1 台主机衔接3 台扩展模块的情况下作业安稳并经过了群脉冲实验,验证了这一组协议芯片的规划是成功的。因为该组协议芯片是针对PLC 的周期性和非周期性数据传送专门规划的,硬件完成的协议帧控制器支撑高速率通讯、支撑数据帧查验功用,避免了数据传送的过错,大大降低了外围单片机的软件开支,增强了可靠性,是一组十分合适用于PLC 背板总线或许需求多模块协同作业的背板总线体系协议芯片。