AD9850概要

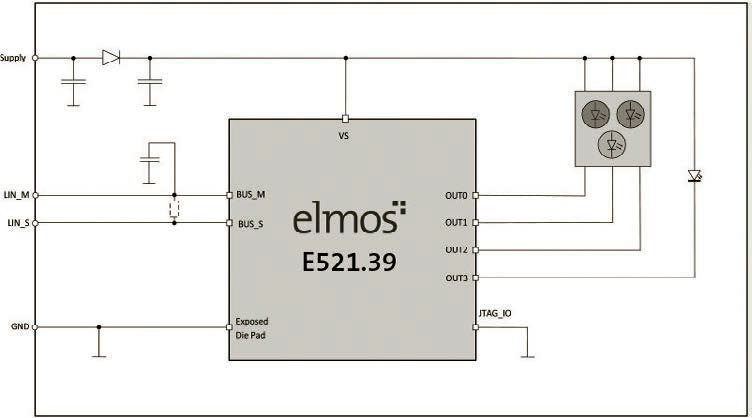

AD9850是AD公司出产的最高时钟为125MHz、选用先进的CMOS技能的直接频率组成器,主要由可编程DDS体系、高性能数模变换器(DAC)和高速比较器3部分构成,能完成全数字编程操控的频率组成。

AD9850内部结构

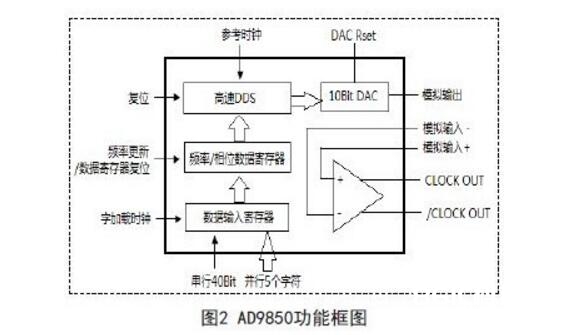

AD9850的芯片功用框图如图2所示。

AD9850芯片内包含高速DDS.10位DAC.频率/相位数据寄存器。数据输入寄存器。比较器等,在125MHz参阅时钟下,AD9850通过高速的DDS中心芯片能发生一个32位频率调整操控字可使AD9850的输出频率达0.0291Hz;并能供给了5bits的相位操控位,它能使输出相位以180°.90°.45°.22.5°.11.25°或是它们恣意组合的增量改动.AD9850的电路结构答应发生频率值是参阅时钟的一半的输出,而且输出的频率能用数控方法以每秒发生23000000个新频率的速度改变.AD9850芯片内的比较器构成能接纳经外部低通滤波后的DAC转化输出,能够发生一个低颤动的方波输出的设备,因而AD9850用作时钟发生器非常便利。频率/相位数据寄存器。数据输入寄存器在外部的频率更新时钟和字加载时钟的操控下进行频率操控字的输入和更新,使芯片输出所要求的频率和相位.

AD9850的作业原理

AD9850内含可编程DDS体系和高速比较器,可完成全数字编程操控的频率组成。

可编程DDS体系由相位累加器和正弦查表组成,其相位累加器由一个加法器和一个N位的相位寄存器组成,N一般为24~32;实质上是一个可变模的计数器,即DDS相位增量的个数在计数器收到每一个时钟脉冲时被存储起来,当计数器溢出时,它就回到初态并运用相位累加器输出到相邻值。频率操控字能设置计数器的模,它决议了相位增量的巨细。相位增量在每个时钟到来时便在相位累加器中相加,相位增量越大,则累加器溢出的速度越快,发生的输出频率越高。

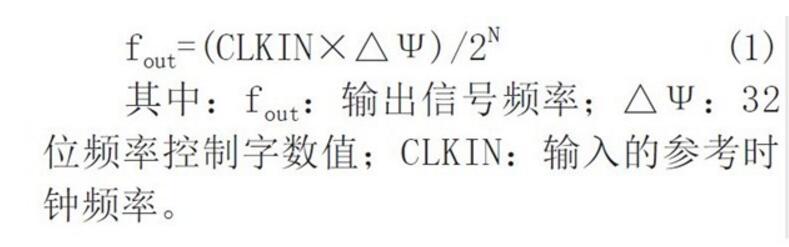

AD9850选用32位的相位累加器,AD9850运用改善的,独有的算法,把14bits已切断的相位累加器的输出转变成恰当的余弦值,经片内高速的10bitDAC转化器,可得到模仿正弦波。这个共同的算法运用一个简化了的ROM表和DSP技能等功用,有助于缩小AD9850的体积和功耗。输入。输出。参阅时钟和频率操控字的联系如下: