本文评论电子体系级(ESL)规划和验证办法学在体系级芯片(SoC)规划中的运用。ESL规划是可以让SoC规划工程师以严密耦合办法开发、优化和验证杂乱体系架构和嵌入式软件的一套办法学,它还供给下流寄存器传输级(RTL)完结的验证根底。已有许多世界抢先的体系和半导体公司选用ESL规划。他们运用ESL开发具有丰厚软件的多处理器器材,这些器材为立异终端产品取得成功供给必需的先进功用性和高功用。

为什么我国的电子工业将会对ESL感兴趣?由于我国抢先的电子公司正在阅历一场对他们竞争力十分要害的转型。经过选用技能立异战略,我国将成为朴实的知识产权(IP)供给者,而不是朴实的IP顾客。那些具有知识产权的公司将持有通向IP库的钥匙。

为成功地履行立异战略,我国公司有必要选用立异抢先公司所运用的先进规划办法学。ESL规划正是这样一种办法学。它现已被许多世界体系和半导体公司选用。在我国,大唐已率先在我国3G手机技能-TD-SCDMA开发中选用ESL规划,清华大学及其一些工业合作单位也选用ESL办法学开发先进的地上数字多媒体播送运用。

嵌入式软件驱动SoC规划

图1总结了市场调研公司世界商业战略(International Business Strategies)对SoC规划工程师所做的查询数据。它标明,两种首要的SoC规划应战–与规划嵌入式软件和硬件架构的相关作业量跟着工艺的缩小而急剧添加,而硬件完结(RTL规划、归纳、物理规划等)作业量的添加则要少得多。请注意,该查询说到的嵌入式软件由半导体制作商供给,这些软件不包含由体系生产商开发的使终端产品差异化的软件。

图1:跟着工艺节点的缩小,首要规划作业从硬件完结转向规划嵌入式软件和硬件架构。

首要规划作业从硬件完结搬运到嵌入式软件和硬件架构这种显着改变标明,芯片已实在成为一个嵌入式体系。

嵌入式软件开发作业量的添加,首要是由于可以完结消费产品之间兼容性和互操作性的无线及多媒体规范(或许其中之一)越来越多。比方JPEG、MPEG、3G、GSM/EDGE、IEEE 802.11/a/b/g WLAN、蓝牙和UWB等规范,都是现代电子工业取得商业成功所必需的。

架构开发作业量的添加首要是由于SoC需求集成和优化越来越杂乱的处理、存储资源以及通讯协议,这些对以必备的功用履行嵌入式软件很有必要。实际上,先进SoC现已选用3个或更多微处理器以及3个或更多数字信号处理器(DSP)。甚至连干流规划也已包含一个微处理器和两个DSP,而包含两个微处理器和两个DSP的状况也很常见。

换句话说,嵌入式软件现正驱动着SoC规划,并且嵌入式软件对开发我国自己的通讯和媒体互操作性规范也十分要害。

为什么选用ESL规划

业界抢先公司选用ESL规划是由于它使规划工程师可以及早进行软件开发,完结快速规划和派生规划、快速硬件验证以及快速硬件/软件(HW/SW)验证。它还供给可以用来验证下流RTL完结契合体系规范的功用测验渠道。此外,ESL规划东西可归纳针对运用优化的定制处理器,以及快速开发和完结先进算法。

及早进行软件开发:关于一个大型软件开发使命,尽或许早地开端软件开发很有必要,即便原有软件的复用程度很高。

选用依据SystemC言语的ESL规划办法学,SoC架构工程师可生成一个用来仿真SoC行为,假如需求,还可仿真SoC周期准确时序的高档模型。这个模型称为业务级模型(TLM),它使软件规划工程师在RTL规划或许硅原型完结前的好几个月就可着手进行软件开发作业。

1.快速规划和派生规划

不断改变的消费市场要求不断推出“新的和改善的”产品。一些改善可以经过从头对SoC进行编程来取得,但更多的软件或许需求更多的硬件资源,因而规划工程师有必要选用可完结快速硬件规划和派生规划的办法。

RTL渠道曾被规划用来削减派生规划问题,它经过为未来规划供给一个经过预验证的架构来完结这一点。可是,为满意新的市场需求而优化RTL架构以及集成RTL IP所带来的困难,会显着减缓规划进程。一个未经优化的架构或许对功用和功耗发生负面影响。终究,规划团队或许被逼抛弃功用性以到达功用和功耗方针。

TLM运用于函数调用和数据包传输层。这是一个笼统层,“规划目的”在该层被捕获,并且该层给规划工程师供给了一个直接而明晰的体系行为视图。硅IP的SystemC TLM模型很简略集成到SoC架构的TLM中,这使SoC架构师能快速研讨并剖析多个备选硬件架构和硬件/软件切割计划(每个计划具有不同的功用和经济上的折衷)以确认最佳架构。这种办法显着加快了初始规划,但它最大的优点是在快速改变的派生规划中选用开端的SoC TLM作为易于更改的渠道。TI就是选用这种办法开发OMAP系列处理器和调制解调器。

2.快速验证

TLM的笼统等级显着高于RTL的笼统等级,它描绘模块内的电路状况、准确到纳秒的转化以及准确到位的总线行为。因而,意法微电子等抢先公司以为,比较运用RTL,运用周期准确的TLM将使硬件验证和硬件/软件协同验证速度快1,000倍或许更多。这种办法不只可发生用于验证体系行为和RTL完结的功用测验基准(testbench),它还支撑SystemC与RTL的协同仿真,这样SoC TLM可被当作一个“测验台”,当下流RTL完结模块可用时,它们便可在这个测验台上进行验证。

高通公司的经历标明,体系级的HW/SW协同验证要优于C/RTL完结级的HW/SW协同验证。一个维特比解码器规划可在20ms内履行一个信息包,可是在C/RTL级进行仿真却需求6个小时,高通估量有必要仿真1,000个信息包才干到达合理的置信度,因而一共需求6,000小时的仿真时刻,但这是不现实的。而1,000个信息包与一个TLM进行协同验证将只需求6个小时,或许更少。

针对运用优化的处理器的归纳:不断增强的处理才干需求常常经过选用额定规范通用(GP)处理器内核来满意。可是,构建GP内核是用来处理广范围内的运用,它或许无法以必备的功用履行一个给定软件算法,且或许占用过多芯片面积和功率。别的,它一般还需付出许多的额定IP答应费和版权费。

选用指令集(IS)针对运用需求优化过的处理器可处理这个问题。定制IS处理器可在只要肯定必要的硬件资源条件下供给必备的功用。运用ESL东西,这样的处理器可以从结构描绘或许定制IS自身开端主动归纳。ESL东西还主动生成处理器的软件开发东西,例如指令集仿真器、汇编器、链接器、反汇编器、调试器和C编译器。

以英飞凌为例,该公司据称在两个月内就为特定运用的多速率DSP开宣布网表和开发东西。

3.先进算法开发

在消费设备中运用的比方JPEG和MPEG等许多先进算法都是数字信号处理算法,有必要完结这些算法以到达对不同设备来说或许不同的功用和功耗方针。先进算法一般首要规划成浮点算术方式的参阅算法(实际上,像JPEG和MPEG这样的规范算法一般都以这种方式完结),然后再转化成定点算术方式,嵌入式软件和RTL完结就是从定点算术方式衍生出来的。

针对DSP算法的图形化ESL规划以及仿真东西能完结这种流程。关于通讯和多媒体运用,选用可定制DSP算法的预规划库能加快算法开发。别的还存在一些规范算法库,例如3G W-CDMA、GSM/EDGE、IS-95 CDMA、IEEE 802.11/a/b/g 无线局域网(WLAN)、蓝牙和UWB。当HW/SW切割后,选用微架构库可加快RTL完结的开发。大唐运用这样的东西与其他公司合作开发了TD-SCDMA的基带库。

TLM办法论

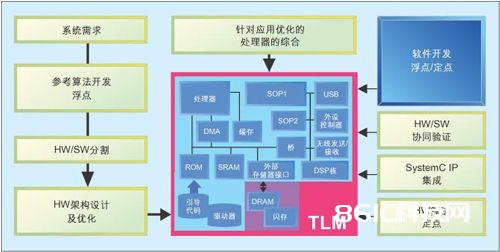

TLM是可完结及早开端软件开发、ESL规划以及验证使命的虚拟集成渠道,图2显现了TLM在SoC规划中所在的中心方位。

图2:ESL规划与验证使命。

SoC TLM本质上是器材资源的一个网络模型,它全无完结的细节。功用模块的行为模型是依据它们的输入鼓励和输出呼应来树立的。模块经过由API衔接至每个模块的一个或许一组总线进行通讯,这些通讯进程则被建模成具有相关数据传输的数据流机制。这样避免了不必要的完结细节,这些细节会含糊规划工程师的体系行为视图并减慢仿真速度。模块行为与通讯分隔,可完结功用模块的快速修正或许替换而无需从头规划总线,反之亦然,它对快速的IP集成以及杂乱的“what if”剖析也十分要害。

有三种常见的TLM运用形式:程序员视图(PV)、架构师视图(AV)以及验证视图(VV)。虽然这些形式代表三种不同的体系视图,可是大多数模型都能以一切三种形式进行装备。

1.程序员视图

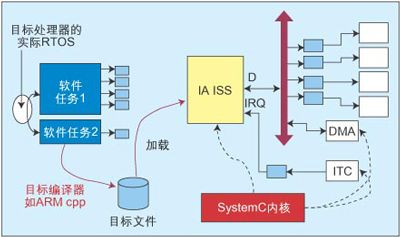

程序员视图TLM是SoC的一种功用正确模型,它答应运用传统软件以及及早开发新软件。一般状况下,PV TLM由处理器、存储器、外设的功用模型以及将业务引导到正确存储器或外设的路由器功用模型组成(见图3)。

图3:程序员视图TLM。

PV使软件开发人员可以拜访必需的体系资源和特点,比方寄存器的可见性、寄存器的准确性和中止处理等,一起它还可直接链接方针处理器和调试环境的指令集仿真器(ISS)。方针RTOS的API以及方针处理器的编译器用来开发软件目标代码,此阶段的运用软件开发只需一个数据流形式(schema)。因而,PV是不守时的,PV仿真可在每秒数百万条指令的速度范围内很好地履行。

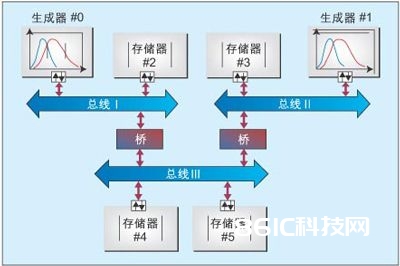

2.架构师视图

架构师视图TLM是具有SoC时序特点的相同模型。该模型使规划团队可以剖析SoC功用以便在规划实 现之前准确找出瓶颈(见图4)。终究的硬件/软件切割决议是在这个视图中完结的。

图4:架构师视图TLM。

时序的捕获不是显式就是隐式。显式时序可以近似地仿照SoC的硬件功用,它用体系事情和事情同步的函数表明,而模块内部时序则或许十分准确。

隐式守时模型运用嵌入到TLM API调用中的时序注释,因而时序注释独立于功用性。这答应对各种功用模块的候选架构和完结进行快速修正和功用描绘,它还可进步仿真速度,使隐式守时模型的仿真速度超越显式守时模型。

指令准确的ISS可经过PV-AV业务器衔接到一个架构视图上,答应在履行软件的一起剖析体系功用。PV-AV业务器还能评价在操作体系(OS)中履行运用的架构。OS以PV形式引导,运用则以AV形式履行。

3.验证视图TLM

验证视图本质上就是AV模型,它在周期准确的时序方面得到增强。这种模型可以完结可准确猜测实在芯片时序的硬件验证和硬件/软件验证,它还使开发团队能创立用于RTL验证的测验基准。用Verilog和/或许VHDL编写的RTL模型一旦完结,便可在VV TLM模型中例示,这样在完好的SoC完结模型完结之前就能进行体系验证以及调试。

VV仿真的履行速度一般比RTL仿真和C/RTL HW/SW协同验证速度快三个数量级。

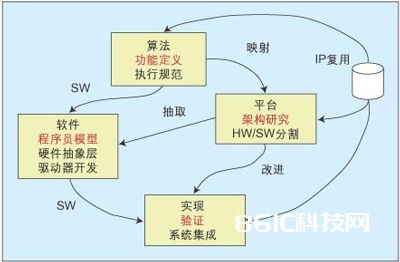

这三个TLM视图组成了悉数ESL规划流程(如图5所示),不同模型可以运用易于规划的处理器和转化器协同履行。

图5:带有三种首要TLM运用形式的HW/SW开发流程。

ESL规划成功事例

抢先的体系和半导体公司现已揭露声称ESL规划的成果超出预期,他们已转向选用在准硅片多处理器体系仿真模型上开发软件的规范操作进程,该模型能以近似实时功用履行。在某些状况下,仿真模型仅在两秒内就可引导一般的RTOS,例如嵌入式Linux。TLM办法具有杰出的准确性,在将硅原型交给制作之前,这种准确性关于优化芯片架构的功用和功耗来说很要害。

例如,某大型日本打印机公司选用ESL规划办法,由于依据RTL的办法已不能应对每一代打印机所需的架构上的严重修正。该公司对其从低端家庭打印机到高端网络打印机的一切产品都选用相同的根本算法。可是,不同打印机类型在数据通讯、处理、存储需求上的严重差异要求那些算法有显着不同的完结,包含不同的存储器架构和通讯总线架构。

优化这些不同架构只能在ESL规划供给的TLM笼统等级上才干得到有用完结。不过,简略地转向ESL规划而短少到RTL完结的链接将导致下流问题。该公司用管脚准确的业务器树立了这种答应SystemC TLM与RTL协同验证的链接。

从RTL转到ESL规划是一条很好的搬运途径。ESL是一种“由中心开端(middle-out)”的规划流程,答应重复运用原有的RTL IP。在那些没有传统束缚的状况下,可以选用“自顶向下”的规划流程。东芝公司就是选用这种流程,运用规划套件开发用户可装备媒体嵌入式处理器(MeP)。这个规划套件的根底是使规划工程师能针对特定运用定制装备的ESL规划环境。规划工程师可研讨不同装备以确认哪种装备最佳,他们不只要验证架构,并且还要验证每个硬件和软件模块是否满意体系要求。

LSI逻辑公司在其ZSP数字信号处理器内核规划中选用了相似办法。LSI对每种不同的内核开发周期和业务准确的SystemC模型,这使规划工程师可以对SoC架构中的内核功用建模。这些模型还使规划工程师能对硬软件交互进行调试。此外,规划师还可剖析处理器的吞吐量和时延以及存储器功用。

本文小结

ESL规划和验证办法使规划工程师可以专心于那些给产品及IP带来差异化和价值的体系规划特点,即功用性和功用。这些特点是由先进算法、杂乱的多处理器和存储器架构、高档通讯协议以及针对运用优化的处理器(它们都由嵌入式软件驱动)决议的。RTL完结的精巧性与高效的完结有关,但其价值则存在体系规划中。IP的立异和具有将成为我国电子工业的下一场革新,而ESL规划和验证办法学将成为这场革新的支撑力气。