摘要:选用FPGA进行的数字电路规划具有更大的灵活性和通用性,已成为现在数字电路规划的干流办法之一。本文给出一种依据FPGA的数字钟规划计划。该计划选用VHDL规划底层模块,选用电路原理图规划顶层体系。整个体系在QuartusⅡ开发渠道上完结规划、编译和仿真,并在FPGA硬件试验箱上进行测验。测验结果表明该规划计划切实可行。

EDA(Electronic Design Automation)又叫电子规划主动化,其根本特征是:以超大规模可编程逻辑器件,如FPGA,为规划载体,以硬件描绘言语,如VHDL,为体系逻辑描绘的首要表达办法,以计算机、大规模可编程逻辑器件的开发软件及试验开发体系为规划东西,完结电子体系的规划。运用EDA进行电子体系规划具有以下特色:1)用软件办法规划硬件;2)用软件办法规划的体系到硬件体系的转化是由有关开发软件主动完结的;3)规划进程中可用有关软件进行各种仿真;4)体系可现场编程,在线晋级;5)整个体系可集成在一个芯片上,体积小、功耗低、可靠性高;6)规划的移植性好、效率高;7)合适分工规划、团队协作。因而,EDA技能是现代电子规划的发展趋势。

1 数字钟的规划计划

本文以FPGA渠道为根底,选用VHDL言语在QuartusⅡ开发环境下规划开发多功用数字钟,具有计时、校时、蜂鸣闹铃的功用,详细功用为:1)可以对秒、分、小时进行正常计时,每日按24小时计时制,能用八个七段数码管进行友爱界面的显现;2)具有复位功用,可以对当时时刻进行清零;3)可以对电子时钟进行时分秒设置,便利在时钟跑错时进行校对;4)可以设定电子闹钟,在指定的时刻驱动蜂鸣器等外设作业,引起运用者留意;5)电子钟具有溢出警报功用,当小时数超越24时,用一个LED小灯进行溢出警报阐明,然后从00—00—00开端重新计时,此功用可以使电子钟很便利的扩展为万年历。

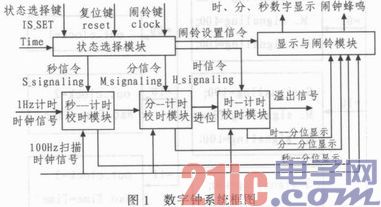

咱们选用自顶向下的层次化规划办法进行规划,其输入为状况挑选信号(运用一个2位二进制表明挑选,00正常运转或显现闹铃信息,01设置秒,10设置分,11设置时)、复位信号、闹铃开关(合作状况挑选信号进行闹铃的设置)、1 Hz的计时时钟信号和1 kHz的扫描时钟信号;输出为时、分、秒数字显现(这儿运用了8个共阴极的七段数码管作为显现输出)、闹钟蜂鸣、溢出信号。体系由状况挑选模块、时、分、秒计时校时模块、显现与闹铃模块组成。数字钟的体系框图图如图1所示。

2 中心模块规划

2.1 状况挑选模块规划

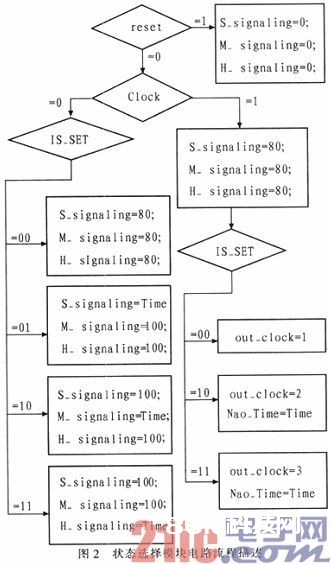

该模块首要功用其实是对输入端的汇总,然后依据设置办法对不同的模块进行使能和参数传递,输出不同的信令signaling操控到各个模块,使每个模块作业在一个有序的状况。状况挑选模块的电路描绘如图2所示,详细阐明如下:当输入一个脉冲到复位键reset时,数字钟发动并对时刻清零。闹铃键clock=0时,模块依据状况挑选键IS_SET输出不同秒、分、时信令到秒、分、时计时校时模块,操控这些模块的运转状况。此刻,当IS_SET=00时为正常计时状况,秒、分、时的输出信令均为80;IS_SET=01时为秒校时状况,输出秒信令S_signaling为时刻输入Time(明显该输出小于60),而输出分信令M_signaling和时信令H_signaling均为100,表明暂停分、时计时;IS_SET=10和11时则别离为分和时的校时状况。闹铃键clock=1时,当IS_SET=10和11时别离设置闹铃的分、时为时刻输入Time并将设置的闹铃时刻输出到“显现与闹铃模块”中保存;当IS_SET=00时,输出out_clock=1,操控显现与闹铃模块显现设置的闹铃时刻。留意,当闹铃键clock=1时,计时正常运转,不管IS_SET怎么设置,秒、分、时的输出信令均为80。

2.2 计时校时模块规划

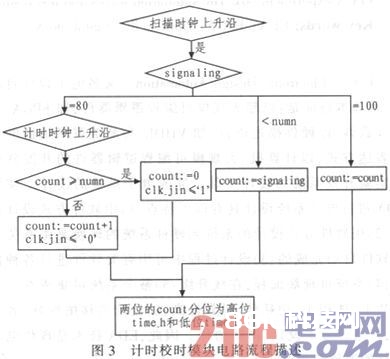

该模块用于时、分、秒的计时校时,依据状况挑选模块传输过来的信令signaling别离进行计时和校时。时、分、秒计时校时模块是相同的,仅仅分秒的进位为60,而小时的进位为24。咱们在实体声明中的运用generic变量界说一个numn,该值设置进制为60或24,经过修正numn值就完结分、秒计时模块到小时计时模块的转化。模块的输入为扫描时钟、计时时钟和信令signaling,输出为输出时刻高位time_h和输出时刻低位time_l,以及进位clk_jin。

计时校时模块的电路描绘如图3所示,详细阐明如下:每逢扫描时钟上升沿时,发动进程,并依据信令signaling履行不同操作,1)当signaling

2.3 显现、闹铃模块规划

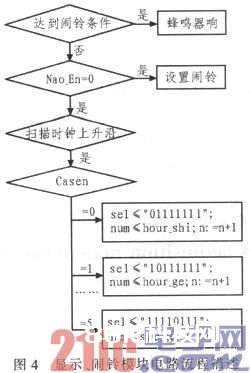

本模块是数字钟体系中的输出模块,用于输出LED数字显现和闹铃,其输入为扫描时钟,从计时校时模块输出的秒低位、秒高位、分低位、分高位、时低位、时高位信号和状况挑选模块输出的闹铃显现Nao_En闹铃时刻Nan_In。假如Nao_En=0则正常显现时刻,当Nao_En=1时,在LED数码管上显现闹钟时刻。当当时时刻与保存的闹铃时刻Nan_In相一起,蜂鸣器鸣响1 min。这儿咱们运用了八个共阴极的七段数码管显现时刻,中选位信号sel=“01111111”时,第一个数码管显现数字,其他七位不显现。咱们经过动态扫描,轮番显现秒低位sec_ge、秒高位sec_shi、分低位min_ge、分高位min_shi、时低位hour_ge、时高位hour_shi共6路信号,当扫描时钟sanc_clk频率高于28 Hz时,因为人眼的视觉残留作用,使得这6路信号看上去是一起显现在6个七段数码管上。显现、闹铃模块电路描绘如图4所示。

3 结束语

在QuartusⅡ软件开发渠道上,选用“自顶向下规划,自底向上完结”的办法完结了数字钟的规划与完结。其根本进程如下:1)完结数字钟的总体规划;2)完结各个底层模块的规划和波形仿真:底层模块选用VHDL言语编写,在编译和仿真成功后,对其进行封装;3)完结数字钟的顶层电路规划:依据数字钟的体系框图(图1)在QuartusⅡ中选用电路原理图办法,调用封装好的底层模块,完结顶层电路图的规划;4)对顶层电路进行编译和仿真,结果表明仿真波形契合规划要求;5)进行引脚分配,再编译后,将下载文件下载到FPGA开发板中进行验证和调试。测验结果表明数码管能正确的显现计时时刻,能经过按键调整时刻,能完结整点报时,完全契合规划要求。