为了满意苛刻功能和快速运转要求,今日的体系,从通讯接口到高品质图画视频和多媒体体系,各种消费类运用广泛选用了数字信号处理技能。数据转化器成为实际国际模仿信号与数字域之间的接口。因而,数据转化器是完好信号处理链上的重要组成部分,而信号处理是每台消费电子设备上不可或缺的一部分。

虽然数据转化器规划杂乱,但IP厂商能够为体系芯片(SoC)规划师供给简直能够满意任何体系要求的数据转化器。此外,为了供给适宜体系芯片集成的数据转化器,Synopsys等闻名的数据转化器IP厂商选用了顶级的电路和架构技能,使它们在苛刻的体系芯片环境中依然坚固经用。这些电路和架构技能(不在本文评论规模之内)能够革除大体系芯片中常见的衬底和电源噪声影响,以及对制程、温度和电压改变体现安稳。

不过,为了完成数据转化器IP功能最大化,体系芯片规划师有必要应对将数据转化器与体系芯片集成的应战,防止损害整个体系功能的缺点。

数据转化器IP集成之所以会被以为错综杂乱,其原因是它要求精心的手动布局布线。可是,通过深化了解影响功能的潜在问题,体系芯片规划师能够具有成功集成到达预期功能的一切技能手段。

本文体系地介绍了12种简化规划技能,这些技能处理了体系集成中的一切常见问题,有助保证在体系芯片中成功集成高功能数据转化器。

数据转化器基础知识

选用最适宜体系芯片终端运用的功能、速度和功耗要求的架构与装备,能够挑选两种类型数据转化器,即模仿-数字转化器(ADC)和数字-模仿转化器(DAC)。

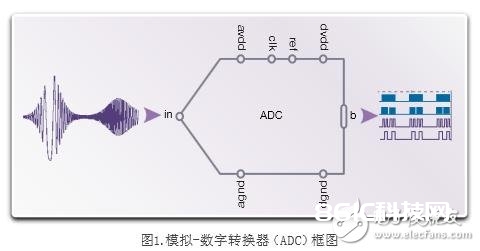

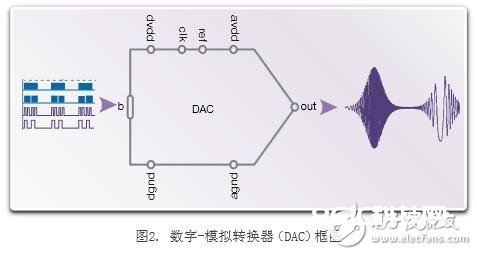

从物理集成的视点来看,两种数据转化器的信号接口相似,只不过ADC是将模仿输入信号转化成数字输出信号(图1),而DAC是将数字输入信号转化成模仿输出信号(图2)。

△模仿输入(in)/输出(out)信号有差分传输和单端传输办法,可有一个、两个或两个以上的通道;

△数字输出/输入(b)信号是模仿输入/输出信号的数字体现形式;

△参阅电压可由内部基准电压源或外部输入;

△转化时钟(clk)可由内部锁相环驱动,或是由芯片外部供给;

△可供给电源和接地电源衔接,包含模仿电源(avdd)、数字电源(dvdd)、模仿接地(agnd)和数字接地(dgnd)

成功的IP集成技能

第三方数字转化器IP在规划进程中考虑到了体系芯片集成和IP运转简略顺利,没有妨碍。可是,随意集成数据转化器或许形成体系功能变差。下面四部分将介绍几种有助保证IP集成成功的简略技能。

1. 首先在体系芯片上做适宜的布局

体系芯片其他逻辑块发生的过大噪声会进入数据转化器继而影响其功能。为保证数据转化器与其他逻辑块很好地阻隔,物理集成进程的第一步是在体系芯片中合理确认数据转化器的方位。

技能1:在活泼逻辑(进犯者)和模仿模块(受害者)之间坚持必定间隔

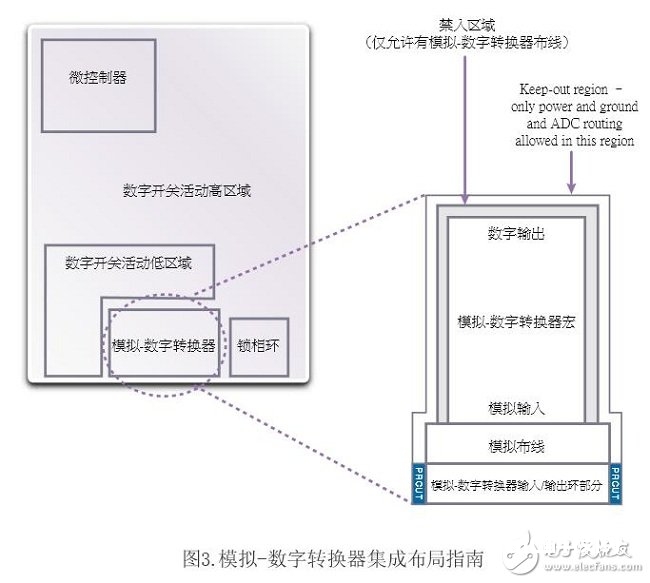

关于一般的模仿-数字转化器,选用这一技能可依照图3中的四个进程进行操作:

1. 将数据转化器(如模仿-数字转化器)远离数字开关电路;

2. 数据转化器数字接口朝向芯片噪声较大区域,而模仿接口朝向芯片较安静区域;

3. 将时钟源(如锁相环)尽或许接近数据转化器;

4. 假如数据转化器接近区域有数字开关走线或逻辑块,请建立一个禁入区域

(即没有金属、晶体管或有源区的区域),以便将数据转化器与逻辑块或布线阻隔开。

技能2:数据转化器接近模仿I/O焊盘

进入模仿-数字转化器输入的任何噪声或不需求的信号将被转化器视为“真”信号,继而呈现在数字输出中。模仿-数字转化器能够区别的最小电压(用最低有用位(LSB)表明)决议数据转化器的准确度,也是模仿-数字转化器最大摆幅(FS)及其分辨率(N)的函数(如以下方程所示)。以0.5V峰-峰最大输入摆幅的12位单端模仿-数字转化器为例,最低有用位规模很小,仅为 122.1μV。

LSB = FS/2N

在如此高的准确度要求下,假如转化的数字信号(进犯者)电容耦合(串扰)到模仿-数字转化器输入(受害者),数字输出信号中耦合的进犯信号的频谱含量或许会超出模仿-数字转化器的噪声本底值,然后影响体系功能(频谱纯度)。

相同,串扰数字-模仿转化器输出对体系功能发生相似的影响,即转化的数字信号电容耦合到数字-模仿转化器输出能够生成超出数字-模仿转化器噪声本底值的频谱含量。

选用差分输入的模仿-数字转化器,或是选用差分输出的数字-模仿转化器,都具有较强的抗共模噪声搅扰才能,因为进犯者均衡地耦合到正负差分信号。为充分利用这种高抗噪声搅扰才能,运用这些数据转化器应一起选用正确屏蔽和外部信号布线等规划技能。

当数据转化器需求外部基按时也会呈现相似的问题。因为基准决议数据转化器的满幅输入摆幅,假如噪声或不需求的信号与基准耦合,就会成为数据转化器输出信号的一部分。

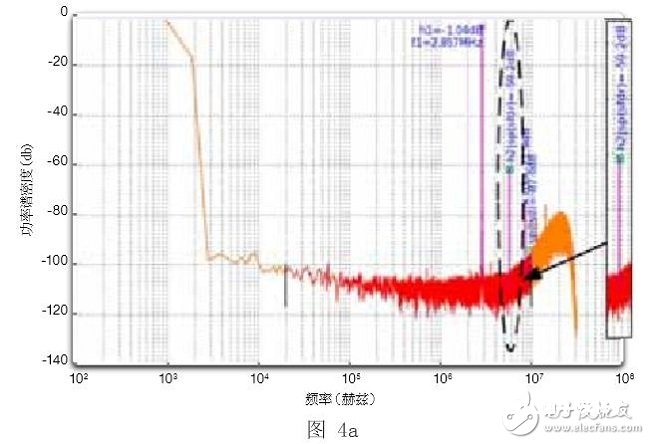

图 4a显现了28纳米12位Sigma-DeltaIQ模仿-数字转化器频谱,能够看到转化器输入与基准信号之间有耦合。这会导致第二谐波(h2)能量过大,将总谐波失真(THD)下降近14dB。相反,图4b显现的是相同IQ模仿-数字转化器在耦合消除后的功能,这会使总谐波失真改进,到达 -72dBc。

基准对流经非零电阻(电阻压降)基准途径的非零电流形成的压降很灵敏。这一效应会在转化中发生体系性的偏移(offset)和增益差错(gain error)。

考虑到这些影响,将数据转化器正确植入体系芯片之后,下一步便是对转化器和I/O之间的模仿信号进行布线,一起选用以下技能:

技能3:坚持模仿布线途径简略

坚持模仿布线途径尽或许简略,使无关信号不太或许耦合到模仿I/O出或基准中。

技能4:添加屏蔽

为尽或许削减要害模仿信号的噪声耦合或串扰,特别是在串扰无法防止的情况下,规划人员应在进犯者和受害者轨道之间添加屏蔽。图5介绍了添加有用屏蔽的正确办法:通过中间层(金属N+1)将以金属N布线的模仿信号轨道A和B与以金属N+2布线的噪声信号C屏蔽开来,彻底掩盖堆叠区域,并与洁净的模仿接地电源衔接。通过在接近信号添加金属层走线,可在同层的金属间(分别是金属N与N+2)完成进一步屏蔽阻隔。

只需在有必要的情况下才添加屏蔽,而且是不沿着一切途径,以防止不用要地添加信号寄生电容。

技能5:坚持差分走线

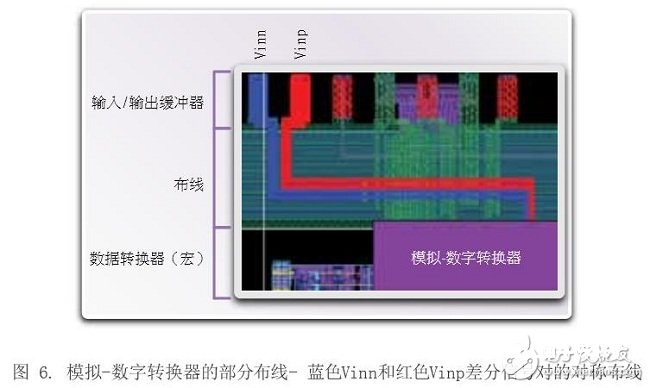

为保证模仿差分信号的共模噪声按捺到达最佳作用,规划师应依据电阻、长度、电容性负载和其他信号的寄生电容耦合、邦定线特征和印刷电路板(PCB)线路等等,对差分信号布线匹配。图6是从模仿-数字转化器到I/O匹配后的输入(赤色Vinp和蓝色Vinn)布线。

技能6:约束电阻压降或阻抗

可通过以下办法保证布线串联电阻不超越数据转化器供给商注明的最大电阻值:

△尽量缩短布线间隔

△运用宽金属布线

△尽量运用多个金属层走线

△运用很多过孔进行衔接

数字输出/输入布线还要求认真仔细地布置。可是,因为布线是在主动数字集成流程中处理,它们的布置天然需求遵从相应的技能,因而不在本文评论之列。

3. 坚持低时钟颤动

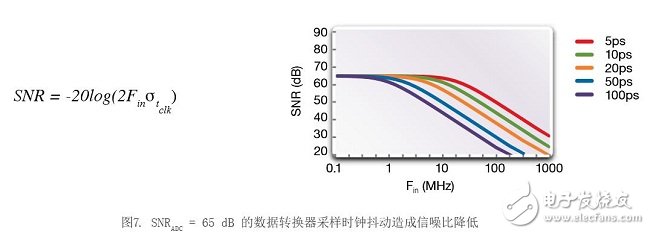

依据数据转化器的体系功能,如通讯接口,取决于采样时钟的质量。模仿-数字转化器信号采样瞬间的不确认性添加了转化噪声,因而下降了转化器功能。采样瞬间的不确认性称为“颤动”。时钟颤动(σtclk)决议了数据转化器可到达的最大理论SNR(信噪比)值。图7显现信噪比是采样时钟颤动的一个函数,将信噪比、时钟颤动和信号频率(Fin)相关起来。以模仿-数字转化器固有的65dB信噪比(SNRADC)为例。

从图7能够看出,采样时钟颤动对转化功能(信噪比)的影响与体系处理低频率信号无关。可是,采样时钟颤动的影响跟着所处理信号的频率增强而添加

因而,体系芯片规划师在规划中有必要考虑到这种影响,能够选用以下技能保证采样时钟质量:

技能7:将时钟源接近数据转化器

将锁相环接近数据转化器,可下降外部信号耦合到时钟线并形成时钟颤动的或许性。

技能8:查看时钟沿速率

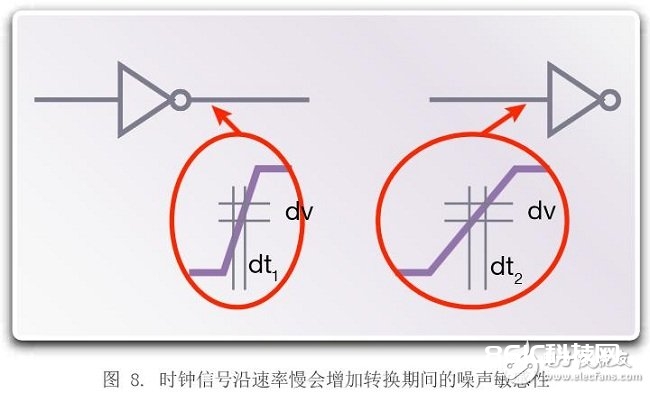

关于时钟途径上的任何电路而言,应保证有满意的驱动强度约束时钟的转化速率。时钟沿转化时刻长会添加噪声灵敏性,因而添加颤动(如图8所示)。依据经历,~100ps的转化时刻是恰当的。

技能9:尽量减小电源域转化

因为信号沿着时钟网络发展,并在不同的电源域进行转化,信号会遭到不同电源的电源噪声耦合的影响。这会导致颤动添加。因而,时钟途径中的一切缓冲器应由同一个电源域(无论是源极电源或终极电源)供给电源。

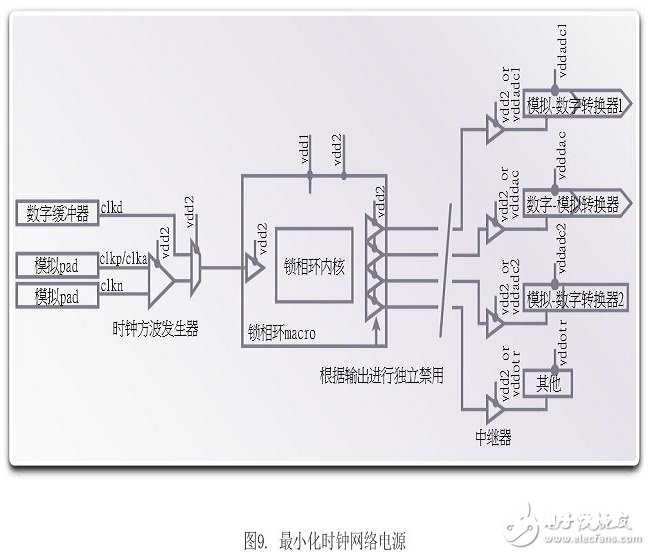

图 9是体系芯片内时钟散布网络的示例。如图所示,锁相环在vdd2电源域生成时钟为四个模块所用,它们是:两个模仿-数字转化器(ADC1和ADC2)、一个数字-模仿转化器和一个通用逻辑块。在这个图中,repeater单元由源极电源(锁相环buffer,vdd2)或是由终极电源(vddadc1、 vdddac、vddadc2或vddotr)供电。

技能10:将时钟信号与进犯信号屏蔽开

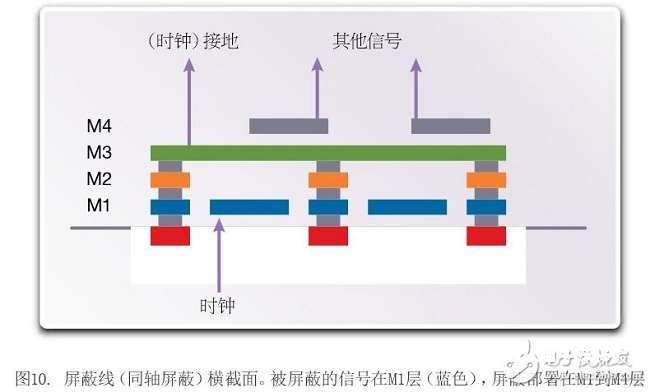

将时钟信号与进犯信号屏蔽开,意图是防止噪声与时钟耦兼并削减颤动。图10介绍了一种屏蔽信号的办法。在图中,信号途径为M1(蓝线),在各个方向与电路中的其他信号屏蔽开。屏蔽层一般与时钟网络相同的接地电位衔接。

4. 坚持电源和接地电源洁净

任何模仿电路的电源按捺比(PSRR)都是有限的。电源和接地电源噪声过大或许影响功能。处理宽带信号时更是如此,原因是低频率时按捺比高,但高频率时按捺比天然会下降。因而,模仿电源应坚持洁净,而且运用时应正确去耦合电容。

还有些其他影响,如布线电阻过大或许导致直流(DC)电压压降超出数据转化器工作规模,还或许形成沟通(AC)电压呼应数据转化器的自生纹波噪声变慢,能够选用以下技能。

技能11:坚持电源和接地布线电阻够小

规划师应遵从数据转化器厂商的主张,使电源和接地布线电阻在约束规模内。这些约束的意图是保证数据转化器的电流耗费形成的压降不会使电源电压超出IP的工作规模。此外,如前面所解说的,走线电阻会使自生纹波呼应变慢。

技能12:运用专用的电源布线

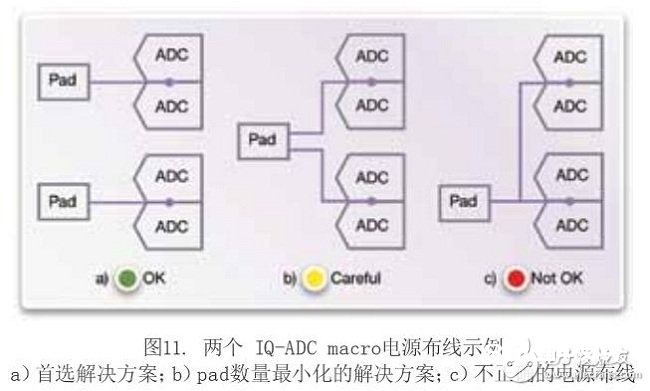

集成多个数据转化器时,规划师应运用专用电源布线,至少包含IO电源。图11a解说了两个IQ-模仿-数字转化器情况下的要求。

关于pad数量受限的体系,只需数据转化器运用相同的时钟频率和相位,多个数据转化器就能够共用相同的IO电源(如图11b所示)。布线有必要与I/O电源(选用星形衔接)阻隔,并坚持电源散布对称。图11c图示说明晰不正确的电源散布。在这个比如中,电源散布没有坚持对称,形成功能下降和串扰。

定论

任何模仿电路的电源按捺比(PSRR)都是有限的。电源和接地电源噪声过大或许影响功能。处理宽带信号时更是如此,原因是低频率时按捺比高,但高频率时按捺比天然会下降。因而,模仿电源应坚持洁净,而且运用时应正确去耦合%&&&&&%。

通过在体系芯片规划中选用Synopsys数据转化器IP,规划师将通过优化的数据转化器IP集成在体系芯片中,满意运用要求和应对体系芯片的恶劣环境。

除了挑选IP外,IP物理集成布置不正确会影响体系功能。选用本文中的技能有助于体系地处理IP集成应战。除供给高质量、牢靠经用的数据转化器IP进行体系芯片集成外,Synopsys可在集成进程中供给广泛的工程支撑(包含具体的集成攻略、集成查看清单和由经历丰富的新思科技运用工程师专门进行集成审阅)并简化体系芯片集成进程,有助保证芯片一次成功。

Synopsys具有超越十五年的数据转化IP研制与运用经历,可供给全面的、经硅验证的200多种DesignWare数据转化器IP产品,包含过采样sigma delta模仿-数据转化器、流水线型模仿-数字转化器、逐次迫临型模仿-数字转化器(SAR ADC)和电流舵数字-模仿转化器。DesignWare数据转化器IP产品具有十分低的功率损耗,占用面积小,支撑从180纳米到28纳米的制程。