作者 / 刘振国 电子科技大学(四川 成都 610054)

刘振国:1992年出世,男,硕士,首要从事功率半导体方面的学习与研讨。

摘要:本文依据LDO的规划思维,规划了一款用于高压集成电路的LDO架构式的基准电路,使其具有宽输入规模的特性。一起,关于该基准电路,文中提出了两种补偿方法,经过添加前馈通路的补偿方法可以使得体系的带宽大大地拓宽,然后减小基准电路的发动时刻(小于5μs)。别的,在该基准电路的根底上添加了上电复位电路,然后进步体系可靠性。终究依据CSMC 0.5μm 600V BCD工艺对规划进行仿真验证。

0 导言

在模拟集成电路中,基准作为一个最根本的单元,它的功用在很大的程度上影响着整个体系的功用[1]。在各种不同的体系中,对基准单元也有着不一样的要求。比方,在一些低功耗的体系中,功耗是基准的要害目标。在一些敏感性的体系中,电源按捺比(PSRR)以及抗噪功用则至关重要。而跟着集成电路工业的不断开展,各种电子产品也不断朝着小型化、智能化的方向开展。由此,又对基准单元提出了新的要求。在一些高压集成电路(HVIC)中,如智能功率模块(IPM)、LED驱动、同步整流等,因为对整个体系的功用提出了更多的要求,故基准单元在HVIC中也逐渐变成了必不可少的一部分。而在HVIC中,则要求基准电路需求有较宽的供电规模以及可靠性。本文正是依据现在在HVIC中对基准电路提出越来越高的要求的前提下,规划了一款用于HVIC的基准电路。

1 电路原理及构架

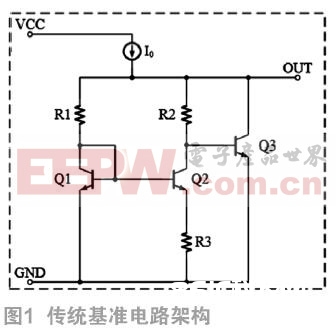

1.1 传统带隙基准电路架构及原理

传统的带隙基准电路结构如图1所示[2]。其间,Q1、Q2以及R3构成与绝对温度成正比(PTAT)电流,该电流流经R1时发生PTAT电压,输出电压为Vbe1与该电压之和,而Vbe1又与绝对温度成反比,故输出电压近似为与温度无关。该电路存在以下几个缺陷。首要,该电路的输出电压为固定值,其值取决于所用工艺中的三极管BE结的本征电压,一般约为1.25 V[3]。其次,该电路的供电规模不能在较大的规模内改变,因为VCC的改变简略导致Q1、Q2的集电极电压改变,然后导致电路无法正常作业。因而,该电路结构在高压集成电路中并不适用。

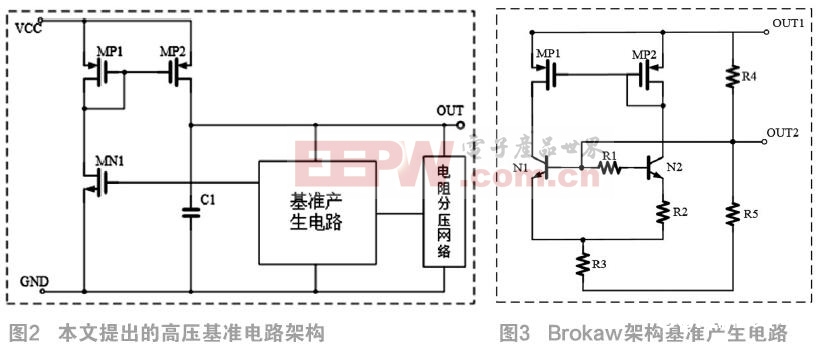

1.2 本文提出的基准电路架构及作业原理

为了习惯可变的输出电压以及较宽的供电规模的需求,本文依据低压差线性稳压器(LDO)的规划思维,提出了一种“LDO”架构式的基准电路,如图2所示。其间,MN1为该LDO的调整管,电阻分压网络则对应于LDO的分压采样电阻,基准发生电路则对应于LDO的比较器。在该LDO架构中,基准发生电路采样输出点电压,经过与自身发生的基准电压进行比较,然后取得较为精确的输出电压。因为该电路选用的是“LDO”架构,故而其自身也具有LDO的一些长处,如供电规模可以在较宽的规模内改变。另一方面,因为电阻分压网络的存在,使得该基准电路的输出电压值并不再局限于传统带隙基准电路。

在图2的电路架构中,基准发生电路的功用直接影响着终究输出基准电压的功用,如温度系数等。因而基准发生电路的架构挑选也是一个需求慎重考虑的要素。在本规划中,选用了Brokaw架构[4],如图3所示。其输出Vout1为:

上式中,第一项为与绝对温度成正比的电压,而第二项为与绝对温度成反比的电压,经过设置适宜的份额系数,即可得到简直与温度无关的基准电压。另一方面,经过适宜规划R4与R5的份额,即可得到非固定值的基准电压Vout1。

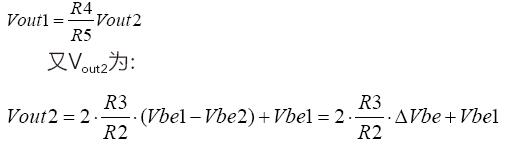

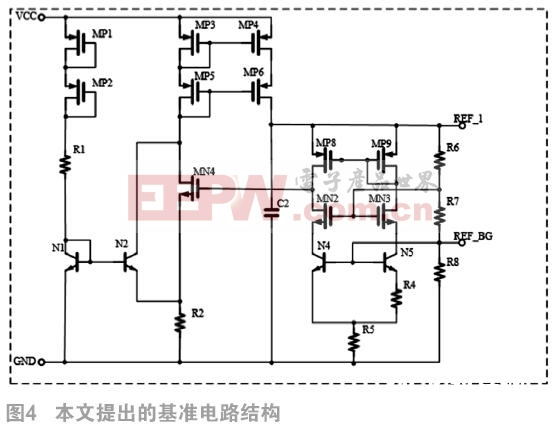

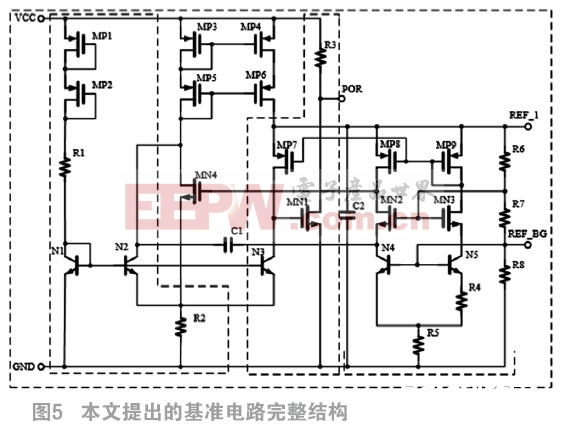

图4为本文提出的“LDO”架构的基准电路的详细电路结构。其间,MP1、MP2、R1、N1、N2以及R2为该电路的发动电路部分,意图是确保该体系可以在上电的进程中脱节简并状况点。另一方面,为了增大该基准结构的电源按捺比,故而电流镜结构均选用了cascode结构。如图中的MP3、MP4、MP5以及MP6构成的cascode电流镜结构。而在基准发生电路中,MN2、MN3与N4、N5也构成了类似于cascode结构,然后进步了电路的PSRR。

1.3 体系的可靠性剖析

在高压集成电路中,可靠性是一个重要的目标。因而,用于高压集成电路中的各个体系模块,一切的功用都必须建立在高可靠性的根底之上。可靠性首要包括两个方面,一方面是要确保体系的稳定性;另一方面,则是需求确保体系在上电、电源动摇等情况下仍可以可靠地作业。

在图4中的电路中,存在着两个以上的极点。第一个极点坐落输出REF_1的方位,因为该方位电流镜结构的原因,故而在cascode电流镜的另一端存在着一个“镜像”极点。第二个极点则坐落“LDO”调整管MN4的输入端。因为该体系存在着两个以上的极点,故体系是不稳定的。该体系有两种补偿方法可以挑选。第一种补偿方法的原理是将第二个极点设置为体系的主极点,第一个极点设置在较高频率方位处。其详细完成方法则可以经过在MN4的栅极添加一个接地的较大电容。这种频率补偿方法长处是较为简略,但相同存在着显着的缺陷,即这种补偿方法会使得体系的带宽大大的减小到几百千赫兹。另一种补偿原理则是经过前馈通路引进额定的零点,使得该零点去补偿第二个极点,这种方法尽管较为杂乱,但却确保了体系的带宽可以增大到几兆赫兹。而体系的带宽则直接关系到体系的呼应速度,因而,关于一些电源电压会动摇的使用中,有着显着的优势。故本文选用的是第二种补偿方法。

体系的可靠性不只要确保体系的稳定性,一起还有确保体系在上电的进程中,各个模块都可以进入正确的作业逻辑状况。发动电路仅仅能确保基准模块在体系上电的进程中进入到正确的作业逻辑,而上电复位电路,则可以确保体系中其它模块在体系上电的进程中可以进入正确的作业状况中[5]。因而,上电复位电路是必要的。在本文提出的基准电路的前提下,为了添加上电复位电路以确保体系可靠性的一起不添加电路规划的杂乱性,故本文提出了一种依据电流比较的上电复位电路,其详细完成电路如图5所示。其间,R3、MP7、MN1以及N3构成上电复位电路。在体系发动的进程中,经过将由N1、N2以及N3构成的电流镜与由MP7、MP8以及MP9构成的电流镜的电流进行比较,然后为高压集成电路整个体系中的其他模块供给上电复位信号。

2 仿真成果及剖析

本文提出的高压基准电路的仿真成果是依据华润上华(CSMC)0.5μm 600 V BCD工艺。且电路目标规划为VCC正常作业于15 V,基准输出电压REF_1为5 V,基准输出电压REF_BG为带隙基准电压,在该工艺下约为1.19 V。

2.1 上电发动进程仿真

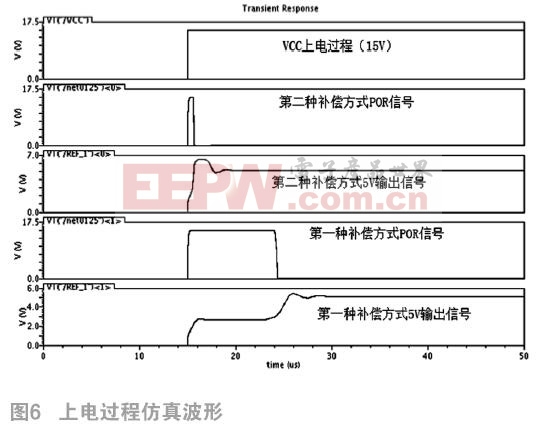

上电发动进程仿真成果如图6所示。在15μs时,VCC经1ns上电。图中别离给出了在上电进程中,两种补偿方法的上电复位信号(POR)以及5 V基准输出信号REF_1。从图中,咱们可以发现,第二种补偿方法的发动时刻相关于第一种补偿方法显着减小。第二种补偿方法5 V输出信号大约在20μs的时分即保持稳定,而第二种补偿方法5 V输出信号大约在30μs时保持稳定。且从POR信号的有用脉宽持续时刻也可以显着发现第二种补偿方法发动速度远远大于第一种补偿方法。一起,POR信号波形也反映了本文所规划的上电复位电路可以在体系上电的进程中,较为精确地为体系的其他部分供给上电复位信号。另一方面,从图6中咱们可以看到,第二种补偿方法上电速度尽管更快,但因为体系的阻尼系数较小,故而在上电的进程中,5 V输出信号会有一个“尖峰”,在一些使用场合中,该尖峰或许会对体系形成必定的危害。在这种使用场合下,则可以挑选第一种补偿方法。从图6中可以显着看到,第一种补偿方法下体系的上电呼应更为滑润。

2.2 体系带宽仿真

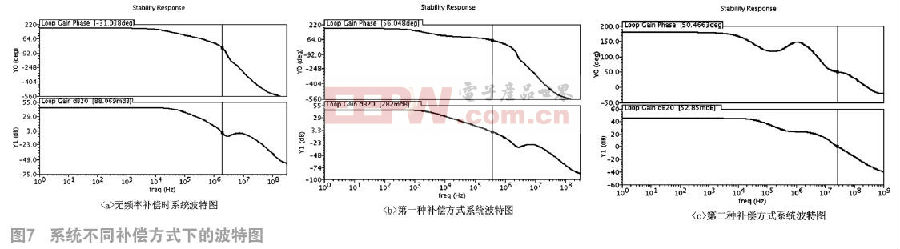

为了更好的了解两种补偿方法差异的原因,图7别离给出了该体系自身以及两种补偿方法下体系的波特图。

从图7中,咱们可以看到,体系在无任何频率补偿方法的情况下,其单位增益带宽(GBW)大约坐落2 MHz的方位,在该方位处其相位裕度为负值,故而体系是不稳定的,这与咱们前面的可靠性剖析是相符合的。图7是体系选用第一种补偿方法的波特图,从和的比照中,咱们可以看到在中,两个极点显着别离,其GBW大约坐落30 kHz的方位,对应的相位裕度约为56度。图7是体系选用第二种补偿方法的波特图。由和的比照中,咱们可以看到在第一个极点之后体系引进了一个零点,该零点的引进导致体系的GBW后移至将近20 MHz的方位,对应的相位裕度约为50度。这儿需求另行阐明的是两种补偿方法的补偿电容值并不持平,其间第二种补偿方法的补偿电容值相对要小一些。从图7的剖析进一步可以得到,第二种补偿方法的确可以很大程度上地进步体系的带宽,然后使体系取得相对较快的呼应速度。

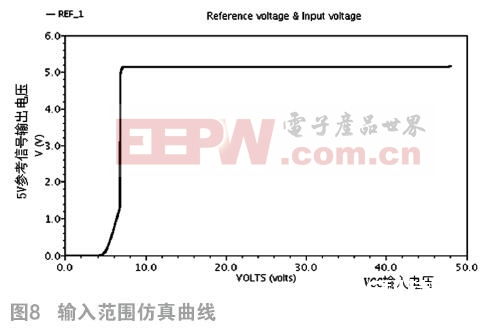

2.3 输入电源电压规模仿真

图8给出了体系输入电源电压规模仿真曲线。从图中咱们可以得到:VCC输入电压约为8 V时,体系即可正常作业。且在VCC输入电压高达40 V时,该基准电路仍可正常作业。乃至可以做出猜测,在工艺条件答应的条件下,该电路可以作业于更大的电源电压规模中。

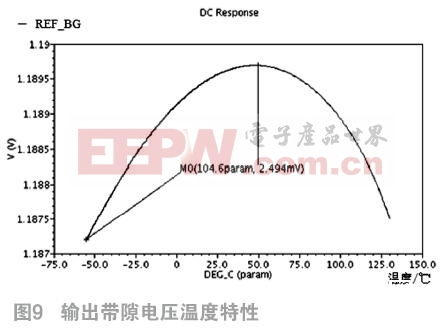

2.4 温度特性仿真

基准电路最为根本的一个功用即为温度特性。本文的基准电路的温度特性首要取决于基准发生电路。因而图9给出了本文带隙输出电压的温度特性曲线。可以得到,在-55 ℃-125 ℃的规模内,输出电压改变规模约为2.5mV。

3 定论

文中所提出的“LDO”架构式的基准电路可以作业于较宽的作业规模内,一起,本文提出了两种不同的频率补偿方法,依据补偿方法的挑选可以到达快发动的意图。另一方面,为了习惯高压集成电路中对高可靠性的要求,本文在所规划的基准电路的根底上添加了上电复位功用,然后可以进一步确保体系中各个功用模块可以进入正确的作业逻辑。终究,文中依据CSMC 0.5μm 600 V BCD工艺对所提出的电路结构进行仿真验证,成果表明本文提出的基准电路适用于高压集成电路。

参考文献:

[1] 曹培栋.微电子技术根底-双极、场效应晶体管原理[M] .电子工业出版社, 2001 .

[2] R.J.Widlar,“New developments in IC voltage regulators,”IEEE J.Solid-State Circuits,vol.SC-6,pp.2-7,Feb.1971.

[3] B.Razavi.Design of Analog CMOS Integrated Circuits.McCraw-Hill Companies Inc.Boston,MA,2001.

[4] A.Paul Brokaw,“A Simple Three-Terminal IC Bandgap Reference,”IEEE Journal of Solid-State Circuits,VOL.SC-9,NO.6,December.1974.

[5] Takeo Yasuda,Masaaki Yamamoto,and Takafumi Nishi,A Power-On Reset Pulse Generator For Low Voltage Applications", Circuits and Systems, 2001,ISCAS 2001,vol.41 May 2001.

本文来源于《电子产品世界》2018年第10期第39页,欢迎您写论文时引证,并注明出处。