导言

DSP+FPGA广泛地运用于各种数字信息处理体系中。在某些特殊的运用场合中,往往需求体系在高温的环境下作业,而体系功耗又不明显增加。尽管一般依据SRAM工艺的FPGA的闪现装备办法现已多种多样,但运用的依据SRAM工艺的FPGA高温功用较差,难以满意高温、低功耗体系的需求。Actel公司依据Flash工艺的FPGA是为军工以及宇航规划的器材,彻底能够担任高温的需求。一般的FPGA都具有上电功耗、装备功耗、静态功耗和动态功耗4种,而Actel依据Flash的FPGA因为上电不需求一个很大的发动电流,并且掉电非易失,不需求装备进程,所以只要静态功耗和动态功耗,没有上电功耗和装备功耗。FPGA在高温下具有更低功耗的优势。

本文依据Actel公司的产品手册及相关文件,规划了一种由DSP操控完结FPGA在线编程的计划,使Actel的FPGA能运用于需求在线晋级的运用场合中,充分发挥其高温高牢靠性、低功耗的优势。当FPGA需求在线编程时,只需经过PC下传FPGA装备指令给DSP,DSP即可把PC下传的FPGA的装备数据经过JTAG写入FPGA完结在线晋级。该办法的长处在于:无需额定装备芯片(DSP在不需求给FPGA进行在线晋级时,可进行其他作业),简略牢靠,在低功耗和高温的运用中显得更为重要。

1 计划规划

图1所示为全体结构规划计划,由PC、UART接口、DSP、RAM存储器、FPGA以及相应的外围辅佐电路构成。其间TMS320F28335芯片是TI公司2000系列的DSP芯片,A3P250为Actel公司ProASIC3系列的FPGA芯片,RAM芯片为IS61LV51216。DSP的4个GPIO与FPGA的JTAG接口相连,而DSP经过串口转USB与PC通讯。这些芯片都能在125℃环境下正常稳定地作业。其间A3P250一般的静态待机电流仅几mA。

体系根本完结进程为:

①依据VC编写文件转化软件,完结FPGA的程序代码(.dat文件)转化成2位十六进制的数据,并存储在txt文档中。

②PC发送下载代码指令至DSP,告诉DSP有代码需求下传。之后就能够把FPGA程序代码(txt文档)以十六进制数据发送给DSP,DSP将收到2位十六进制数据存至外部RAM中。每个地址存两个2位十六进制数据,先存低位,再存高位(存入RAM是因为FPGA的程序代码量比较大)。

③DSP对下载的代码进行CRC校验,回传调试信息。若代码CRC校验成功,PC就能够发送编程指令告诉DSP给FPGA编程。

④DSP操控FPGA JTAG完结读取FPGA设备的ID,验证是否与装备数据中的ID共同。成功,则开端FPGA编程。DSP实时回传编程的调试信息给PC,便利调查调试。编程成功之后,FPGA即可正常运转。

因为串口传输进程只需求两根信号线,即传输线TX以及接纳线RX,故传输协议简略,且较好地避免了JTAG间隔的约束。一起,体系在需求对DSP的装备操控功用进行晋级时,也能够经过串口完结。

2 计划完结

2.1 体系硬件规划和完结

依据计划规划,装备操控电路如图2所示。在本体系中FPGA的JTAG口与DSP的GPIO相连,DSP的SCIA接口经RS485收发器和串口转USB芯片衔接至PC,完结指令下传至DSP和调试信息上传至PC。DSP在外部接口(XINTF)的ZONE7区(共3个区域,另两个为ZONE0、ZONE6)外部扩展1片512 KB×16的外部RAM,用以存储FPGA的装备码流。F28335的XINTF区域能够经过编程来装备特定的等候状况数,选通讯号的树立和坚持时刻,并且读写拜访能够独立装备。当片选信号被拉低时,用户能够拜访该区域。如当程序拜访0x00300000时,就会发生外部地址0x00000和ZONE7区片选信号(

)。别的,需特别注意的是,在编程电压VPUMP和地之间需接0.01μF和0.33%20%20μF滤波电容。不接,或许会导致JTAG鸿沟扫描接入失利等问题。经过PC下传下载代码指令,DSP接纳FPGA的装备码流并保存在外部RAM,之后PC就能够下传指令,指令DSP给FPGA再编程。

2.2 体系软件规划和完结

2.2.1 DerectC介绍和移植

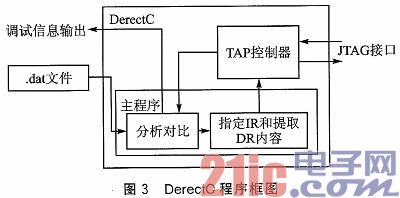

Actel公司依据Flash的FPGA只能经过JTAG接口,而JTAG运用的间隔较近,程序晋级有必要拆开体系封装,较为费事,且简略形成零部件损坏。Derectc3.0是Actel供给的一系列C源程序代码,经过移植它到不同的微处理器,将微处理器通用I/O(需支撑LVTTL电平)衔接至FPGA的JTAG接口,完结FPGA的擦除或再编程。DerectC不包括任何与运用或许设备相关的信息,它只担任解析装备文件中的内容,在JTAG接口上发生用于装备的二进制数据流并读取反应数据,适用于IGL002、SmartFusion2、ProASIC3、IGLOO、Smart Fusion和Fusion系列。DerectC程序框图如图3所示,DerectC需运用Libero生成的.dat格局的FPGA装备文件,文件需求LiberoV8.5以上才干取得。在Libero SoC v11.1中,只需点击gene rate programming data选项即可取得。在运用DerectC时,只需对它作一些修正,增加一些必要的API函数,然后增加至C工程中即可。

把DerectC移植到DSP中,首要经过以下进程:

①针对运用的FPGA系列,增加和去除预处理句子,去除不必要的代码;

②将JTAG信号映射到详细的DSP硬件引脚;

③增加JTAG输入输出函数和装备文件数据块读取函数等必要的API函数。

关于IGLOO2、SmartFusion2、IGLOO、Smart Fusion和Fusion系列的FPGA,移植进程是彻底相同的。移植完结后,关于以上说到的一切Actel的FPGA芯片都能够完结在线编程,仅仅FPGA的装备电路中滤波%&&&&&%的个数或许稍有差异。

别的,DerectC还支撑FPGA的菊花链编程。在移植DerectC时,只需设置好在鸿沟扫描链中IR和DR的长度和额定支撑菊花链的预编译指令。此刻只需一块DSP就能够顺次完结多块FPGA的在线晋级,大大节省了硬件开支。

2.2.2 装备文件格局及转化

A3P系列Libero发生的装备文件包括3个方面的内容:

①头块:包括二进制文件的辨认信息(软件版本号等)、数据块的数目、总的字节长度、方针设备ID和DerectC辨认所支撑的块所需的标志位等,共69字节。

②数据查找表:在DerectC中运用到的各数据块在文件的相对开端地址以及长度,每个数据占5字节。

③数据块:二进制数据码流,用于给FPGA在线编程的首要数据,总长度以字节为单位,最终包括总的data文件的CRC校验码。

便利下传数据,依据VC把整个二进制data文件转化成2位十六进制的数据流并存储在TXT文档中,一起在文件的头部参加标明整个data文件长度的4字节,以便利PC指示DSP下传的数据长度。详细为VC以二进制的方式翻开装备文件,读取其长度写入TXT文档,并每次读取8位二进制数据转化为2位十六进制数据。DSP把收到的数据顺次存在DSP的外部RAM(每个地址存两个字节),先存低位,再存高位。

2.2.3 装备程序数据的下载完结

本规划PC经过USB转串口向DSP发送指令,以指示DSP需求进行什么样的操作。表1为常用的几个串口指令,指令长度都为2字节。

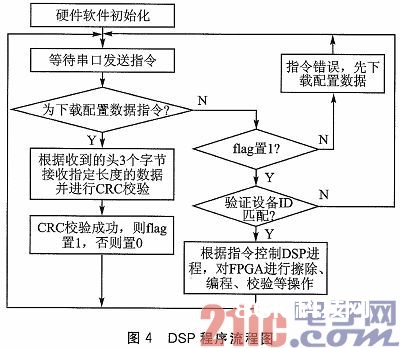

DSP的主程序流程图如图4所示。DSP串口中止等候PC下传FPGA在线编程指令,对收到的FPGA装备数据流进行CRC校验,保证程序的完整性。之后DSP接入FPGA鸿沟扫描链,在JTAG每个TCK上升沿读取TDI的数据或向TD0输出1位数据,在DSP把IR操作数内容写入IR,FPGA会主动把DR放入鸿沟扫描链,进行FPGA的数据读出与写入,然后完结读取FPGA设备ID与装备数据流中的设备ID匹配、FPGA的擦除、装备文件中的数据块写入FPGA等操作,完结在线晋级。

3 试验成果剖析

为了保证装备操控办法的牢靠性,经过串口往DSP下传经过VC转化的FPGA装备文件,DSP接纳到悉数装备文件后会进行CRC校验。查验的成果经过串口实时回传至PC,保证了装备文件的完整性。之后DSP读取FPGA的设备ID,与装备文件的ID进行比照,保证方针设备的正确性,成果相同经过PC显示出来。

在上述验证经过的情况下,DSP开端对FPGA进行擦除操作,之后向FPGA中烧写跑马灯装备码流数据。和Actel的FlashPRO3编程器相同,烧写完结之后会对编程成果进行验证,保证烧写的正确性。以上进程中,DSP串口会回来调试进程信息给PC,以标明程序烧写进程。整个进程完结后,LED灯按预期程序规划有规则地闪耀,无需重新发动。在试验体系环境中,一次装备的时刻约为97 s,与运用Actel的FlashPRO3编程器的时刻相差无几,装备时刻很短。

结语

本规划完结了一种依据DSP GPIO口驱动FPGA的JTAG接口,以及串口对Actel FPGA进行体系的在线编程。不只适用于某一类型的Actel的FPGA,并且适用于IGLOO2、Smart Fus ion2、ProAS%&&&&&%3、IGLOO、Smart Fusion和Fusion系列,适用范围很广。别的,该规划简略,只需将DSP的GPIO与FPGA的JTAG中4个必要的引脚相连,串口下传指令和FPGA装备数据,无需额定的装备芯片,避免了JTAG间隔的约束,且选用的芯片彻底满意高温、低功耗的要求,具有高速高、牢靠性等长处,便利多任务的切换。运用本体系无需重启就能够动态地更新FPGA运用,使得Actel的FPGA运用能不受在线晋级的间隔困扰。