回忆大局OFFSET束缚

在时钟行中运用Pad-to-Setup和Clock-to-Pad列为一切出于该时钟域的I/O途径指定OFFSETs。

为大多数I/O途径进行束缚的最简略办法——但是,这将会导致一个过束缚的规划。

指定管脚的OFFSET束缚

运用Pad-to-Setup和Clock-to-Pad列为每个I/O途径指定OFFSETs。

这种束缚办法适用于只要少量管脚需求不同的时序束缚。

更常用的办法是:

1. 为Pads生成Groups

2. 对生成的指定Groups进行OFFSET IN/OUT束缚

双沿时钟的OFFSET束缚

OFFSET束缚指明晰FPGA管脚的输入数据和初始时钟之间的联系。

初始时钟沿在周期束缚界说中呈现关键词“高”和“低”。

——高:初始时钟上升沿(默许),即上升沿锁存数据

——低:初始时钟下降沿

假如一切的I/O都由时钟的一个沿操控,那么你能够运用这个关键字高或低进行周期束缚。

假如两个沿都用到,你就必须进行两个OFFSET的束缚。

——每个OFFSET对应一个时钟沿

——DDR寄存器也是这样运用的一个比如

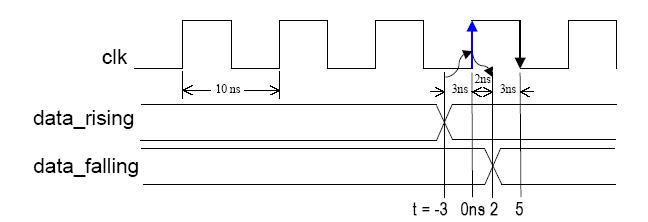

双沿时钟的OFFSET IN束缚

输入数据在上升沿或许下降沿之前3ns有用——周期束缚为10ns,初始上升沿,占空比为50%。

为每个时钟沿生成一个时钟Groups

——输入时钟的上升沿,OFFSET = IN 3ns BEFORE CLK;

——输入时钟的下降沿,OFFSET = IN -2ns BEFORE CLK;(在初始时钟的上升沿后2ns = 时钟下降沿前3ns)

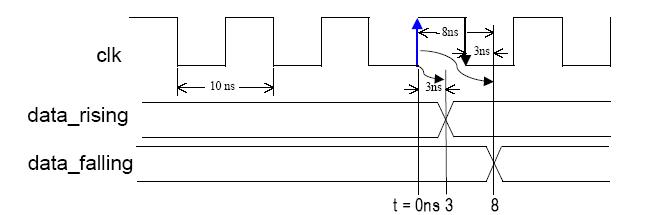

双沿时钟的OFFSET OUT束缚

输出数据必须在时钟的上升沿或许下降沿后3ns内有用——周期束缚为10ns,初始上升沿,占空比为50%。

为每个时钟沿生成一个时钟Groups

——输入时钟的上升沿,OFFSET = OUT 3ns AFTER CLK;

——输入时钟的下降沿,OFFSET = OUT 8ns AFTER CLK;(在初始时钟的上升沿后8ns = 时钟下降沿后3ns)

问题考虑

特定途径时序束缚怎么改进了规划功能?

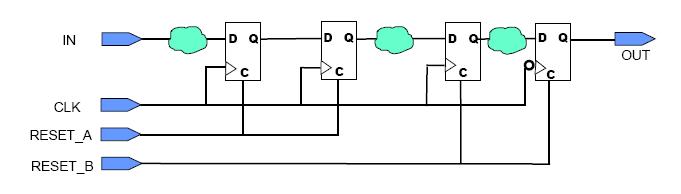

你怎么束缚这个规划使其内部时钟频率抵达100 MHz?

输入(数据)将在时钟CLK的上升沿抵达前3ns内有用。输出数据必须在时钟CLK的下降沿后4ns内稳定下来。写出适宜的OFFSET束缚?

问题解答

特定途径时序束缚怎么改进了规划功能?

——它使得履行东西愈加灵敏的抵达你的时序要求。

你怎么束缚这个规划使其内部时钟频率抵达100 MHz?

——给时钟信号CLK施加一个10ns的大局周期束缚。

写出适宜的OFFSET束缚?

——OFFSET = IN 3 ns BEFORE CLK; OFFSET = OUT 4 ns AFTER CLK;