Microchip新型PIC® MCU系列 将软件任务移交硬件加快系统响应速度-Microchip PIC18-Q43系列产品将更多的独立于内核的外设(CIP)及功能丰富的开发工具生态系统相结合,可改善实时控制和互联应用的设计 在基于单片机(MCU)的系统设计中,软件系统通常是影响产品上市时间和系统性能的瓶颈。Microchip Technology Inc.(美国微芯科技公司)推出的下一代PIC18-Q43系列产品可以将多种软件任务转移至硬件上实现,从而帮助开发者更快地将性能更高的解决方案推向市场。 新系列产品集成了丰富的外设,功能多样且简单易用,通过方便

基于定时器和计数器改善微控制器的设计性能-定时器和计数器也许在MCU设计中最普遍的外设。几乎任何应用程序可以使用一个定时器或计数器,以提高性能,降低功率,或通过用一个简单的定时器或计数器中断替换repetitive-织或钩织CPU的操作简化设计。您可能没有然而,使用了一些较新的定时器/计数器单元,以及一些现已高级功能可以提高您的设计,甚至更多。本文将很快回顾一些,你可以用它来改善你的设计与流行的微控制器系列具有特别强调功能的自主经营和电机控制说明性的例子在新定时器/计数器功能。

Microchip新型PIC® MCU系列 将软件任务移交硬件加快系统响应速度-Microchip PIC18-Q43系列产品将更多的独立于内核的外设(CIP)及功能丰富的开发工具生态系统相结合,可改善实时控制和互联应用的设计 在基于单片机(MCU)的系统设计中,软件系统通常是影响产品上市时间和系统性能的瓶颈。Microchip Technology Inc.(美国微芯科技公司)推出的下一代PIC18-Q43系列产品可以将多种软件任务转移至硬件上实现,从而帮助开发者更快地将性能更高的解决方案推向市场。 新系列产品集成了丰富的外设,功能多样且简单易用,通过方便

基于Fusion系列FPGA器件实现水温测控系统的设计-方案三 该方案采用CortexM1 FPGA系统来实现。系统硬件用单芯片完成多方面功能,软件编程灵活,自由度大,可用软件编程实现各种控制算法和逻辑控制,还可实现数码显示和键盘设定等多种功能,系统电路框图如图1所示。

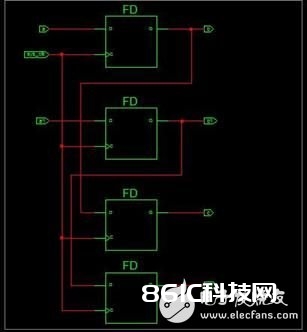

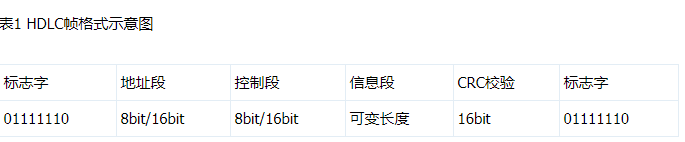

基于FPGA器件EPF10K20RC240-3实现HDLC协议控制器的应用方案-HDLC(High Level Data Link Control)协议是通信领域中应用最广泛的协议之一,它是面向比特的高级数据链路控制规程,具有差错检测功能强大、高效和同步传输的特点.目前市场上有很多专用的HDLC芯片,但这些芯片大多因追求功能的完备,而使芯片的控制变得复杂.实际上,对于某些特殊场合的特殊用途(如手持式设备),我们只需选择HDLC协议中最符合系统要求的部分功能,设计一种功能相对简单、使用灵活的小型化HDLC协议控制器.另一方面,随着深亚微米工艺技术的发展,FP-GA(Field Programmable Gate Array)芯片的规模越来越大,其单片逻辑门数已超过上百万门.同时它还具有设计开发周期短、设计制造成本低、可实时在线检验等优点,因此被广泛用于特殊芯片设计中.本设计中采用Altera公司的FLEX10K芯片EPF10K20RC240-3来实现HDLC协议控制器.

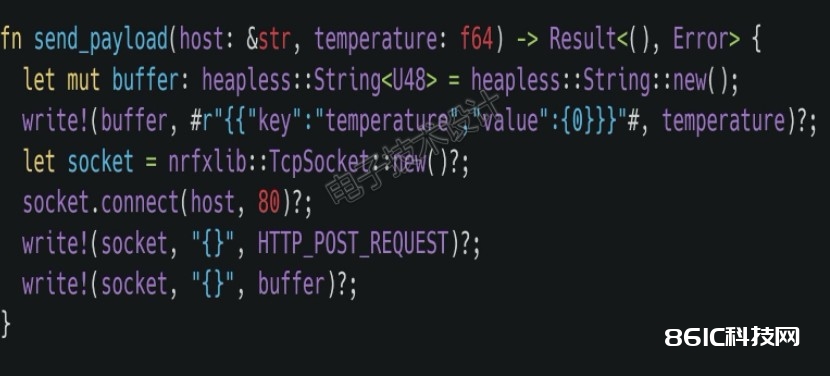

Rust编程语言推出独特“借阅检查器”功能-近年来,消费、医疗、农业、工业以及其他领域对物联网(IoT)连接的需求不断增长,产品开发咨询公司42 Technology表示,制造商希望为最终用户带来与众不同的产品,因此想利用物联网连接来添加功能,或为基于服务的产品生成新的数据流。

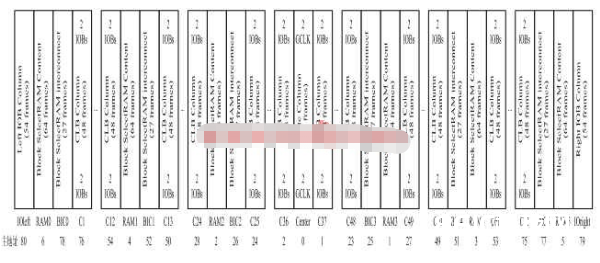

FPGA和其他可编程逻辑IC 的不同之处在于哪- FPGA是一种集成电路,包含许多(64至10,000多个)相同的逻辑单元,可以将它们视为标准组件。每个逻辑单元可以独立承担一组有限的个性中的任何一个。单个单元通过电线矩阵互连和可编程开关。通过为每个单元指定简单的逻辑功能并有选择地闭合互连矩阵中的开关来实现用户的设计,通过将这些基本模块组合以创建所需的电路来创建复杂的设计现场可编程意味着FPGA的功能由用户的程序定义取决于设备的具体情况,该程序会在电路板组装过程中永久或半永久性地“刻录”,或在每次开机时从外部存储器加载。

采用模块化设计实现基于FPGA的动态可重构功能-应用FPGA动态部分重构功能使硬件设计更加灵活,可用于硬件的远程升级、系统容错和演化硬件以及通信平台设计等。动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-Based Partial Reconfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。