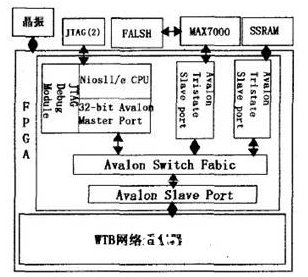

基于Nios II嵌入式系统的FPGA配置文件下载更新设计-现场可编程门阵列(FPGA,Field Programmable Gate Array)是一种高密度可编程逻辑器件,其逻辑功能是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器(SRAM )来实现的,具有可重复编程性,可以灵活实现各种逻辑功能。由于FPGA器件采用的是SRAM 工艺,在断电的情况下FPGA内的配置数据将丢失。所以,在典型的采用FPGA器件的电子系统中通常将FPGA 的配置数据存放于其兼容的SPROM 中,上电时由控制电路将SPROM中的配置数据装入FPGA器件中。但是通常的SPROM价格昂贵,且是一次性,不利于FPGA程序的更新,所以有必要分析FPGA 的配置原理,采用廉价、能重复使用的方式配置FPGA。

基于LabVIEW FPGA模块程序设计特点的FIFO深度设定详解-为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO不同深度的实验表明,采用该方法设定的FIFO深度能够比较好地满足系统对数据连续传输的要求。研究结果对深入展开研究和工程设计具有一定的指导意义。

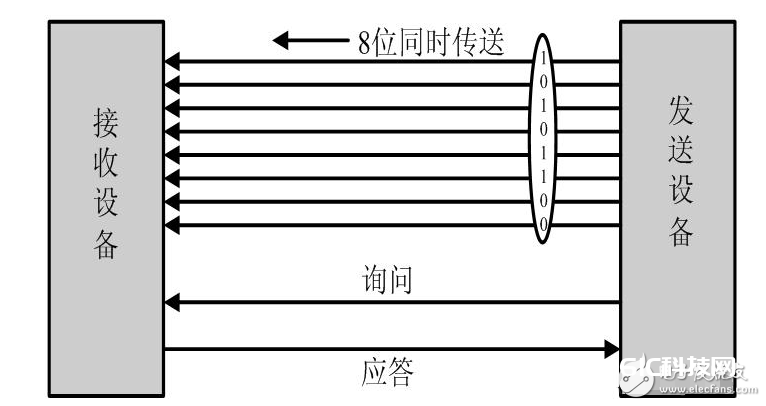

一文读懂UART/RS232协议学习_串行和并行通信介绍-串行和并行通信 在微型计算机中,通信(数据交换)有两种方式:并行通信和串行通信。 并行通信——是指计算机与I/O设备之间通过多条传输 线交换数据,数据的各位同时进行传送。 串行通信——是指计算机与I/O设备之间仅通过一条传 输线交换数据,数据的各位是按顺序依次一位接一位进行传送。 应该理解所谓的并行和串行,仅是指I/O接口与I/O设备之间数据交换(通信)是并行或串行。

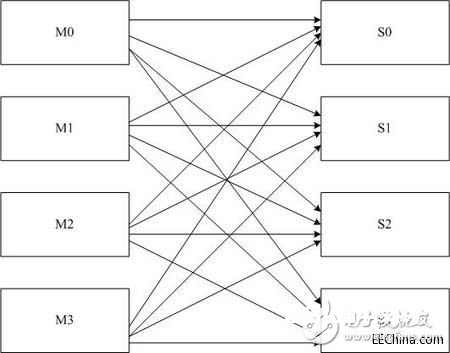

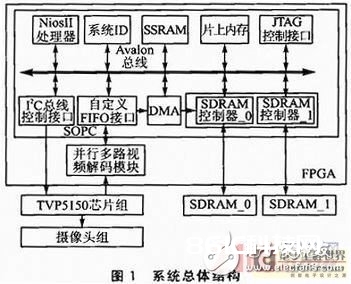

一种基于FPGA的高速多路视频数据采集系统设计详解-数字图像处理技术广泛地应用在信息处理领域,如何高效、灵活地将现实世界图像数字化是信息处理的关键技术之一。本文基于FPGA技术设计了一个高速多路视频数据采集系统。基于Altera Cyclone II芯片,构建一个集成NiosII软核处理器、存储器、I/O接口、自定义外设的可编程片上系统系统(System On Programmable Chip,SOPC)。利用FPGA高速并行处理能力,可同时对多路视频数据进行视频解码,大大提高系统数据采集前端的处理能力。

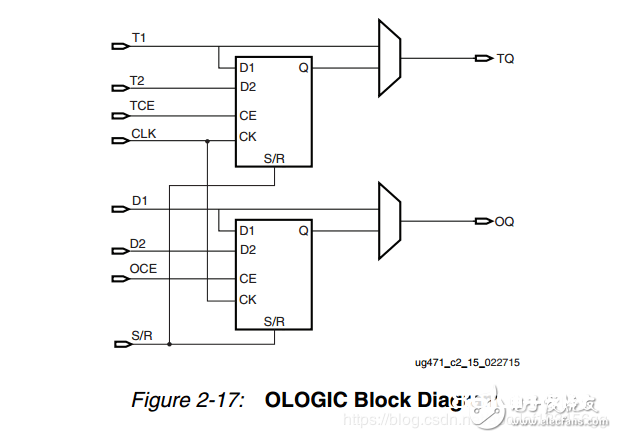

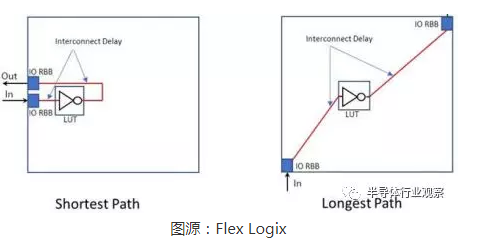

关于嵌入式FPGA的内容详解- 换句话说,eFPGA是一种数字可重构结构,由可编程互连中的可编程逻辑组成,通常表现为矩形阵列,数据输入和输出位于边缘周围。 eFPGA通常具有数百或数千个输入和输出,可连接到总线、数据路径、控制路径、GPIO、PHY或任何需要的器件。

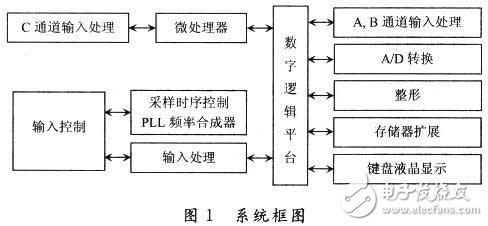

采用ARM和单片机的CPLD/FPGA高速数据处理系统-传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差;受限于计算机插槽数量和中断资源;不便于连接与安装;易受机箱内电磁环境的影响。

失眠症的福音:多功能检测仪Sense助你改善睡眠质量-Sense是一款外形美观的床头艺术品,但实际上它拥有一颗高科技的芯,可以改善人的睡眠质量。Sense的强大之处在于,它可以将人的睡眠数据和室内环境数据结合起来分析,从而找到影响睡眠质量的关键所在,从而找到改善计划。