ADuCM360的主要特性及应用范围分析-该器件包含一个片上32 KHz振荡器和一个内部16MHz高频振荡器。该时钟通过可编程时钟分频器路由,并由此产生MCU内核时钟工作频率。最大内核时钟速度为16MHz,不受工作电压或温度的限制。

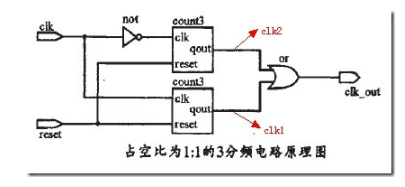

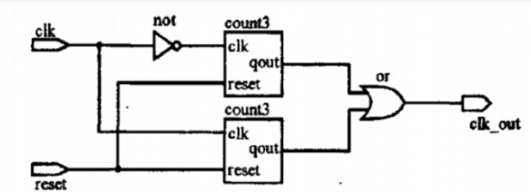

基于FPGA的整数倍分频器设计-偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

基于可编程逻辑芯片和CPU实现数字锁相环频率合成器的设计-数字锁相环频率合成系统的工作原理是:锁相环对高稳定度的基准频率(通常由晶体振荡器直接或经分频后提供)进行精确锁定,环内串接可编程的分频器,通过编程改变分频器的分频比,使环路总的分频比为N(可通过编程改变),从而环路稳定的输出 N倍的基准频率,而整个程序和系统的控制是要由CPU来完成的。

本站为您提供的对32.768KHz晶振的极致研究、专业应用,32.768KHz是一个标准的频率, 32.768KHz的时钟晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1Hz秒信号,即秒针每秒钟走一下,石英钟内部分频器只能进行15 次分频,要是换成别的频率的晶振,15次分频后就不是1Hz的秒信号,时钟就不准了。