通过并行流水线结构实现直接型FIR滤波器的系统设计方案-在用FPGA或专用集成电路实现数字信号处理算法时,计算速度和芯片面积是两个相互制约的主要问题。实际应用FIR滤波器时,要获得良好的滤波效果,滤波器的阶数可能会显著增加,有时可能会多达几百阶。因此,有必要在性能和实现复杂性之间做出选择,也就是选择不同的滤波器实现结构。这里运用并行流水线结构来实现速度和硬件面积之间的互换和折衷。

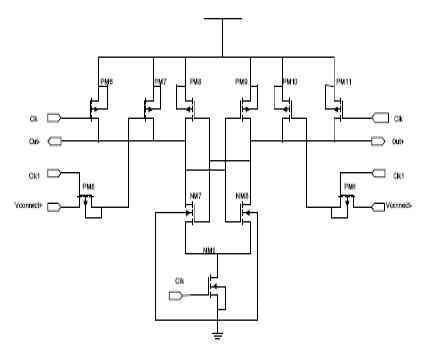

高速比较器电路的设计实现和仿真实验分析-在任何一个高速高分辨率的模数转换器中,高精度和快速比较器总是起着至关重要的作用。与其它种类的ADC相比,流水线ADC 有着高速、高分辨率的特点。因此,它在电子系统中,有着广泛的应用。流水线ADC由许多子FLASHADC 构成。流水线ADC 的特性中,特别是速度,功耗和失调电压对整个电路有着很重要的影响。

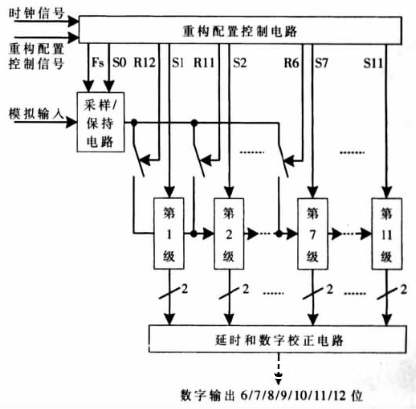

适用于多标准收发器中的可重构流水线ADC的应用设计-运算放大器是采样保持电路的核心,其性能直接影响采样保持电路的速度和精度,是流水线ADC电路设计的关键。本设计采用共源共栅两级运算放大器[4],其第一级采用高速的套筒式共源共栅运算放大器来弥补两级运算放大器速度慢的缺点,因此整个电路具有相对较高的增益、较高的速度、较低的功耗和噪声及较大的输出摆幅等特点,其电路结构如图3所示。

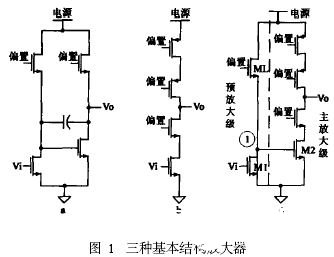

基于新放大器结构在流水线模数转换器中的应用研究-本文提出了一种新颖的放大器结构。它由两部分组成:前面为跨导放大器,后面则是由电阻反馈形成的跨阻放大器,两种放大器的组合构成了具有高输入阻抗、低输出阻抗的电压放大器。与普通放大器不同的是,在我们设计的工作条件下,它输出端的极点几乎不受负载电容的影响。用该放大器作为预放大级,驱动一单级主放大器所构成的两级运放在负载电容为4pf的情况下实现了超过1GHz的增益带宽积,瞬态分析的结果表明它可以在10ns内达到0。01%的精度(闭环增益为8),而功耗仅有25mW,远低于同性能其他结构的放大器,非常适合作为高速高精度流水线模数转换器中的首级余量放大器使用。

关于利用FPGA做图像处理的相关知识盘点-用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性。因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA。例如在一些分选设备中图像处理基本上用的都是FPGA,因为在其中相机从看到物料图像到给出执行指令之间的延时大概只有几毫秒,这就要求图像处理必须很快且延时固定,只有FPGA进行的实时流水线运算才能满足这一要求。

随着嵌入式技术的发展,工控机产业迎来新改革-近年来,嵌入式工控机在工控机的应用中日趋成熟,开始在一些领域取代传统工控机,比如从工业流水线,到智能电视、智能冰箱、智能音箱,再到智慧医疗设备,多媒体设备等等。