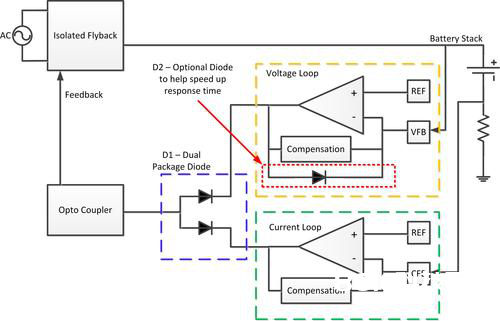

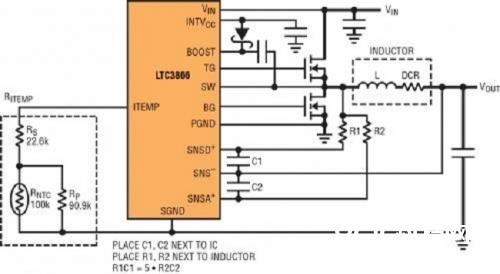

当电流模式开关电源与电压模式开关电源相比时,前者有几种优势:(1) 高可靠性,具快速、逐周期电流采样和保护能力;(2) 简单和可靠的环路补偿,全部用陶瓷输出电容器就可稳定;(3) 在大电流多相 (Po

基于FPGA芯片Stratix II EP2S60F672C4设计实现了数字基带预失真系统中的环路延迟估计模块。该模块运用了一种环路延迟估计新方法,易于FPGA实现。同时,在信号失真的情况下也能给出正

AVS 视频标准中,自适应环路器在实现时存在许多条件运算(如滤波强度的计算、边界阈值和跳转等的计算)及其对于数据的访问比较繁琐,使得滤波器的算法复杂度很高。并且块效应可能会出现在每个8×8 块的边界上

数字时钟管理模块与嵌入式块RAM-业内大多数FPGA 均提供数字时钟管理( 赛灵思公司的全部FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 提供数字时钟管理和相位环路锁定。相位环路锁定能够

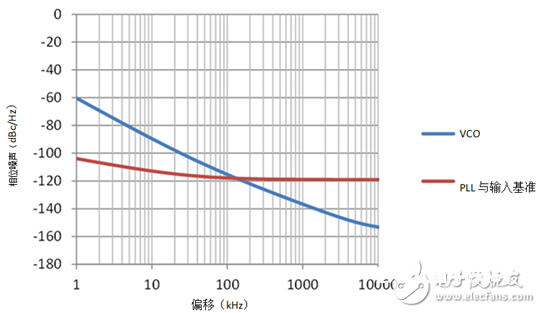

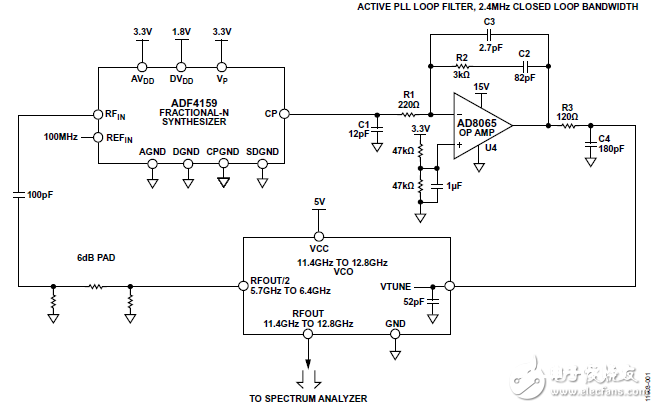

RF至13GHz超快速建立PLL-在PLL和VCO频率合成系统中,获得低于5 µs的频率和相位建立时间需极宽的环路带宽。环路带宽(LBW)定义控制环路的速度。更宽的LBW允许更快的建立时间,但会牺牲相