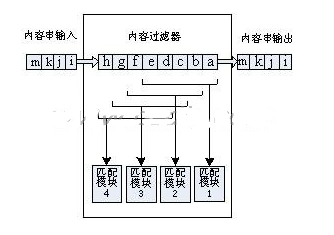

采用StratixII系列的EP2S60FPGA芯片实现报文内容过滤算法研究分析-可见,位置i上的hash函数可以通过i-1位置上的hash函数简单的算出。并且如果dij=di+1j的话,可见t时刻的hi和t+1时刻的hi-1是相同的,这样所有Hi就可以通过并行的移位结构在一个时钟周期内完成,而不用等待Hi-1的计算结果。相应的结构如图4所示,算法可以在一个时钟周期内算出所有Hi的值,非常便捷。

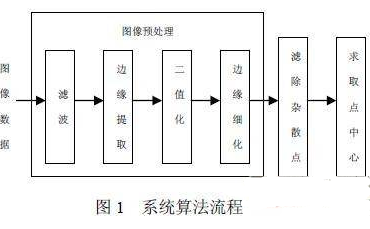

基于FPGA的SOPC技术实现视觉测量系统的解决方案-传统的视觉测量系统主要是在 PC机上采用软件方式实现,由于其专用性不够高,因此处理速度较慢。近年来,基于 FPGA的 SOPC技术的出现,使 FPGA高效的硬件并行信号处理能力和软件控制的灵活性完美的结合到一起。在 SOPC系统中,对速度要求高的算法可以采用自定义硬件逻辑的方法实现;而用硬件难以实现的复杂算法以及控制流程可以在 Nios II核中以软件方式实现。因此基于 SOPC技术的系统具有很好的实时性、灵活性以及可扩展性。设计者可以自由的进行软硬协同设计,并且可以在设计的各个阶段不受限制的修改设计而无需重新构建硬件平台。

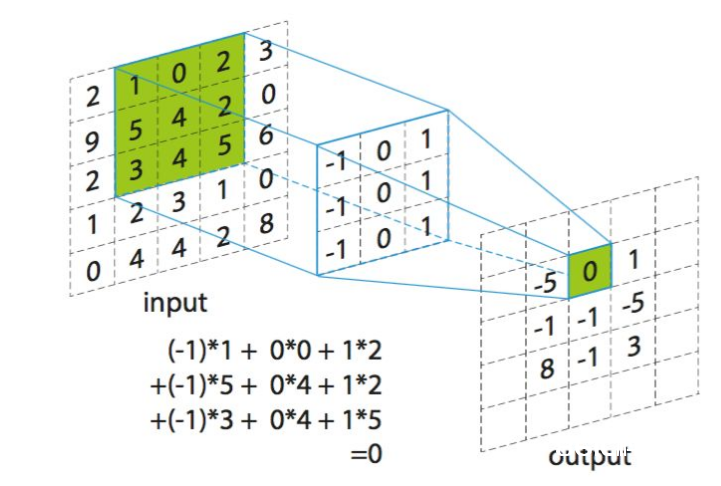

一种采用像素积分单元阵列结构的FPGA实现与性能分析-Adaboost 算法是Freund 和Schapire 于1995 年提出的,全称为Adaptive Boosting。它是 Boosting 算法的改进,意为该算法通过机器训练与学习不断自适应地调整假设的错误率,这 种灵活性使得Adaboost 算法很容易与实际应用联系起来。2001 年,微软研究院的P.Viola 提出了基于Haar 特征的Adaboost 算法,创造性地将积分图的概念引入到人脸检测的特征 计算当中,由于此算法使用了大量尺寸不一的矩形作用来表征人脸。并且该算法中用以检测 人脸的分类器是采用的级联结构,按照由弱到强的顺序组织的,其优点在于按照统计概率, 在图像检测的一开始就能够将大部分不包含人脸的区域排除在外,省去了后面计算负载更重 的检测步骤,以此达到检测速度提升的目的。经过实际测试,P3 700MHz 的处理器对352*288 的图像进行检测的速度为15 帧/秒。但是如果在嵌入式平台上运行的话

赛灵思FPGA卷积神经网络,云中的机器学习- 人工智能正在经历一场变革,这要得益于机器学习的快速进步。在机器学习领域,人们正对一类名为“深度学习”算法产生浓厚的兴趣,因为这类算法具有出色的大数据集性能。在深度学习中,机器可以在监督或不受监督的方式下从大量数据中学习一项任务。大规模监督式学习已经在图像识别和语音识别等任务中取得巨大成功。

基于GPS中频信号源的FPGA设计实现方案-在GPS接收机的设计中,为了检验和完善信号处理算法,需要在本地获得GPS数字中频信号数据。采用真实的数据并不是最佳选择,主要是因为其中的许多信号属性无法控制,也无法模拟不同的接收环境和干扰情况,这给算法的验证测试带来麻烦;而且存储GPS真实数据需要消耗大量的硬件资源。解决这一问题的有效方法是设计一个能够产生GPS数字中频信号并且参数可控的仿真信号源。

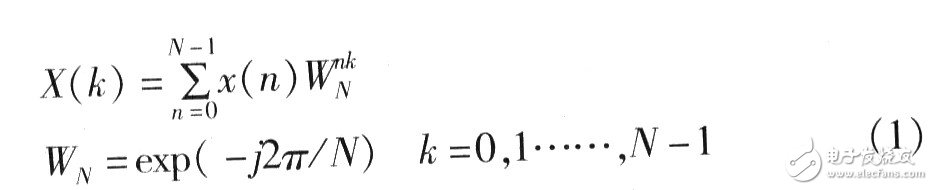

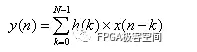

采用FPGA实现FFT算法-随着数字技术的快速发展,数字信号处理已深入到各个学科领域。在数字信号处理中,许多算法如相关、滤波、谱估计、卷积等都可通过转化为离散傅立叶变换(DFT)实现,从而为离散信号分析从理论上提供了变换工具。

Xilinx Vivado HLS中Floating-Point(浮点)设计介绍-尽管通常Fixed-Point(定点)比Floating-Point(浮点)算法的FPGA实现要更快,且面积更高效,但往往有时也需要Floating-Point来实现。这是因为Fixed-Point有限的数据动态范围,需要深入的分析来决定整个设计中间数据位宽变化的pattern,为了达到优化的QoR,并且要引入很多不同类型的Fixed-Point中间变量。而Floating-Point具有更大的数据动态范围,从而在很多算法中只需要一种数据类型的优势。Xilinx Vivado HLS工具支持C/C++ IEEE-54标准单精度及双精度浮点数据类型,可以比较容易,快速地将C/C++ Floating-Point算法转成RTL代码。

随着技术的进步 在FPGA中实现信号处理算法成为有吸引力的替代方案-过去十几年,通信与多媒体技术的快速发展极大地扩展了数字信号处理(DSP)的应用范围。眼下正在发生的是,以更高的速度和更低的成本实现越来越复杂的算法,这是针对高级信息服更高带宽以及增强的多媒体处理能力等需求的日益增加的结果。一些高性能应用正在不断发展,其中包括高级有线和无线音频、数据和视频处理。

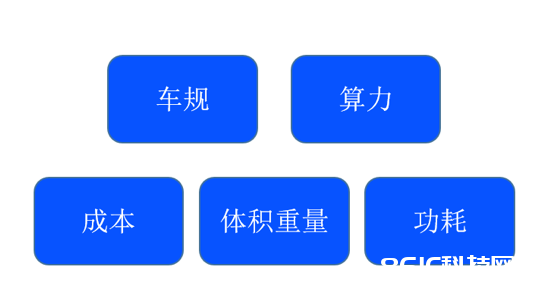

自动驾驶技术中FPGA面临的挑战与实践-人工智能技术是自动驾驶的基础,算法、算力和数据是其三大要素。本文探讨的就是其中的“算力”。算力的高低,不仅直接影响了行驶速度的高低,还决定了有多大的信息冗余用来保障驾驶的安全。