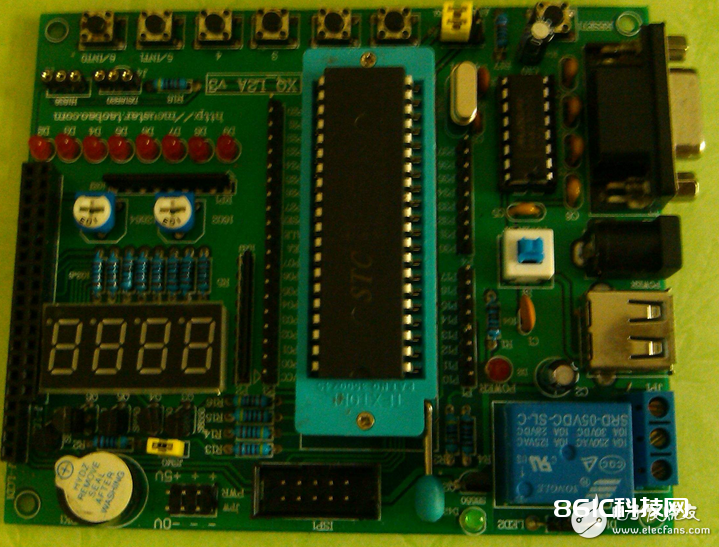

单片机如何执行代码命令,单片MCU内存如何分配?-由于本次进入指令寄存器中的内容是74H(操作码),以译码器译码后单片机就会知道该指令是要将一个数送到A累加器,而该数是在这个代码的下一个存储单元。所以

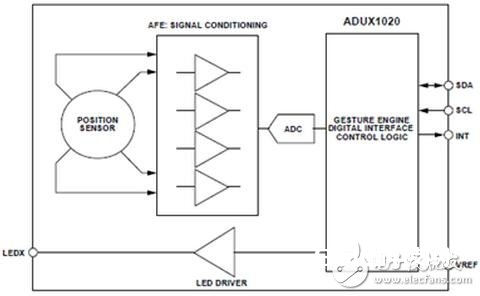

14位模数ADC+20位突发累加器的ADI手势识别传感器方案-ADI公司的ADUX1020是集成了14位模数转换器(ADC)和20位突发累加器的高效率光度传感器,采用单点检测改善了应用的可靠性,同时所

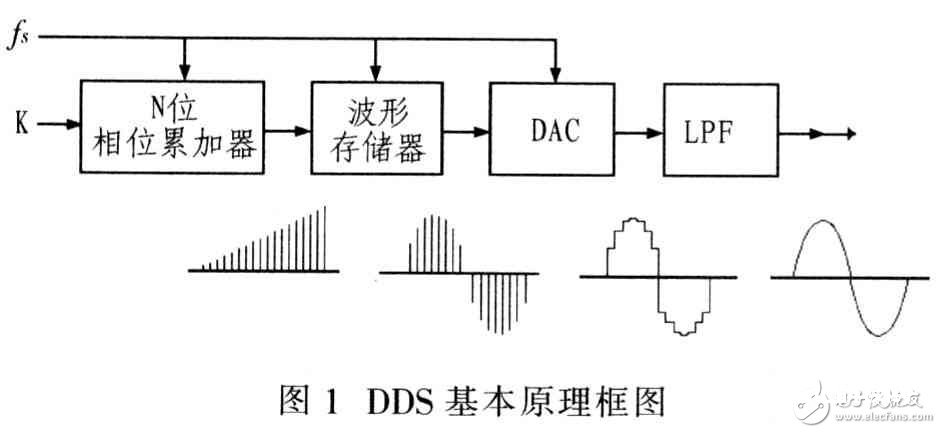

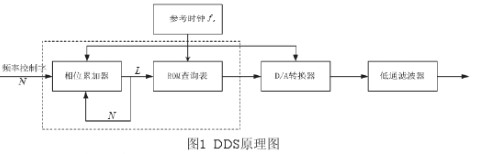

采用FPGA实现DDS任意波形发生器设计-在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A转换器转换成模拟量输出,从而合成波形。滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

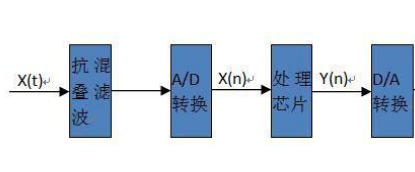

简析DSP的工作原理-DSP内部除了算术逻辑单元(ALU),还包括多个处理单元——辅助寄存器运算单元(ARAU),累加器(ACC),硬件乘法器(MULT),以及丰富的总线资源,它们的存在使得DSP可以拥有一些数字信号处理的特殊DSP指令,以及可以快速的访问存储以及并行操作的能力,保证数字信号处理中的实时的高速度、高精度累加即乘法等运算。

在FPGA硬件平台通过采用DDS技术实现跳频系统的设计-DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。

在FPGA硬件平台通过采用DDS技术实现跳频系统的设计-DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。

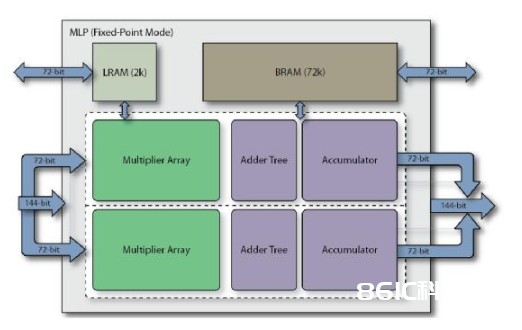

震惊!FPGA运算单元可支持高算力浮点-MLP全称Machine Learning Processing单元,是由一组至多32个乘法器的阵列,以及一个加法树、累加器、还有四舍五入rounding/饱和saturation/归一化normalize功能块。

基于Adaboost算法结合Virtex5平台如何提升FPGA器件的性能-本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25×18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。