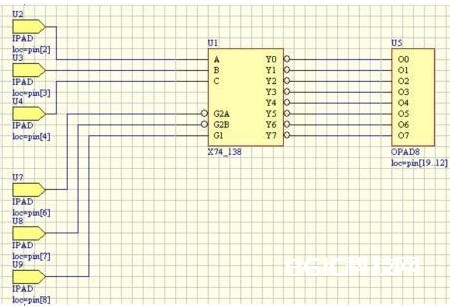

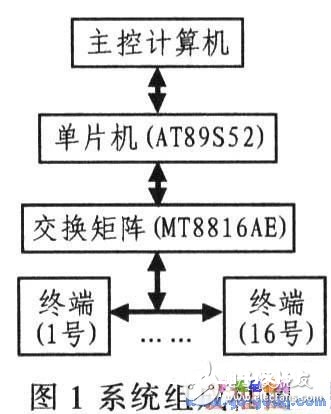

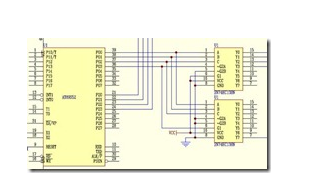

基于AT89S52和MT8816AE的音频控制系统组成和电路设计-MT8816AE内含一个8×16的开关阵列,并具有7~128条线路的译码器和锁存器。选择7个适当的地址位,即可对矩阵开关的任意一位进行寻址。在该器件的DATA输入端加1或0.可使选中的开关开启或关闭。STROBE为锁存信号,器件选择(CS)信号可使开关阵列相互串接,以扩大矩阵的容限。

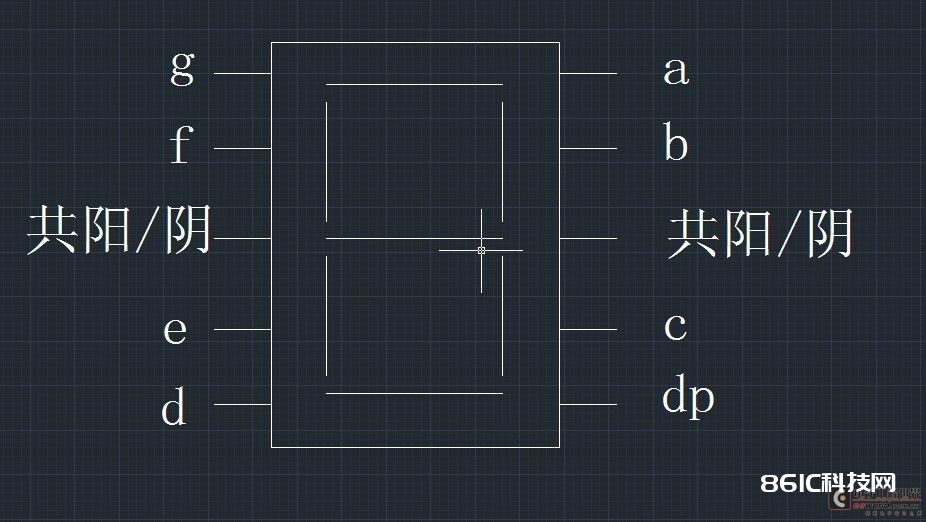

51单片机对8位数码管依次显示0-7的设计-共阳极数组0~9:display[]={0xC0,0xF9,0xA4,0xB0,0x91,0xA2,0x82,0xF8,0x80,0x90}

共阳极数组A~F:display[]={0x88,0x83,0xA6,0xC1,0x86,0x8E}

共阴极数组0~9:display[]={0x3F,0x06,0x5B,0x4F,0x6E,0x6D,0x7D,0x07,0x7F,0x6F}

共阴极数组A~F:display[]={0x77,0x7C,0x59,0x3E,0x79,0x71}

共阴、两组四位一体数码管,位选接74LS138译码器,输入(位选)CBA接P20,P21,P22。段选通过74573后接P1口。

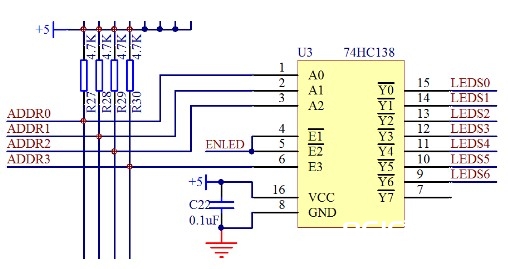

单片机74HC138三八译码器的原理及应用方法-从这个名字来分析,三八译码器,就是把3种输入状态翻译成8种输出状态。从图3-15所能看出来的,74HC138 有1~6一共是6个输入引脚,但是其中4、5、6这三个引脚是使能引脚。使能引脚和我们前边讲 74HC245 的 OE 引脚是一样的,这三个引脚如果不符合规定的输入要求,Y0 到 Y7 不管你输入的1、2、3引脚是什么电平状态,总是高电平。

AT89S52单片机对LED点阵显示屏的控制设计-LED 点阵显示屏是由20 个8*8 的LED 点阵块组成,形成16*80 矩形点阵,以Atmel 公司的AT89S52单片机为控制核心。显示屏的其他主要硬件有:①带锁存输出的8位移位寄存器74HC595,作为LED的列线驱动输入;②三八译码器74LS138,作为LED行线的译码选择;③三极管C9012,连接两个三八译码器的十六个输出端,作为开关使用,驱动LED的行线。

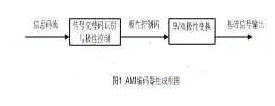

基于FPGA器件实现AMI编码器和译码器的设计-实际的基带传输系统,含有丰富直流和低频成分的基带信号不适宜在信道中传输。而对具有易获取定时信息、无直流成分和只有很小的低频成分、以及具有内在纠错能力的信号才适宜在基带传输系统中传输。AMI码、HDB3码均具有这些特点,因而广泛应用。

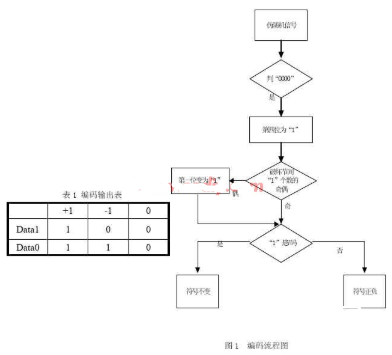

基于VHDL语言和可编程逻辑器件实现HDB3编译码器的设计-由于VHDL不能处理负电平,只能面向“1”、“0”两种状态,所以要对它的输出进行编码,如表1所示。编码的实现是根据HDB3编码原理把二进制码编码成两路单极性的码字输出,之后经过单双变换模块形成HDB3码。在编码过程中,要经过连0检测、破坏节判断、破坏节间“1”的个数判断、调整“1”的符号输出等步骤,编码部分可分为4个模块,编码流程如图1所示。

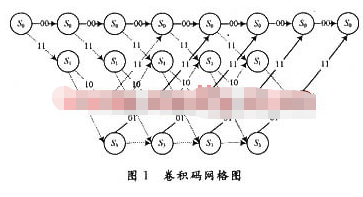

采用可编程逻辑器件的译码器优化实现方案-由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。