STM32单片机的5个时钟源解析-1. STM32的5个时钟源

a。高速内部时钟 HSI,大约为8MHz

b。高速外部时钟 HSE,晶振取值范围在4M–16M,一般采用8M晶振

c。低速外部时钟 LSE,32.768k晶振,可以作为RTC的时钟源

d。低速内部时钟 LSI,大约为40KHz

e。PLL锁相环时钟

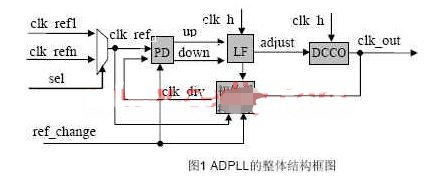

基于可编辑逻辑器件实现ADPLL的应用设计-随着数字电路技术的发展,特别FPGA技术的普遍应用,采用FPGA实现全数字锁相环(ADPLL)的应用越来越多。ADPLL设计简单、应用方便。本文介绍一种采用FPGA实现的ADPLL,该ADPLL用于产生SDH设备的外同步输出时钟。该锁相环具备传统的APLL的俘获时间短、有稳定的相差的优点,同时也具备DPLL的中心频点可编程调整、能够实现平滑源切换的优点。

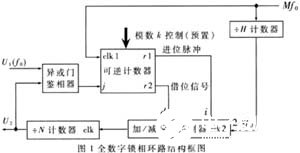

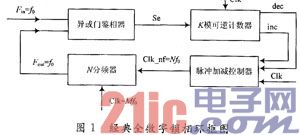

采用Spartan2系列FPGA器件实现全数字锁相环路的设计和仿真验证-数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。传统的全数字锁相环路(DPLL)是由中、小规模TTL集成电路构成。这类DPLL工作频率低,可靠性较差。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去,实现所谓片上系统SOC(System on a chip)。因此,可以把全数字锁相环路作为一个功能模块嵌入SOC,构成片内锁相环。下面介绍采用VHDL技术设计DPLL的一种方案。

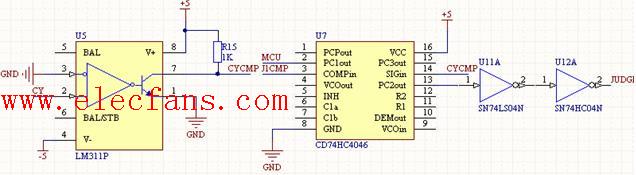

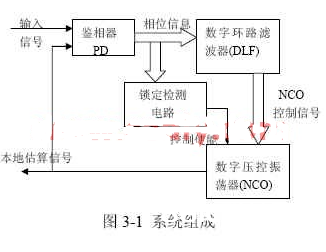

基于EPM7128SCL84-7芯片和quartus 2软件实现低频信号的锁相技术-在现代数字通信中, 数据传输,时钟校时等问题中很重要的一个方面是信号的同步。而同步系统中的核心技术就是锁相环。通常商用的全数字锁相环(DPLL)的关键部件是电荷泵和数字延迟线。电荷泵将数字鉴相器得到的相位差信息以电荷的方式累积起来,并根据积累的电荷量控制数字延迟线的反馈环,从而获得相应的本地估算时钟。即使是微小的相位差,也会导致电荷泵的电荷的累积。因此,这种技术实现的锁相环可以达到很高的同步精度。

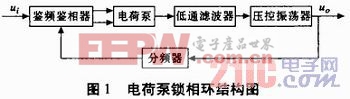

摘要:环路滤波器是锁相环中的一个关键模块,对宽带高压VCO进行调谐时,常采用有源滤波器。在论述了电荷泵锁相环基本原理的基础上,对有源环路滤波器的结构以及滤波器对锁相环性能的影响进行了分析,推导出有源环

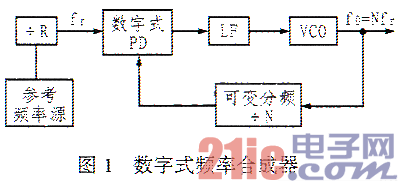

摘要:LMX2332是美国国家半导体公司生产的集成数字锁相环(PLL)电路。文章介绍了利用单片机AT89C2051控制数字锁相环LMX2332及压控振荡器JTOS-150实现低噪声频率源的方法,该方法

1 引 言锁相技术在信号处理、调制解调、时钟同步、倍频、频率综合等领域都得到了广泛的应用。目前锁相技术的实现主要有模拟锁相环(APLL)、全数字锁相环(DPLL)、模拟数字混合锁相环与延迟锁相环(DL

1 引 言频率合成技术迄今已经历了三代:直接频率合成技术、锁相环频率合成技术、直接数字式频率合成技术。直接数字式频率合成(Direct Digital Frequency Synthesis,DDFS