0 导言

现在,液晶显现职业得到敏捷的开展,但由于液晶模块的出产不或许到达100%的成品率,或多或少地存在缺点,现在在TFT模块的出产工艺中就有或许发生点缺点和线缺点等。为了及早对产品的质量进行检测,液晶测验仪器成为一切的液晶模块出产厂家的必备设备。针对此问题,规划了能够快速查看TFT模块的点缺点和线缺点的简易测验仪器,该测验仪首要应用于中小尺度TFT LCD模块的快速检测。测验仪最首要的部分是为模块供给测验信号的信号源。

1 TFT驱动测验原理

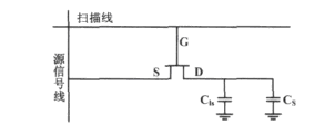

TFTLCD最或许发生缺点的方位是在电路层,即TFT阵列层。TFT实践功用好像一个开关,液晶好像一个电容,当开关闭合的时分,显现信号写入液晶电容Cls,断开的时分信号坚持在液晶上。存储电容Cs的作用便是让充电电压坚持到下一次更新画面。图1是单一TFT等效电路图。扫描线操控TFT的栅极,来决议TFT是否选通,源信号线衔接TFT的源极对液晶电容进行充电。当加在G极和S极的电压Vgs大于阈值电压Vth时,源极和漏极导通,液晶电容充电,到达显现作用;当Vgs小于阈值电压Vth的时分,TFT开关断开,液晶电容坚持充电电压到下一扫描周期。

图1 单一TFT等效电路图

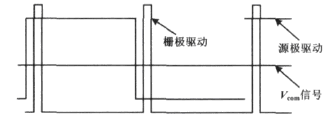

若液晶分子长期固定在某个电压下不变,会损坏液晶分子的旋转特性。当显现要求同一灰度的时分,可将显现电压相关于Vcom分红相同压差的正负极性,这样不管是加在液晶上的电压是正仍是负,尽管液晶分子的旋转方向不同,但显现的灰度是相同的。当要求显现同一灰度的时分,通过正负电压的替换,到达显现要求,也可防止对液晶分子的损坏。现在,为了防止闪耀现象和削减功耗,大多数TFT LCD选用点翻转固定Vcom电压的驱动方法。选用固定Vcom电压方法的时分要注意馈通电压的影响。关于固定Vcom电压的驱动方法,馈通电压的构成首要来源于栅极驱动信号的改变,此改变经存储电容Cs和栅极与漏极之间的寄生电容Cgd反应到显现电极上,影响显现电极电压正确性。为防止此影响,需求批改Vcom电压,使之对馈通电压有所补偿。图2是一般TFT模块选用的二阶驱动原理示意图。

图2 二阶驱动原理

2 TFT点缺点和线缺点发生机理

依据

3 测验信号的要求

为了满意对不同中小尺度TFT模块的测验要求,测验信号源一般供给源极信号、栅极信号、栅极操控信号和公共地信号。栅极操控信号一般是直流信号, 0~25V可接连调理,此信号一般接模块的GG端(此端为测验选通使能);栅极信号幅值-15~25V能够接连调理,频率10~100Hz可变,占空比1/1 000~1/2可调,此信号接TFT的栅极;源极信号幅值±0.5V~±5V可调,频率与栅极信号相同,占空比能够调理,此信号与栅极信号比较有一个滞后时刻,但高电平时刻要比栅极信号坚持时刻长,而且具有16级灰度的改变;地信号是为液晶屏供给的一个公共端。

4 测验信号的发生规划

为完成对TFT LCD的测验,就要完成上述的信号。其间栅极操控信号和公共地信号很简单完成,在此不作介绍。栅极和源极信号首要通过FPGA来完成。本文中首要介绍完成要求的频率和占空比,以及对灰度的操控。栅极信号的发生首要在FPGA中通过对给定的时钟进行分频计数的方法完成,此信号作为外部模仿开关MAX4622的选通信号,对MAX4622的两路输入信号进行选通。MAX4622的输入信号的幅值能够调理,别离在-5~0V和0~10V之间调理,MAX4622的输出信号经电路扩大后作为输出,即可满意栅极信号的要求[3]。栅极信号在FPGA中的构成进程如下:依据接收到的所要完成的频率和占空比的数值,通过公式计算出输入FPGA的数值,规则fclk为输入时钟频率,要完成的频率为freq,占空比为duty,则有:

N =fclk/(freq×duty)

FPGA依据N对时钟脉冲分频计数,分为偶数和奇数的两种状况,N为偶数时比较简单完成,当N为奇数时,需求设置两个分频器,别离对时钟脉冲的上升和下降沿计数,再将这两个成果作逻辑或处理,即可得到成果为(freq×duty)的方波脉冲,再对其进行值为duty的不等分频处理,所得到的便是频率和占空比满意要求的成果。图3是仿真成果,其间m为所要完成的频率freq,n为占空比, temp2为频率为freq×duty的方波信号, clk_gate便是终究的栅极信号。其间时钟clk为2MHz,m为10Hz,n为1/20。

图3 栅极信号

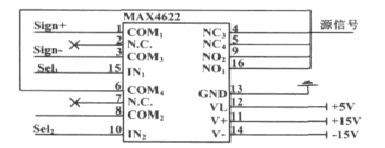

源极信号是通过16路模仿开关AD7506和模仿开关MAX4622发生的。AD7506是16选1的模仿转换开关,通过4位地址输入值挑选1路输出。AD7506的16路输入将+5V16等分,每路通过不同的电压值代表不同的灰度等级。其挑选信号也是由FPGA发生的,完成16选1的输出。该输出通过正向跟和顺反向扩大电路作为另一个MAX4622的一组开关(COM1和COM3)的输入,由FPGA发生的选通信号Sel1,操控正向电压或反向电压的输出,此输出和公共地又作为MAX4622另一组开关(COM2和COM4)的输入,经Sel2选通,就可得到具有16个不同正负幅值和脉冲宽度均可调的信号,此信号通过运放电路的扩大即为所要求的源极信号。其间详细的完成电路如图4所示。

图4 源极信号的发生电路图

其间Sel1是栅极信号通过D触发器而构成的,所以具有必定的滞后。Sel2是栅极信号通过FPGA内部的一个单稳态触发器而完成的, FPGA构成的单稳态触发器由两个D触发器和一个计数器组成,其间cp为上述的(freq×duty)方波,tr为栅极信号, Sel2即为输出信号,其高电平的时刻能够依据实践需求在必定范围内随意设定,如图5所示。这样,代表不同灰度等级的交变信号就可加在TFT的源极点