1 规划摘要

FPGA芯片具有高速并行核算的特色。跟着摩尔定律的开展,核算科学现已步入并行化的年代,具有并行处理才能的CPU/GPU随即问世。而FPGA芯片凭仗其并行核算的才能,现已能够轻松将科学核算、逻辑运算、ASIC规划等使用并行化。咱们以电子竞技裁判为切入点,将该特性普及化、使用于日子运动范畴。本规划在每个竞走运发动的鞋子上都装置加快度传感器,在竞走进程中,将收集到的加快度数据经过射频发送给依据FPGA芯片规划的电子裁判,把杂乱的算法、数据处理交给FPGA芯片完结,让电子裁判进行判别。这样,在数十名运发动进行竞走练习的时分,并不需要别的组织裁判员而精确测出犯规问题。大大地减轻人力资源以及从根本上提高了竞走练习的功率和灵敏性,是FPGA并行化使用的一次全新测验。

2 体系原理与技能特色

依据竞走比赛规则:

- 一个竞走运发动有必要一向坚持有一向脚落在地上上。

- 从行进脚落地的一刻起直到腿部到达笔直的姿态,腿部有必要坚持直线,膝盖不能曲折。

咱们把集成了加快传感器、射频收发器等专用芯片的运动鞋节点装置在每只专用练习鞋上,并将它固定在脚跟方位。那样,在竞走时,假如两只脚一起离地,两只脚的加快传感器都会捕获到一个一起向前的加快度。别的,由所以腾空,在竖直方向上的加快度,会和坚持脚落在地上是不同的。因而,经过剖析x、y、z三个方向的加快度数学模型,咱们能够从中判别是否呈现违规现象。

而咱们的电子裁判体系是以依据FPGA芯片为根底,经过CC2500射频收发器无线接纳每个运发动练习进程中传递过来的加快度。FPGA芯片收到一切运发动的采样数据后,调用相应的片内模块算法进行判别核算,依托其并行化的特色,能够将每个运发动的数据处理并行化。假如有违规现象,能够经过亮灯或许喇叭鸣叫作出警示。最终乃至能够再将核算成果经过PCI Express总线或有线网络回来给PC机。以便利数据存储或进一步的数据剖析,以监控每个运动的练习情况。

体系的技能特色有以下几点:

(1)彻底的电子监控裁判体系,能够扫除人为因素的忽略错判漏判。并且在练习进程中不需要别的再组织人手,以愈加灵敏高效有弹性的组织练习时刻和进程;

(2)使用FPGA的高速并行特性,可完结多种同类型核算的并行化,因而满意多运发动练习的一起监控,并快速作出判别;

3 体系软件流程

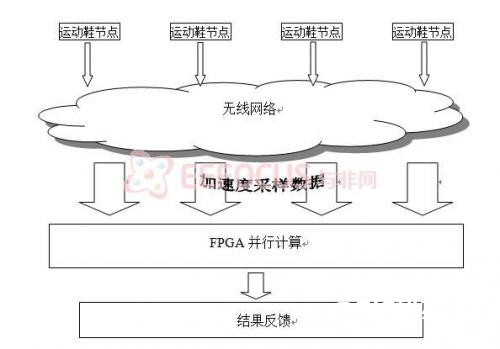

图 1 多节点数据判别的软件流程

上图所示为多节点回传采样数据并调用并行核算的进程,运动鞋节点与FPGA芯片的通讯经过无线网络来完结。FPGA芯片依据接纳到的采样数据、调用判别算法来判别违规现象并进行警示。

4 体系结构

图 2 体系结构

上图所示为体系的组成结构。运动鞋节点主要有加快传感器的驱动程序,射频收发器的驱动程序;FPGA端主要有无线网络接口、犯规判别算法的Verilog HDL模块。

5 体系功用

5.1 运动鞋节点功用

(1)读写加快传感器数据

(2)无线发送采样数据

(3)反常处理

5.2 FPGA电子裁判功用

(1)接纳网络数据

(2)依据采样数据调用判别算法,进行运发动违规辨认

(3)对违规现象实施示警

(4)将核算模块回应的核算成果,经过PCI Express总线接口或有线网络将数据回送给PC

5.3 FPGA PCI Express总线接口IP核功用

(1)经过PCI Express总线读写数据

5.4 PC机数据优化模块功用

(1)依据具体的使用要求参加不同的优化算法模块

6 体系具体规划

6.1 运动鞋节点的规划

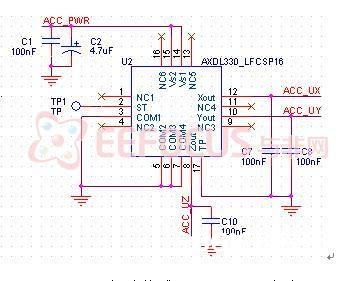

咱们的运动鞋节点是以MSP430单片机为中心,并衔接外部芯片加快传感器ADXL330。咱们经过MSP430内部的ADC数模转化模块获得该ADXL330芯片的加快度数据。

图3 加快传感器ADXL330电路图

6.2 CC2500无线网络的规划

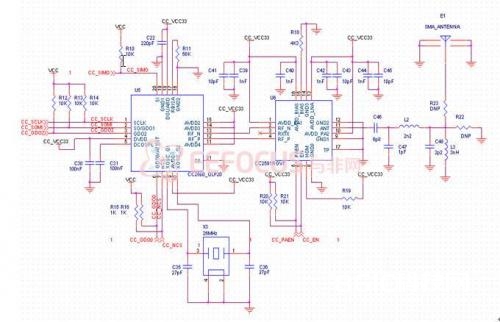

MSP430经过CC2500和CC2591彼此协同作业,将从ADXL330读取的加快度数据经过无线网络传回给FPGA电子裁判作出判别。

6.3 FPGA电子裁判的规划

相同,在电子裁判端,咱们用MSP430单片机和CC2500、CC2591芯片,接纳无线网络传送过来的加快度数据,并经过串口与FPGA相连。但从串口的传输速度来看,经过串口传输是一个瓶颈。所以咱们计划做一个有多点串口的FPGA板,每个串口衔接一个MSP430,而每一个MSP430担任接纳一部分的运动鞋节点的数据。

而在FPGA板上,咱们写一个驱动,将串口数据存入自定义buffer里。这儿的自定义buffer,是由VHDL言语写的锁存器组合而成。最终的FPGA判别算法模块,便是读取一切锁存器的数据,进行快速并行核算,得出违规成果。

6.4 FPGA端的PCI控制器模块规划

图5 PCI设备结构图