接连时刻Σ-Δ调制器(Continuous-Time ΔΣ Modulator)先天上具有对输入信号滤波的作用,可下降前级滤波器规划复杂度,并提高信号质量,因此成为如今无线通信体系接纳机(Receiver)规划的常用计划。

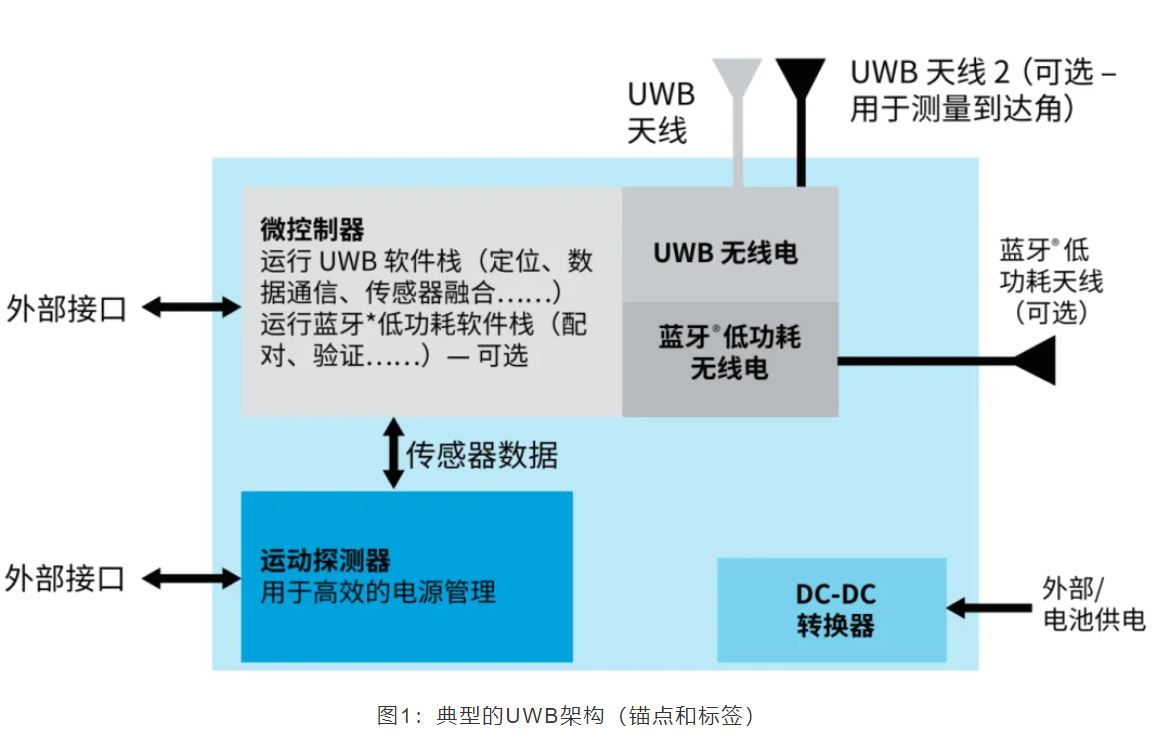

无线技能现在已广泛运用于人类的日子中,低功率无线收发器(Ultra-Low-Power Wireless Transceiver)更是无线通信电路开展的重要关键。现在接纳(Receiver)中的模仿数字转化器(ADC)遍及提出的架构,皆以低通Σ-Δ调制器(Low-pass Delta-Sigma Modulator)为主(图1),信号通过带通滤波器(BPF)、低噪声扩大器(LNA),再经由混频器(Mixer)做降频的动作,接着在基带(Baseband)做数字化处理。

图1 传统接纳器架构图

Σ-Δ模仿数字转化器(Delta-Sigma Analog-to-Digital Converter)一直以来是一个能够得到高分辨率(Resolution)的电路架构,其间接连时刻Σ-Δ调制器(Continuous-Time Delta-Sigma Modulator, CTDSM)因先天上具有对输入信号滤波的作用,使前级滤波器在规划需求上能够比较宽松,因此CTDSM成为在规划接纳机时,常被运用的要素之一。当然此类的ADC规划上有许多当地需求留意,如今仍有许多文献在这个范畴有不少着墨,以致力于低功耗、宽带的CTDSM规划。

本文首要分红两大部分,榜首部分为过采样ADC的根本运作原理介绍,第二部分则针对如今文献在CTDSM所提出的技能,做一些简略的介绍。

采样/量化影响ADC信号精确

ADC的运作进程首要分为采样(Sampling)和量化(Quantization)两大过程。采样的动作是将接连信号转为离散的数据,在此进程中,势必会遇到两个问题,榜首是怎么确认取得的成果为所需求的信号;第二是要多快的采样频率才够精确。

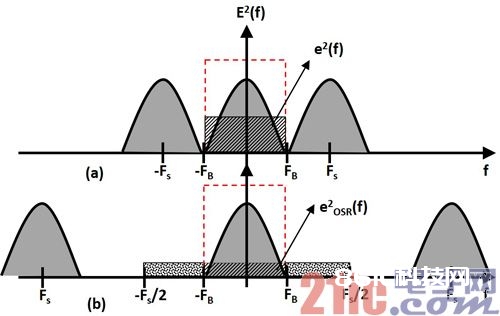

由频率图(图2)的成果能够发现,榜首,为了保证采样信号确实是咱们要的,一般会先通过抗混叠滤波器(Anti-Alias Filter)来过滤不要的信号;第二,通过采样后,若信号带宽超越fs/2的话,那数据会相互重迭导致失真发生,好像尼奎斯特原则(Nyqusit-Sample-Theorem)中所述,采样频率至少有必要大于两倍数据带宽。

图2 采样频谱图

量化的动作是将接连的振幅转为离散数值,而量化中发生的差错会影响精确度(图3(a)),假定输入的信号为一个三角波(Ramp Signal),则量化差错会出现锯齿波(图3(b)),并散布在±0.5Δ内(表明Δ量化阶的差值);假如输入没有构成超负荷(Overload),则量化差错能够视为一个均匀散布的函数,其机率密度函数ρ(e)如图4所示,其均匀值(Mean Value)为0,量化差错的功率等于其变异值(Variance),可表明为:

图3 (a)3位的搬运函数、虚线为三角波输入,(b)对应之量化差错

图4 量化差错的机率密度函数

……公式1

接着为了求ADC的信噪比(SNR),必需求知道信号的功率。若输入一个弦波到一个输出为N个位的ADC,在转化器未达超负荷的前提下,输入弦波的最大振幅为A,则A满意:

……公式2

所以输入的功率能够表明为:

……公式3

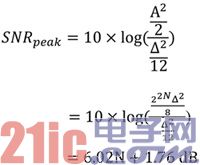

因此SNR的最大值能够表明为:

……公式4

根据上述公式,每增加一个位能够增加6dB,所以关于一个高分辨率的ADC,则实际上需求一个N位的输出,这在实作大将难以到达,因此后来提出过采样(Oversampling)的办法来改进这个问题。

调配噪声整形 过采样可削减差错

上述在ADC满意采样频率为信号带宽两倍的,归于尼奎斯特型(Nyquist Rate) ADC(图5(a))。过采样的意思便是采样频率大于两倍的带宽,这时候能够界说一个参数是过采样份额(Over-Sampling-Ratio, OSR)为:

1)>

图5 (a)量化差错功率散布(OSR=1),(b)量化差错功率散布(OSR>1)

(FB为信号的带宽)……………………….公式5

假定量化差错为白噪声(White Noise),即它的功率为均匀地散布在Fs/2之间(图6(b)),则它的功率谱密度(Power-Spectral-Density)为:

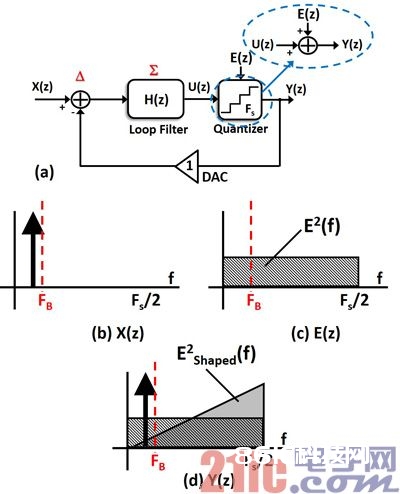

图6 (a)三角积分器示意图;(b)输入X(z)频谱图;(c)量化差错E(z)频谱图;(d)输出Y(z)频谱图

……公式6

则于信号带宽(FB)内的总量化差错功率PNoise,OSR为:

……公式7

因此SNROSR的最大值能够表明为:

……公式8

由上述公式能够知道,固定信号带宽下,每两倍OSR(即Fs两倍)仅增加3dB(0.5个位)。由成果能够发现,仅增加OSR所取得的优点并不大,因此一般会进一步合作噪声整形(Noise-Shaping)的技巧。

Σ-Δ调制器改进量化差错

三角积分器自身即一起选用过采样及噪声整形两项技巧,噪声整形即运用相减(Delta, Δ)和积分(Sigma, Σ)组合而成(图6(a))。则量化差错E(z)所通过的搬运函数(Noise-Transfer-Function, NTF)为:

……公式9

则输入信号X(z)所通过的搬运函数(Signal-Transfer-Function, STF)为:

…..公式10

由上面两个公式能够发现,当挑选H(z)为一个高直流增益的低通滤波器时,噪声搬运函数则为一个高通滤波器函数,代表原本为白噪声散布的量化噪声E(z)会通过高通滤波器塑型;而信号搬运函数则为一个低通滤波器函数,代表在低频时,输入信号X(z)通过增益为一的输入搬运函数到输出。而一起由于选用过采样,所以信号带宽相关于采样频率小许多,即大部分的量化差错都被塑型到信号带宽(FB)外面,所以带宽内的量化差错被大幅度的削减。

因此,调制器的输出Y(z)包括输入信号即通过塑型的量化差错ESHAPE(z)(图6(b)(c)(d))。最终根据环路滤波器(Loop-Filter)为离散型H(z)或接连型H(s),可分为接连型或离散型Σ-Δ调制器。一个环路滤波器阶数为L的Σ-Δ调制器,其SNRDSM的最大值能够表明为:

……公式11

由上面公式能够知道,固定信号带宽下,每两倍OSR能够增加(6L+3)dB,假定一个三阶的环路滤波器,则能够增加21dB,相关于只要做过采样,可多得到18dB(三个位)。

低功率CTDSM适用于无线通信体系

以下将针对接连型三角积分器中各个子区块做阐明。在过采样Σ-Δ调制器中,架构上能够分红两种办法,一种是离散时刻Σ-Δ调制器(Discrete-time Delta-sigma Modulator, DTDSM),另一种则是CTDSM。由于架构先天上的优势,CTDSM比起DTDSM更适用于高速、宽带的运用;可是跟着带宽需求的增加,采样频率(Fs)也会跟着增加,随同而来的便是更高的功率耗费,首要能够分几个部分来阐明。

首要,由于带宽的增加,使得用来完结CTDSM中环路滤波器的运算扩大电路,需求更高的单位增益带宽(Unit Gain Bandwidth),这样的需求也一起伴跟着更高的功率耗费;另一方面,由于用于CTDSM中的量化器,是操作在采样频率的速度,因此跟着采样频率的增加,也会使得量化器为了到达速度的需求,需求耗费更多的电流来压低运算时刻。

在高标准的CTDSM中,为了增加回授途径上之数字模仿转化器(Digital to Analog Converter, DAC)的线性度,常会运用数据加权均匀(Data Weighted Averaging, DWA)的办法,来下降DAC中各个单位Cell之间不匹配所构成的Harmonic Tone。

再者,由于整个CTDSM是一个负反馈的闭回路体系,这使得每一笔从量化器输出的数据,都需求在小于一个、乃至是半个采样周期的时刻回授到CTDSM的输入,体系才会安稳,也便是整个信号途径包括环路滤波器、量化器以及DWA所奉献的推迟,需求压在半个周期(0.5/Fs)内完结。

当环路滤波器以及量化器都会奉献必定程度上的推迟时,DWA电路就需求操作在更高的速度,使其所奉献的推迟更小,坚持CTDSM体系的安稳,可是更高速的操作,就代表需求更多的功率耗费。

最终,便是推迟回路(Excess Loop Delay, ELD)的补偿。由于整个闭回路体系上的电路所奉献的推迟时刻,相较于采样频率是不行疏忽的,因此这样额定的推迟等效上便是在体系上增加额定的极点,使得体系安稳度下降。

为了补偿这个不抱负性,高速的CTDSM一般需求额定的补偿途径,使体系能够正常的操作,而这个额定的补偿途径一般需求额定的DAC乃至是额定的运算扩大器来完结信号相加减的运算,这都使得高速CTDSM比起低速的CTDSM,须耗费更多的硬件以及功耗。

可是,假如期望在CTDSM运用于无线通信体系中,功耗就有必要压低,根据这样的需求,有许多技能被提出来下降CTDSM中各部分的功率耗费。

根本上CTDSM体系架构能够简略分为几个电路区块,首要的电路区块包括环路滤波器、DAC、量化器(Quantizer)和DWA(图7)。

图7 CTDSM根本架构

Gm-C/VCO/Twin-T下降环路滤波器功耗

一般在CTDSM中,假如期望压低量化差错,其间一个办法便是增加环路滤波器的阶数,阶数越高,对带宽内量化差错的压抑作用就越好,可是随同而来的便是要选用更多的运算扩大器来完结积分电路,以到达所需环路滤波器的方程式。

一般积分器的完结都是选用Active-RC架构,环路滤波器的阶数多增加一阶,就需求多增加一个Active-RC电路来完结积分电路;再者,用于Active-RC电路中的运算扩大器是归于闭回路运用(Active-RC中的C,一般衔接于运算扩大器的输入与输出,构成负回授),所以此运算扩大器的单位增益带宽必需是采样频率的两到三倍,体系才会安稳。

根据这个考虑,有些高速的运用,就会恰当的引进Gm-C架构来完结积分电路,由于Gm-C电路中,Gm的完结是归于开回路的完结办法(Gm的输入与输出点之间并无回授途径),因此关于用来完结Gm电路的单位增益带宽之需求就比较低,也就使得Gm-C的架构能够运用比较少的功耗,完结出相同的环路滤波器转化方程式。

可是,Gm-C的架构由于是开回路架构,所以比起Active-RC的架构,线性度较差,Gm-C架构所奉献的电路噪声也较Active-RC大。因此,Gm-C电路一般只能替代环路滤波器中部分的积分器;而在CTDSM中信号摆伏比较大的当地或是CTDSM的输入端,这些对线性度以及信杂比要求较高,一般仍是会选用Active-RC的架构。

Gm-C的架构比起Active-RC架构还有一个缺陷,一般Active-RC架构由于是负回授架构,所以会有虚短路(Virtual Short)点能够将输入信号以及回授信号做相加减;可是,因Gm-C电路比较归于开回路架构,并没有显着的虚短路点能够做信号相加减,因此在环路滤波器架构的选取上,比重用Active-RC的办法完结,就会比较受限。

另一方面,为了提高环路滤波器的阶数,一起期望到达低功耗,有些计划会恰当的引进电压操控式振动器(VCO)电路,以一起到达一阶积分作用以及量化的功用。正由于VCO这项将两者功用合而为一的特性,因此能够有用地下降功率耗费。

至于为什么VCO就能够将积分和量化两项功用合而为一,首要是由于VCO在时域上的操作是根据输入电压的不同。VCO电路会振动在不同的频率,而频率的积分会是相位,因此,只要用一个具有固定相位的信号,和VCO的输出信号做比较,就能够得到VCO在一个采样周期内的相位改变量。等效上便是得到对输入信号积分一个周期后的改变量,这样不光能够使得输入电压由于通过VCO的联系有积分作用,而且输入电压由于VCO也会对应到相位信息。

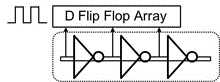

透过和固定相位的参阅频率做比较(一般通过简略的D Flip-Flop就能够完结以及固定频率的频率),能够得到相位是抢先或是落后的信息。而得到量化往后的成果,也便是说藉由VCO电路,能够一起完结积分以及量化运算,亦即把积分器以及量化器合而为一,到达下降功耗的方针。

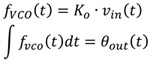

由以下VCO简略的公式推导,能够了解到VCO电路在频域上,确实具有一阶积分的作用:

……公式12

Ko:振动频率的增益

fVCO:VCO的振动频率

out:VCO的输出相位

Vin:VCO的输入电压(操控电压)

此运用的VCO电路一般运用环形振动器(Ring Oscillator)(图8),由于环形振动器能够供给多相位,也便是能够将相位的改变量,区分为更多的状况,等效出多位(多位)量化器的作用,压抑量化差错。可是,由于是选用环形振动器,压控环形振动器的线性调变规模很小,因此假如规划欠好,很简略发生额定的Harmonic Tone,这是此一架构的缺陷。

图8 多级环形振动电路

此外,还有别的一种办法,便是引进双T型滤波器(Twin-T Filter)(图9)。此种滤波器的特性便是能够只运用一颗运算扩大器,合作特别规划过的电阻、%&&&&&%网络,即可得到二阶的积分作用;换句话说,便是T型滤波器的架构能够只运用一颗运算扩大器,就能完结出原先需求两个Active-RC积分器才干完结的体系方程式。

图9 双T型滤波器

很显着的,这个办法能够有用下降运算扩大器的运用数量,等效上便是下降环路滤波器的硬件以及功耗。可是这样的办法一般由于只用到一颗运算扩大器,就能够完结两阶积分的方程式,比起原先运用两个独立积分器来完结相同的体系方程式,虚短路的点比较少,而使得在体系参数的设系上,会比较受限。规划自由度会比运用两颗独自的运算扩大器还低。

归纳上述各种架构做一个简略的定论,一般最常见完结环路滤波器的办法是Active-RC架构,可是为了更进一步下降功耗,所以有许多计划会选用Gm-C、VCO-Based、Twin-T等办法完结环路滤波器。图10对环路滤波器的完结办法做了一些简略的定论。

图10 环路滤波器的各种完结办法

DWA处理消除DAC非线性

差错

回授途径上的DAC,假如是运用多位DAC,则DAC的非线性会约束了CTDSM的信号噪声失真比(Signal to Noise and Distortion Ratio, SNDR)。DAC的非线性差错能够被视为一个除了电路噪声以外,额定增加的噪声源,此噪声正是由于DAC中各个子电路(Unit Cell)之间的不匹配。要处理这个问题,最直接的办法便是选用单位元的DAC架构(1Bit DAC),由于只要一个位,就没有所谓不匹配的问题。

可是选用单位元DAC又会衍生其他问题,例如单位元DAC体系中的积分器相较于多位会比较难规划;一起,单位元DAC也对时序信号颤动(Clock Jitter)此一非抱负效应更灵敏。假如想要运用多位DAC,可是又想要消除非线性度对CTDSM的影响,最常被运用的办法,便是将DAC的输入数字码做恰当的处理,也便是所谓DWA的处理。

处理的算法根本方向,便是让不同的DAC Cells均匀地被运用。正由于每个DAC Cells都被均匀的运用,所以DAC Cells之间的不匹配效应就会遭到必定程度的压抑,而使得全体CTDSM能够有更高标准的体现。

一般来说,做这样的信号处理,必需求比及量化器的输出都现已安稳,才干够做进一步的运算。量化器输出通过处理后才会被送到DAC的输入,因此此一电路在回授途径上,也会奉献额定的时刻推迟,使体系简略振动,所以在估量整个CTDSM的体系安稳度时,需求将此一电路所奉献的推迟恰当地考虑进去。

在DAC电路上,最适合用于高速的架构莫过于电流扶引(Current Steering)。DAC规划上,最大的问题除了线性度以外(一般会合作DWA电路加以处理),别的便是电路热噪声的问题。现在面临电路噪声问题,最好的处理办法便是拉高DAC电源电压,使热噪声能够下降,此外鲜少有比较好的处理办法。

本篇文章分为首要两个部分,在榜首部分,介绍了DSM根本的架构以及操作原理,包括过采样(Oversampling)、噪声整形(Noise Shaping)等概念;第二部分则是更进一步介绍了CTDSM各部分子区块的电路架构,包括环路滤波器、量化器、DWA电路以及ADC。针对各个部分,本文亦介绍了许多如今常被运用的技能以及其优缺陷。